東芝、ミリ秒オーダーで大規模な「組み合わせ最適化問題」を計算する技術を2019年中に適用実験 金融分野などに期待

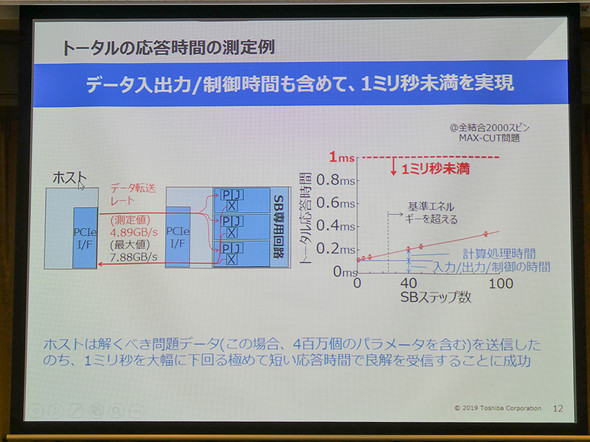

東芝は9月11日、組み合わせ最適化問題を大規模かつ高速に解ける「シミュレーテッド分岐アルゴリズム」(SB)を、FPGAなどの専用回路に実装する設計技術を発表した。同技術でSBを実装したFPGAでは、入力から出力を返すまでにかかる時間は1ミリ秒未満だという。実用的な問題を解く実証実験を行い、今年中の成果発表を目指すとしている。

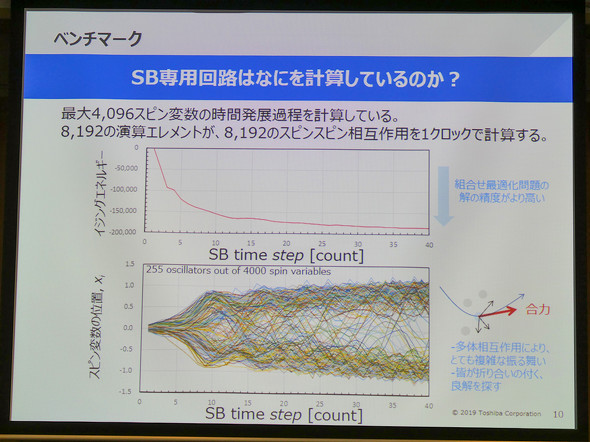

シミュレーテッド分岐アルゴリズムは、東芝が4月に発表した組み合わせ最適化問題を近似的に解くアルゴリズム。組み合わせ最適化問題を表す「イジングモデル」を、既存のアルゴリズムを実装した従来のコンピュータや組み合わせ最適化問題に特化した量子コンピュータより、高速かつ大規模に解けるとしている。

今回発表したのは、FPGAやASICなどにSBアルゴリズムを効率的に実装するためのソフトウェア言語(高位合成言語)による記述方法。これにより計算の規模や並列度、データの粒度などを回路へ設計できるという。

同技術でSBアルゴリズムを20ナノメートルプロセスルールのFPGAに実装すると、4096変数・全結合までの問題サイズを扱えるマシンができあがる。同マシンでは入力を得てから、0.2ミリ〜1ミリ秒で問題の近似解を出力できるという。

SBアルゴリズムのハードウェア実装に当たった東芝の辰村光介主任研究員は「これほど大規模な問題に対して瞬時に応答するシステムは例がない。新しい可能性を示せるのではないか」と話す。

大規模かつ高速・超低遅延で解を出せることに加え、省電力性などにも優れるとしており、金融分野の自動取引の最適化などに活用を見込む。

適用分野は明らかにしていないが、19年中に特定分野の問題に対し同マシンの実証実験を行い、成果を発表したいとしている。

関連記事

「量子理論の副産物に過ぎなかった」──東芝の「量子コンピュータより速いアルゴリズム」誕生秘話

「量子理論の副産物に過ぎなかった」──東芝の「量子コンピュータより速いアルゴリズム」誕生秘話

量子コンピュータよりも速い「シミュレーテッド分岐アルゴリズム」を開発した後藤隼人主任研究員に、開発背景を聞いた。 「世界最速・最大規模」──東芝、量子コンピュータより高速に組み合わせ最適化問題を計算するアルゴリズムを開発

「世界最速・最大規模」──東芝、量子コンピュータより高速に組み合わせ最適化問題を計算するアルゴリズムを開発

東芝が、組み合わせ最適化問題を従来のコンピュータで、量子コンピュータより高速に解けるアルゴリズムを開発した。同アルゴリズムを活用したサービスプラットフォームの19年中の事業化を目指す。 日立、GPUで組み合わせ最適化を大規模・高速に計算する「モメンタム・アニーリング」を発表 10万変数・全結合問題を1秒未満で計算

日立、GPUで組み合わせ最適化を大規模・高速に計算する「モメンタム・アニーリング」を発表 10万変数・全結合問題を1秒未満で計算

日立製作所は、組み合わせ最適化問題を高速に計算できるアルゴリズム「モメンタム・アニーリング」を発表した。NVIDIAのGPU4台で実装したところ、「10万変数・全結合」という大規模な問題の近似解を1秒未満で計算できたという。 東芝の「組み合わせ最適化最速アルゴリズム」、クラウドで一般公開

東芝の「組み合わせ最適化最速アルゴリズム」、クラウドで一般公開

東芝は、組み合わせ最適化問題を高速・大規模に解ける「シミュレーテッド分岐アルゴリズム」を実装したマシンを、クラウド上に公開した。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

Special

PR