PCのスケーラビリティを決定付けた超重要コンポーネント、地味にスゴイ「APIC」の登場:“PC”あるいは“Personal Computer”と呼ばれるもの、その変遷を辿る(2/2 ページ)

本題に戻る。

IBM PC/ATではこれで良かったが、AT互換機がどんどん進化するにつれ、不都合も出てきた。最大のものはマルチプロセッサに対応できないことだ。

SMP、つまり対称型マルチプロセッサ構成の場合、OS Kernelはどれか1つのプロセッサの上でのみ稼働し、ドライバも当然そのプロセッサで動く。こうしたケースでは、IRQの信号はそのOS Kernelが動くプロセッサにだけ渡されないといけない。他のプロセッサが受け取っても、そのIRQをハンドリングするロジックはそのプロセッサ上に存在しないからだ。

これはIntel 8259の欠点といえば欠点なのだろうが、そもそもマルチプロセッサ構成を考慮しない、シングルプロセッサ向けIPCなのだから仕方がない。

PCベースのマルチプロセッサシステムは、Compaqが1989年に投入したSystemProが多分最初(Zenith Data SystemのZ-1000とどっちが先か微妙だが、多分Compaqが先と思われる)である。

Compaq SystemProはDual Intel386、Zenith Data System Z-1000は最大構成で80386×6という壮絶な構成であるが、どちらのシステムもPICに関しては独自実装されており、このためOSはCompaqなりZenith Data Systemなりが提供するものしか動作しなかった(SystemProはSCO UNIX、Z-1000はSCO Xenixがそれぞれ提供されたが、汎用品ではなくそれぞれのシステム向けのスペシャル版である)。

こうした独自インプリメントを何とかしないと、PC市場が広がらないことになる(当時Intelは、サーバマーケットまでx86を何とかして売りたいといろいろ画策していた)。実装としては、特定のCPUにだけ割り込みが掛かるという、「一見対称型に見えて、実は非対称なマルチプロセッサ」という方法もなくはない(そういう実装も存在する)が。

また、これはIntel 8259というよりもIBM PCとの互換性に絡む話だが、IBM PCではIRQ2が予約とされつつ、実際にはXT Busにつながっていた。ところがIBM PC/ATではこれがSlave PICにつながっているため、互換性維持のためにIRQ9が呼び出されたらIRQ2の割り込みルーティンを起動することにしたのだが、今度はIRQ9が使えなくなるという面倒な話になった。

Intel 8259はLevel Triggerできないのもネックであった。I/O Busで割り込み線のハンドリングには、Edge Trigger(信号のOn/Offのタイミングで割り込みを通知する)とLevel Trigger(信号の電圧レベルで割り込みを通知する)の2種類の方法もある。どちらが便利かといえばLevel Triggerの方で、複数のデバイスからの割り込みをまとめてハンドリングできる。

このためPCIではLevel Triggerを採用しているのだが、XTやISA、VL-BusなどはEdge Triggerだけ(EISAはLevel TriggerとEdge Triggerの両対応だが、現実問題としてLevel Triggerはほとんど使われなかった)という問題もあった。

時系列的にはAPICが出た後でPCIの策定作業が始まっているから、PCIの存在がAPICの登場を促した訳ではないのだが、おそらくIntel社内では8259の制約が将来のバスに影響を与えるであろうことは理解しており、それゆえ先取りする形で仕様を盛り込んだのだと思う。

前置きが長くなったが、そんなわけで1989年にIntel 486DXと併せて導入されたのがAPICである。主な特徴は、

- これまでシステムに1つだけだったPICを、各CPUごとに用意されるLocal APIC(LAPIC)と、I/Oデバイス側の管理をまとめて行うIO APICの2種類に分離し、これを専用レーンで接続する構造にした

- Intel 8259互換モードを実装し、後方互換性を確保

- マルチプロセッサ環境に対応、さらにプロセッサ間の割り込み(IPI:Inter-Processor Interrupt)にも対応

- SMP/AMP環境でのさまざまな割り込みニーズに対応

といった点が挙げられる。

最初に実装されたのはIntel 486DX向けに用意されたIntel 83489DXであるが、これはまだLAPICとIO APICが1つのパッケージに収められる格好になっており(写真5)、見た目にはそれまでAT互換機で搭載されていたIntel 8259×2を1つに収めたようになっている。

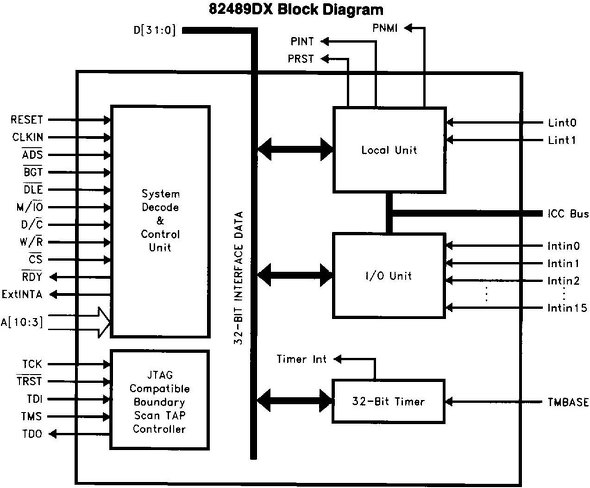

写真5:“Intel 82489DX Advance Interrupt Controller Datasheet”より抜粋。Local Unit(LAPIC)とI/O Unit(IO APIC)が内部I/Fで接続される構造になっているのが分かる。IRQは16本に拡充されている

写真5:“Intel 82489DX Advance Interrupt Controller Datasheet”より抜粋。Local Unit(LAPIC)とI/O Unit(IO APIC)が内部I/Fで接続される構造になっているのが分かる。IRQは16本に拡充されている互換モードで動いている限りにおいては、従来のIntel 8259と同じ制約が掛かることになる。ただこの後、APICにOSがネイティブ対応するようになると、8259ベースでは不可能だったマルチプロセッサや1つのIRQで複数の割り込みハンドリングといった機能が利用できるようになった。

マルチプロセッサを当初から考慮したWindows NT 3.1やOS/2 2.1などでは、APICが使える場合にはAPICを使うようにインプリメントが行われるなど、大々的にアナウンスされたわけではないが確実にAPICが広まっていった。

このAPICをベースにMPS(Multi-Processor Specification)と呼ばれる、x86ベースでマルチプロセッサ環境を構築するための仕様(写真6)も1993年にIntelからリリースされている。

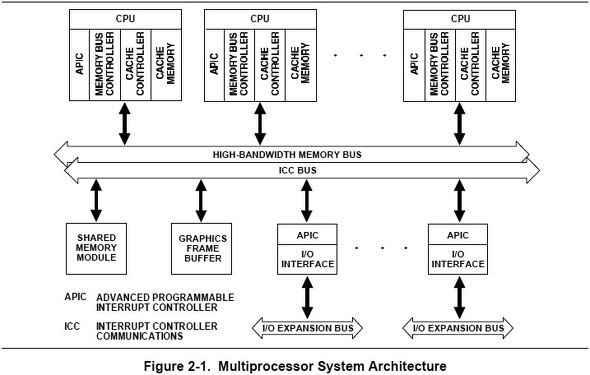

写真6:“MultiProcessor Specification”より抜粋。ICC(Interrupt Controller Communication)Busと呼ばれる、LAPICとIO APICをつなぐバスが出ているのが分かる

写真6:“MultiProcessor Specification”より抜粋。ICC(Interrupt Controller Communication)Busと呼ばれる、LAPICとIO APICをつなぐバスが出ているのが分かるこれはIntel 486やPentiumをベースにマルチプロセッサを構築する際の標準的な仕様をまとめたもので、これに基づく形でベンダーはサーバ向けのマルチプロセッサシステムの構築が可能になった。

APIC自身も進化している。LAPICはPentiumの第2世代(P54)からCPU側に内蔵されるようになり、一方IO APICはチップセット側に集約されるようになった。

さらにPentium 4の世代からx2 APICという新しい仕様が登場している。このx2 APICは、例えばProcessor IDが8bitから32bitに増やされたことで、255個までだった最大プロセッサ個数が約43億(2^32-1)個に増える、APICレジスタへのアクセス方法が改善されるなど、多くの改良がなされている。

PCIではMessage Signalled Interrupts(MSI)という機能が実装されたが、これもIO APICの存在を前提に行われているなど、APICの搭載はPCがシングルプロセッサの小規模システムから、大規模なマルチプロセッサシステムまで発展できるようになるための、重要な出来事であった。

関連記事

Modern PCの礎、PCIはどう生まれ、いかに成立していったか

Modern PCの礎、PCIはどう生まれ、いかに成立していったか

USBが誕生したのは「奥さんのプリンタをつなげる手間にキレたから」 USBの設計当時を振り返る

USBが誕生したのは「奥さんのプリンタをつなげる手間にキレたから」 USBの設計当時を振り返る

今回は、USBこそがPCであることの条件を規定しているというお話。 Intelが生み出したさまざまなPC標準規格 Microsoftとの協力と対立

Intelが生み出したさまざまなPC標準規格 Microsoftとの協力と対立

そろそろ皆さんに馴染みの深い規格が登場してきた。ここまでくると、Wintelの時代である。

Copyright © ITmedia, Inc. All Rights Reserved.

Special

PR