Intelがメモリ標準化で主導権を失うに至った“やらかし”について:“PC”あるいは“Personal Computer”と呼ばれるもの、その変遷を辿る(2/3 ページ)

これに続いて登場したのがSDRAM(Synchronous DRAM)である。ちょっと想像できないかもしれないが、EDO DRAMの時代まで、メモリのアクセスは信号線の制御をns単位で設定していた。

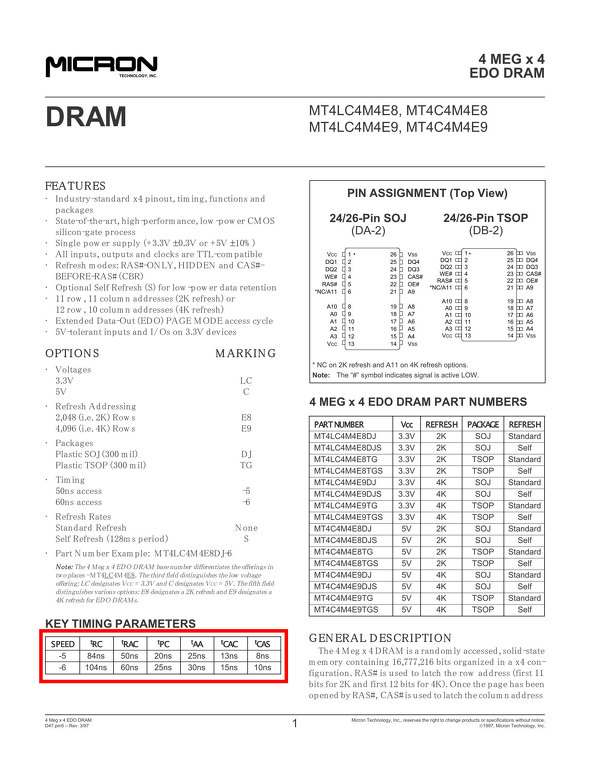

写真1はMicronのMT4LC4M4E8/9という16Mbit EDO DRAMチップのデータシートの表紙ページだが、左下にKey Timing Parametersとしていくつかの時間が示されている。

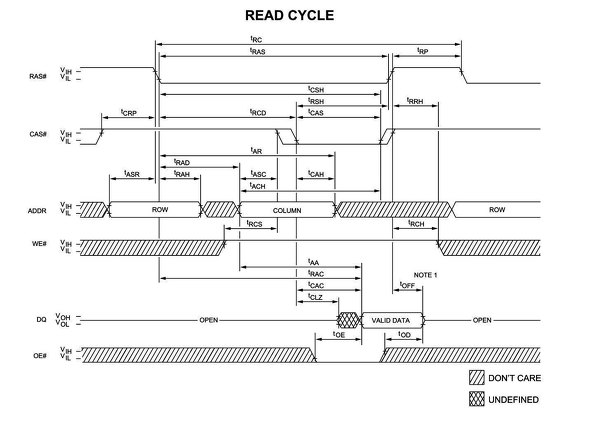

この時間の意味は、例えばRead Cycle(写真2)を見ると分かりやすい。

DRAMのアクセスにあたっては、基本的にRAS(Row Addressの制御)、CAS(Column Addressの制御)、WE(Write Enable:書き込みか読み込みか)、OE(Output Enable:出力するか否か)の4つの制御線を経由してDRAMに指示を与え、ついでにADDR(アドレス線)にRowとColumnの2つのアドレスを載せることで、DQ(Data In/Out)経由でデータを読み取ったり書き込んだりとなるのだが、それぞれの制御線のON/OFFのタイミングとアドレスを載せるタイミング、それとデータ入出力のタイミングが、先ほどの赤枠に示したパラメーターで決められているわけだ。

ちなみにこれはあくまでも主要なタイミングであって、実際にはタイミングパラメーターが20以上存在しており、これを細かくハードウェアで制御する必要があった。なかなかしんどいとはいえ、慣れればディスクリート部品でこのタイミングを作ることも不可能ではない(実際筆者もディスクリートIC+PALでDRAMメモリコントローラーを作ったことがある)。

ただこれ、高速化しようとするといろいろパラメーターが多くて大変である。そこでコントローラー側からクロック信号を与え、これに同期する形でアクセスできるようにしよう、というのがSDRAMである。これにより、これまでns単位で制御していたメモリのパラメーターがClock単位になり、ずっと制御が容易になった。また新たにコマンド線が追加され、DRAMの制御を信号線ベースではなく、コマンドの形で指示できるようになったのも大きい。

Intelでいえば1997年の430TX(これはPentium向け)と440LX(Pentium Pro/Pentium II向け)でこのSDRAMに対応した。ちなみに440LXはPC-66という66MHz動作のSDRAMにのみ対応したが、翌1998年にはPC-100という100MHz動作のSDRAMに対応した440BXが登場している。

Copyright © ITmedia, Inc. All Rights Reserved.

Special

PR