ITmedia NEWS >

企業・業界動向 >

Intelなど半導体大手、Google、Meta、Microsoftがチップレット推進で新標準「UCIe」のコンソーシアム結成

» 2022年03月03日 09時15分 公開

[ITmedia]

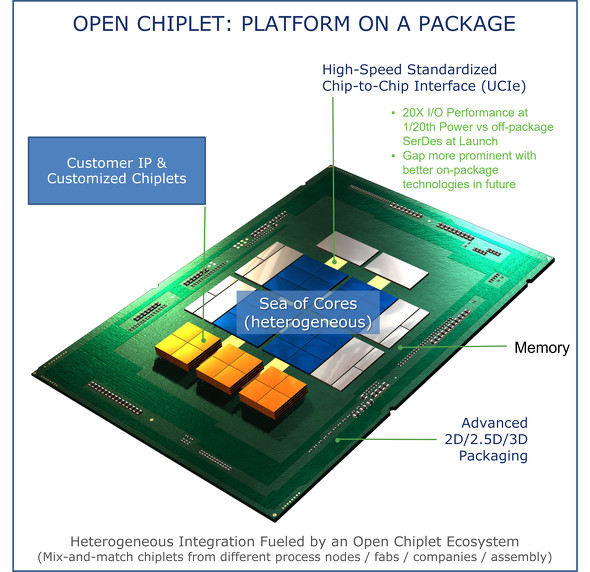

IntelやAMDなど半導体大手、Google、Meta、Microsoftなどは3月2日(米国時間)、半導体設計でチップレットエコシステムを確立するための新たな技術「Universal Chiplet Interconnect Express」(UCIe)を発表した。

参加するのは、Advanced Semiconductor Engineering(ASE)、AMD、Arm、Google Cloud、Intel、Meta、Microsoft、Qualcomm、Samsung、TSMC(アルファベット順)。

チップレットは、2018年ごろから注目されているSoC作成方法。従来の統合モノリシックチップは、SoCのすべてのパーツを単一のシリコンに統合する。それに対し、チップレットはCPUやGPUなどのパーツを小さなコンポーネントに分割し、それを組み合わせてSoCにする。メリットは、多様な組み合わせが可能になることや、モノリシック設計よりも大きなチップの作成が可能になることなどだ。AMDは最近のRyzenシリーズなどでチップレットを採用している。

UCIeでは、まずはチップレットをより広範なパッケージに相互接続させるためのルール確立に重点を置く。将来的には「チップレットフォームファクター、管理、セキュリティ、その他の重要なプロトコル」を含む次世代UCIe技術の標準を策定するとしている。

関連記事

ソフトバンクG、ArmのNVIDIAへの約4兆円売却を断念 再上場へ

ソフトバンクG、ArmのNVIDIAへの約4兆円売却を断念 再上場へ

ソフトバンクGはArmのNVIDIAへの売却断念を正式に発表した。この取引には英、米、EUが懸念を表明していた。ソフトバンクGはArmの再上場の計画も発表した。 Apple Silicon移行主導者がIntelに出戻り(3回目)

Apple Silicon移行主導者がIntelに出戻り(3回目)

AppleのApple Siliconへの移行を主導したジェフ・ウィルコックス氏がIntelに戻りDesign Engineering GroupのCTOに就任した。 AMD、EPYC搭載サーバ開発でMeta(旧Facebook)と提携

AMD、EPYC搭載サーバ開発でMeta(旧Facebook)と提携

AMDは、Meta(旧Facebook)がサーバプロセッサ「EPYC」を採用したと発表。リサ・スーCEOはオンラインイベントで第3世代EPYCを披露し、このプロセッサ搭載のシングルソケットサーバの開発でMetaと協力したと語った。 Google、初オリジナルモバイルSoC「Google Tensor」発表 「Pixel 6」に搭載

Google、初オリジナルモバイルSoC「Google Tensor」発表 「Pixel 6」に搭載

Googleが次期フラグシップ「Pixel 6/6 Pro」を発表した。オリジナルのSoC「Google Tensor」を搭載する。Gogole Tensroは、4年を費やしてTPUのチップをモバイルに最適化したSoCだ。- ムーアの法則 次なるけん引役は「チップレット」 〜IEDM2020に見る先端パッケージ技術

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

Special

PRアイティメディアからのお知らせ

SpecialPR

あなたにおすすめの記事PR