最終回:RISC-Vエコシステムの発展 Arm、NVIDIAとの関係はどうなるのか?:RISCの生い立ちからRISC-Vまでの遠い道のり(2/3 ページ)

RISC-Vの組織作り

この時点における研究プロジェクトとしてのRISC-Vは、主に軍関係(DoE Isis Project、DARPA PERFECT program、DARPA POEM program)からの資金援助が多いが、他にC-FAR(STARnet Center for Future Architectures)やLBNL(Lawrence Berkeley National Laboratory)といった政府の研究所からの支援、更に業界スポンサーとして米Intel、Google、Microsoft、NVIDIA、Oracle、フィンランドのNokia、中国Huawei、韓国LG、Samsung、そして日本のNECなどの各社もRISC-V研究プロジェクトに資金提供をしている。こうしたスポンサーには当然RISC-Vに関する動向レポートなども届いているわけで、結果このうち何社かはRISC-V Foundationの創立メンバーに加わることになった。

さて、この2015年はRISC-V Teamと、特にアサノビッチ教授には忙しい年だったと思われる。

まず、RISC-V Foundationが8月5日に立ち上げられた。もっともこの時点では「質問は(Executive Director)のリック・オコナーにメールしてくれ」と書いてあるだけという、とりあえず組織が立ち上げられた「だけ」の状況である。

そして、ほぼ同じ頃にSiFiveも創業される。創業メンバーはアサノビッチ教授の他、RISC-V Teamの中核メンバーだったユンサップ・リー氏(CTO)とアンドリュー・ウォーターマン氏(Chief Engineer)の合計3人である。

ここはRISC-Vベースの商用IPを提供する会社であり、ちょうどデビッド・A・パターソン教授が立ち上げた初代MIPS(MIPS Computer)のような格好である。もっとも年末の時点でもトップページはこんな感じであったが(写真6)。

さらに8月23日から開催されたHot Chips 27では、そのユンサップ・リー氏がRocket Scalar CoreとHwacha Vector Acceleratorを組み合わせた「RAVEN-3」の詳細の発表を行っている(PDFへのリンク)。ワークショップを開催したり命令セットの仕様策定を進めたりしながら、さらにこうした作業と並行して、これまでUC Berkleyで行っていたRISC-Vに関するさまざまな取り組みをRISC-V Foundationに移管するという作業までもが水面下で行われていた。この頃のアサノビッチ教授は、体が4つか5つ欲しいほどに忙しかったのではないかと思う。

2016年はこうした取り組みが、形になり始めた年である。まずSiFiveに関しては、「Freedom E31」という最初の商用シリコンとこれを搭載した「HiFive 1」という評価ボードが完成して発売を開始。また最初のCEOとしてSutter Hill VenturesのManaging Directorであったステファン・ダイカーホフ氏を迎え、社員数を増やすと共にベンチャーからの出資を増やし、かつ手掛ける製品も増やしていくという拡大期に入る。

RISC-V Foundationの発展

これと並行してRISC-V Foundationも急速に形を整えていった。FoundationはPlatinum、Gold、Silver、Auditor、Individualという5段階のメンバーから構成されることになった(のは良いのだが、Member DirectoryをみるとMember Ship LevelがFounding、Platinum、Gold、Silver、Auditorになっているのが謎)。2016年末におけるPlatinum MemberにはBAR(Berkeley Architecture Research)、bluespec、Cortus、Draper、Google、HPE、Huawei、IBM、Mellanox Technologies、Micron、Microsemi、Microsoft、NVIDIA、NXP、Oracle、Qualcomm、Rambus、SiFive、Western Digitalという錚々(そうそう)たるメンバーが集まった。

この当時はAMDまでGold Memberとして加盟していたというのも面白い(写真7)。

写真7:ちなみにAMDはRISC-V Internationalに改編の前後で脱退した模様。今も加盟していたら面白いことになったのに、と思わなくもない(入ろうと思えばすぐ入れるだろうが)。赤丸は筆者が追加した

写真7:ちなみにAMDはRISC-V Internationalに改編の前後で脱退した模様。今も加盟していたら面白いことになったのに、と思わなくもない(入ろうと思えばすぐ入れるだろうが)。赤丸は筆者が追加した2017年には取締役会のメンバーも集まった。もっともこの当時はまだ取締役会(会長はアサノビッチ教授)の下にExective Managerのリック・オコナー氏とCommunity Managerのスー・レイニンガー氏しかいない状態で、なので事実上取締役会がFoundationの指揮を執るような形になっていた。まぁ立ち上げ間もない組織では良くある話ではある。ただこうした状況の中でも、例えば命令セットに関するTechnical Working Groupの結成に向けた話し合いなどは進んでおり、2018年あたりからこれが本格化していく。

もう一つ大きな動きは、本格的なエコシステム構築に向けた、特にソフトウェアや開発ツールチェーン関連の動きが活発になってきたことだ。元々UC Berkeleyの時代から、最低限のソフトウェア開発環境は用意されていた。早い時期にGCCを始めとするツールチェーンは用意されたし、Linuxもかなり早い時期にブートしている。ただこれは最小限という話であって、これで十分かと問われると、全然十分ではなかった。

ところがRISC-V Foundationには少なからぬ開発ツールチェーン提供ベンダーが参加した。ソフトウェア開発ツールではIAR SystemとかLauterbackやSeggerなどが、SoCの開発ツールとしてはImperasとかUltraSoC、Cadence、Mentor Graphicsなどが、いずれもSilver Memberながら加盟しており、こうしたベンダーは社内でRISC-Vの対応プロジェクトをスタートすることになる。

また、CortusやAndes Technology、CEVA、VeriSiliconなどこれまでProcessor IP(CEVAはDSP IPだが)を提供してきたベンダーは、従来Processor IPに併せて統合ソフトウェア開発環境(IDE)も提供してきていた。こうしたベンダーは、自社の独自ISAベースの製品からRISC-Vベースに切り替えるにあたり、IDEもまたRISC-V対応を図ることになったため、図らずしもソフトウェア開発環境が充実するというメリットも生まれた。

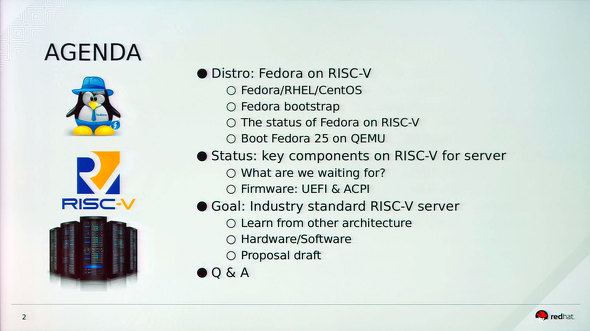

ソフトウェアベンダーもまた、RISC-V Foundationに参加し始めた。RedHatが正式に加盟したのは2019年のことだが、2017年に開催されたRISC-V Day TokyoではRedHatのウェイ・フー氏より、“RISC-V PC/server OS Development Status and proposal”と題した講演が行われている(写真8)。

写真8:既にこの時点でRV64に対応したBootstrapでFedora 27が起動しているという。ただしPCやサーバに持っていくためには、まずUEFIに対応したファームウェアがないし、ACPIもないし、とまだまだやるべきことがたくさん残っているとしていた

写真8:既にこの時点でRV64に対応したBootstrapでFedora 27が起動しているという。ただしPCやサーバに持っていくためには、まずUEFIに対応したファームウェアがないし、ACPIもないし、とまだまだやるべきことがたくさん残っているとしていた他にも、例えば現在はSilicon Labs傘下になったMicriumは、2017年にMicrosemi(というか、Microchip)が「Mi-V」というFPGA上で動くRISC-V環境の提供を発表したのに合わせ、同社の「Micrium μC/OS」のRISC-V対応を表明しているし、これよりはちょっと遅れたが2019年にはAmazonも「FreeRTOS」もRISC-Vへの対応を表明している。RISC-Vの最初のターゲットが、ASIC/ASSP向けのコアおよび一部の組み込み向けシステムということを考えると、出だしとしては悪くない状況である。

Copyright © ITmedia, Inc. All Rights Reserved.

Special

PR