第3回 Coreマイクロアーキテクチャ に迫る[後編]:新約・見てわかる パソコン解体新書(3/4 ページ)

アドバンスド・スマート・キャッシュ

インテルが言う5つのイノベーションのうちの1つ、アドバンスド・スマート・キャッシュは、デュアルコアに最適化したキャッシュシステムです。

Pentium DとCore 2 Duoのキャッシュ構造を次の図に示します。

Pentium Dでは、2つのCPUコアがそれぞれ自分専用のL1キャッシュとL2キャッシュを備えていました。両方のコアが、メインメモリの同じアドレスのデータをキャッシュ内に保持している場合、その両データのコヒーレンシ(一貫性)を保つための工夫が必要です。片方のコアがキャッシュ内のデータを書き換えた場合、もう片方のコアのデータも同じ値に更新しなければならないのです。このときデータは、Pentium Dでは下図左のようなルートを通ります。1つのパッケージの中に封入されたコア同士であるにもかかわらず、いったん外部バスとMCHを経由するのです。当然、処理に時間がかかります。

Core 2 Duoは、両コアが1つの大容量L2キャッシュを共有するため、片方のコアがL2キャッシュ内のデータを更新すれば、もう片方のコアにとっても自動的にデータが更新されます。L1キャッシュは独立しているので、それぞれのコアのL1キャッシュ内のデータを更新する必要はありますが、これはコア内部のことなので高速に処理できます。

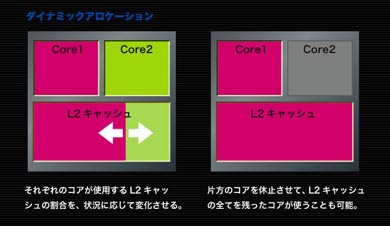

Core 2 DuoのL2キャッシュには、もう1つダイナミック・キャッシュ・アロケーションという機能があります。2つのコアの共有L2キャッシュの占有率を、各コアのメモリアクセスの規模に応じて変えるのです。片方のコアが、L2キャッシュの全てを占有することも可能です。

スマート・メモリー・アクセス

メモリとキャッシュに関するもう1つのイノベーションが、このスマート・メモリー・アクセスです。

基本的に、CPUのスピードに比べてメモリの反応速度は遅く、CPUがメモリにアクセスしてから実際にデータが読み出されるまでにはレイテンシと呼ばれる待ち時間が発生します。そのほか、CPUの都合でメモリへのアクセスが一時的にできなくなる場合もあります。いずれもCPUの処理速度を低下させる、重い足かせの1つです。そして、この足かせを軽くするのがスマート・メモリー・アクセスの狙いです。その名前の通り、賢いメモリアクセスを行う2つの技術からなっています。

1.メモリー・ディスアンビギュレーション

一言で言えば、メモリアクセス動作をアウトオブオーダー化するものです。

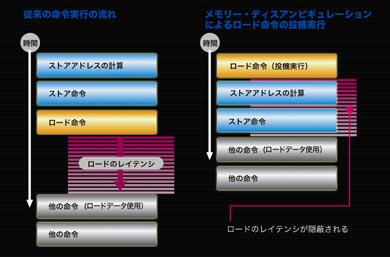

通常、プログラムの中で、メモリからデータを読み込むロード命令の後にメモリにデータを書き込むストア命令が続いている場合、先行するストア命令の処理が完了するまでは、後のロード命令を実行できません。ロードしようとしているメモリの内容を、先行するストア命令が書き換える可能性があるからです。ストア命令とロード命令がメモリの同じアドレスにアクセスする場合はそうなります。

しかし、ストア命令とロード命令がそれぞれ別のアドレスにアクセスする場合は、ストア命令の終了を待たずにロード命令を実行しても問題がありません。メモリー・ディスアンビギュレーションは、ストア命令の対象アドレスが決定する前に、後続するロード命令のアドレスと重なるかどうかを予測して、重ならない可能性が高い場合は、ストア命令の完了を待たずにロード命令を投機実行します。

インテルの情報によれば、典型的なプログラムでは約38% がメモリのストアおよびロード命令で構成されるということなので、これを少しでもアウトオブオーダーで実行できればCPUの実行効率は大きく改善するはずです。

2.IP ベースのプリフェッチャー

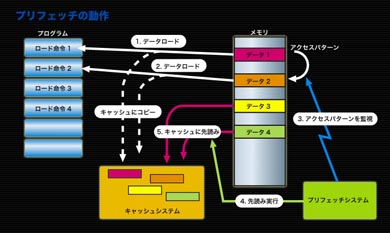

低速なメインメモリのレイテンシをカバーするためにCPUに内蔵されているのが、高速なSRAMで構成されたL1キャッシュおよびL2キャッシュです。CPUが一度メインメモリから読み出したプログラムの部分やデータを、キャッシュメモリにコピーしておき、次に同じプログラムの部分を実行したり、データを読むことになったときには、キャッシュメモリから素早く読み出すのです。

Coreマイクロアーキテクチャが持つIP ベースのプリフェッチャーとは、プログラムがメモリにアクセスするパターンを解析して、次にアクセスされそうなメモリの部分を予測し、そのアドレスのデータをメインメモリから投機的にプリフェッチ(先読み)して、キャッシュメモリに入れてしまうというものです。予測がヒットして、次にプログラムがそのアドレスのデータを読もうとしたときには、キャッシュメモリから素早く読み出すことができます。

メインメモリへのアクセスは、極端にCPUの実行効率を低下させるので、このプリフェッチが有効に働いてキャッシュメモリのヒット率が上がれば、かなりの効率アップが期待できるでしょう。

アドバンスド・デジタル・メディア・ブースト

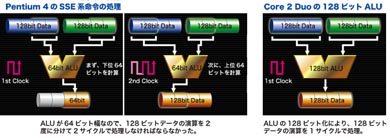

PentiumシリーズのCPUは、大量のデータを高速処理するのに適した拡張命令を持っています。この拡張命令は、SIMD(単命令複データ処理)型の処理を基本としていて、例えば合計128ビットの範囲内で、32ビットデータなら4組、16ビットデータなら8組のデータを、1命令で処理可能です。SIMD型拡張命令は、1997年発表のMMX Pentium以来、MMX、SSE、SSE2、Pentium 4のSSE3と進化してきました。しかし、SSE3命令を処理するためにPentium 4に与えられたマイクロアーキテクチャは、64ビット幅のALU(論理演算ユニット)を2度動かして128ビットの処理を行うというものでした。ですから1命令の処理に2クロックサイクルを必要とします。

Core 2 Duoには、SSE3に32個の命令を追加した、SSSE3という拡張命令が実装されています。そして、この命令を処理するALUは128ビット構成となっていて、128ビットデータを1クロックサイクルで一括処理することができます。静止や動画、あるいは音楽などのデジタルデータ処理の高速化が期待できます。

以上、いろいろな機能を紹介してきましたが、CPUに新しい機能を実装すると、それだけトランジスタの数が増加して、消費電力が増えます。機能の追加によって得られる性能向上率と、削減できる消費電力、増加する消費電力を計りにかけて、メリットがあるものだけがCoreマイクロアーキテクチャに採用されています。

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- OpenAIが「GPT-5.5」を発表/GeminiのチャットでWordやExcel、PDFファイルなどを生成可能に (2026年05月03日)

- バッテリー最大30日&64GBのストレージ! 究極のタフネスウォッチ「Amazfit T-Rex Ultra 2」は+3万円の価値があるか (2026年05月01日)

- 無刻印モデルが2万円! Amazon GWセールでPFUが「HHKB」シリーズを特別価格で放出中 (2026年05月02日)

- 大容量HDDは品薄前夜「見つけたら即買い」の危機? 連休狙い目の「MSI×AMD×Apacer」スペシャルパックを追う (2026年05月02日)

- Windows 11の不満解消へ Microsoftの最優先プロジェクト「Windows K2」とは何か (2026年04月28日)

- 静音性とカスタマイズ性を両立した有線メカニカルキーボード「Keychron C3 Pro」がセールで20%オフの7744円に (2026年04月30日)

- 4月30日発売の「Amazon Fire TV Stick HD(2026)」の特徴は? 購入時に注意すべきポイントをチェック! (2026年04月29日)

- コンパクトな高品質キーボード「ロジクール MX KEYS mini KX700GRd」が15%オフの1万3480円に (2026年04月30日)

- MicrosoftとOpenAIの「独占契約終了」が意味するもの──AI覇権を巡る両社のしたたかな戦略 (2026年05月01日)

- 手のひらサイズでAIが動く! 産業・ビジネスを支える最新「ミニPC」「GPUサーバ」展示レポート (2026年04月28日)