第3回 Coreマイクロアーキテクチャ に迫る[後編]:新約・見てわかる パソコン解体新書(1/4 ページ)

前回は、Pentium 4のマイクロアーキテクチャであるNetBurstを中心にお話しました。今回は、NetBurstに変わってインテルの主力CPUに採用されることになったCoreマイクロアーキテクチャを解説します。Core 2 Duoの性能と電力効率のよさの秘密に迫りましょう。

まずは簡単におさらいをしておきましょう。Pentium 4は、ひたすら動作クロックを高くすることで性能向上を狙ったCPUでした。31段という異常なほど長いパイプラインを採用することで、4GHz以上のクロックを狙いました。ところが、長いパイプラインは、分岐ミスがあったときのペナルティが重く、実際にアプリケーションプログラムを処理させたときに、期待したほどのスピードが出ないことがあります。また、高い周波数で駆動することで、消費電力が非常に高くなってしまいました。そこで、デュアルコア化によって高性能化を目指すPentium Dが登場したわけですが、今後さらにCPUの性能を向上させて行くには、Pentium 4のアーキテクチャを捨てて、新しいアーキテクチャのCPUを作る以外に道がありませんでした。そして生み出されたのが、インテルCoreマイクロアーキテクチャです。

インテルの狙いは、1クロックあたりの処理命令数(IPC)を多くすることにより、高クロックに頼らずに性能を向上させることと、消費電力あたりの性能を高くすることです。そのために、インテルの技術者はたくさんのアイデアを考え出し、Coreマイクロアーキテクチャに取り入れました。

例えて言えば、Coreマイクロアーキテクチャは、ターボ付きのエンジンのようなものです。小排気量のエンジンでも、ターボを付けて空気を圧縮してシリンダーに押し込むことで、大排気量のエンジンに負けないパワーを絞り出すことができることはよく知られています。しかも、加給さえ効いていれば、低回転からでも高いトルクを発生することができるのです。高回転まで引っぱらないと力が出ない自然吸気エンジンと大きく異なります。

それでは、Coreマイクロアーキテクチャにはどんなターボが付いているのか、見て行くことにしましょう。

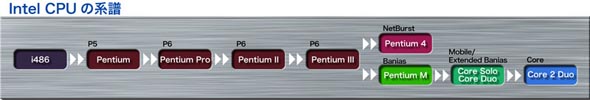

インテルCPUの系譜

Pentium 4の後継CPUとなるCore 2 Duoは、2006年7月に発表されました。すでにインテルは、2006年1月にCoreブランドを冠した初のCPUであるCore DuoおよびCore Soloを登場させていましたが、これはモバイルPC向けのCPUであり、やはりモバイル向けに作られたPentium Mの後継CPUという位置付けになります。

Core 2 Duoは、インテルCoreマイクロアーキテクチャというマイクロアーキテクチャを採用しています。同アーキテクチャは、Pentium Mのアーキテクチャをベースとし、さらに洗練させたものと言えます。

ちなみに、Pentium Mのアーキテクチャについては正式名はないようですが、俗にBaniasマイクロアーキテクチャと呼ばれています(BaniasはPentium Mの開発コード名)。また、Pentium Mを引き継いだCore Duo/Core Soloのアーキテクチャは、俗称としてMobileマイクロアーキテクチャまたはExtended Baniasマイクロアーキテクチャと呼ばれています。系譜としては次のようになります。

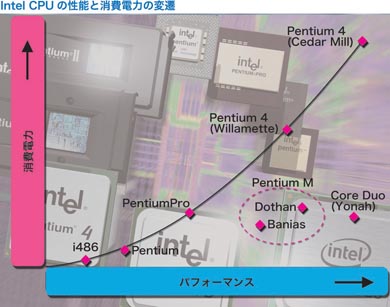

次のグラフは、i486からCore DuoまでのCPUの性能と消費電力をまとめたもので、インテルが公表しているものを描き直しています。Pentium 4の消費電力の高さと、Baniasマイクロアーキテクチャの効率のよさがよくわかるでしょう。Baniasマイクロアーキテクチャは、少ないパイプライン段数や、マイクロフュージョン、専用スタックエンジン(いずれも後述)などによって高いパフォーマンスと電力効率を実現しました。このグラフには、残念ながらCore 2 Duoのデータが含まれていませんが、Core Duoよりもパフォーマンスが高く、消費電力はやや高いといったところでしょう。

Pentium 4からCore 2 QuadまでのCPUの登場時期を下の表にまとめておきます。細かいことですが、Coreマイクロアーキテクチャを採用した初のCPUはサーバ/ワークステーション向けのXeon 5100であり、その発表はCore 2 Duoの登場より約1月早かったのです。

Coreマイクロアーキテクャの概要

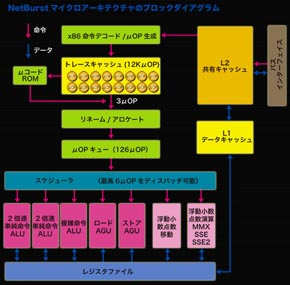

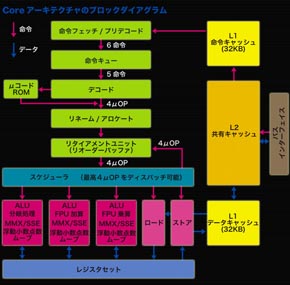

まずはNetBurstとCoreマイクロアーキテクチャのブロックダイアグラムを並べて示すので、しばらく眺めてください。

NetBurstについては前回も解説していますが、簡単にまとめると、x86命令をマイクロOPに変換してトレースキャッシュに蓄え、これを7個ある実行ユニットでアウトオブオーダーで実行します。トレースキャッシュがヒットし続け、分岐予測が当り続ける限りは高い性能を発揮しますが、それが外れたときには処理速度がガクンと落ちてしまいます。1クロックあたりの同時実行命令数は最大6マイクロOPですが、平均命令実行数は3マイクロOP程度と言われており、その効率の悪さも大きな問題です。

一方、Coreマイクロアーキテクチャはトレースキャッシュをやめて、毎回L1キャッシュからx86命令を読み込み、マイクロOPに変換して実行します。同時実行命令数は最大4マイクロOPで、NetBurstよりも低いのですが、平均命令実行数はNetBurstを上回るようです。この高効率の秘密は、ブロックダイアグラムからはうかがい知ることができません。

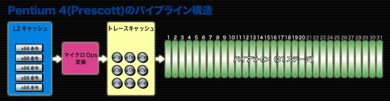

上で示したブロックダイアグラムの各ブロックは、実際には複数の回路に分割されていて、全体が長いパイプライン構造となっています。NetBurstのパイプライン構造を示します。

NetBurstを採用した最初のPentium 4(Willamette)のパイプラインは20段でしたが、第3世代のPentium 4であるPrescottコアでは高クロック化のために31ステージに細分化されています。また、x86命令をマイクロOPに変換する部分も、実際には数段のパイプライン構造となっています。トレースキャッシュのミスがあった場合は、L2キャッシュへのアクセスとマイクロOPへの変換処理が行われ、それが終わるまではパイプラインに命令が流れて行きません。また、分岐ミスが発生した場合にも、パイプラインがストールします。これらの影響で、NetBurstは平均命令実行数が期待するほど増えなかったのです。

NetBurstは、整備されたサーキットで好タイムを記録できるレーシングカーのようなものと言えるかもしれません。実際のアプリケーションソフトは、信号があったり路面が荒れたりしている一般道のようなもので、レーシングカーが速く走れるとは限らないのです。

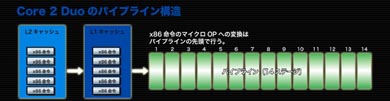

次に、Core 2 Duoのパイプラインを見てみましょう。

パイプラインは14段。Pentium 4の半分以下です。動作周波数は高くしにくくなりましたが、分岐予測が外れたときのペナルティは少なくなります。ちなみに、マイクロOP方式を採用した初のCPUであるPentium Pro(1995年発表)のパイプラインは12段でした。

トレースキャッシュ方式をやめたため、毎回x86命令をマイクロOPに変換しなければなりませんが、それによる速度低下は分岐予測が外れたときだけです。変換処理もパイプライン化されているからです。

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- マウスの概念が変わる! ロジクールG「PRO X2 SUPERSTRIKE」が切り開く“身体感覚”と直結する新たなクリック体験 (2026年02月18日)

- Googleが「Pixel 10a」発表 499ドルでフラッグシップ級のAI機能を搭載 AirDropや衛星SOSも対応 (2026年02月19日)

- 日本初の限定Echo Dotは「ドラえもん」! 価格はあえての「1万1293円」 (2026年02月19日)

- 最大3画面出力と100W給電に対応した「UGREEN 14-in-1 ドッキングステーション」がセールで1万3990円に (2026年02月18日)

- ChatGPT連携で文章の要約や下書きもこなす電子ペーパーノート「iFLYTEK AINOTE Air 2」がセールで6万799円 (2026年02月18日)

- 「UGREEN ワイヤレスHDMI送受信機」が25%オフの8999円に (2026年02月19日)

- 5層の吸音材で極上のキータッチを実現した75%キーボード「EPOMAKER x Aula F75」が25%オフの1万490円に (2026年02月18日)

- 「UGREEN Revodok USB-C ハブ 6in1」が2000円で買える (2026年02月17日)

- 中小企業のビジネスPC調達は絶対に新品であるべきか? コスパを最大化する“中古/新古品”という選択肢の是非 (2026年02月19日)

- 約10gのウェアラブルAIレコーダーや分離合体プロジェクターなど、Ankerが「Soundcore」を刷新 ロボット掃除機も定番モデルを強化 (2026年02月18日)