乽22僫僲乿偲乽3D僩儔僀僎乕僩乿偑杔偨偪傪岾偣偵偡傞棟桼丗偙傟偑Tick乬亄乭偩両乮1/2 儁乕僕乯

乬3D僩儔僀僎乕僩乭偭偰壗偑偦傫側偵偡偛偄偺偐

丂僀儞僥儖偼丄4寧24擔偵乽戞3悽戙僀儞僥儖 Core 僾儘僙僢僒乕丒僼傽儈儕乕乿傪敪昞偟偨丅偙偺CPU偼丄僀儞僥儖偑乽3D僩儔僀僎乕僩僩儔儞僕僗僞乿偲屇傇3師尦峔憿偺嵟怴僩儔儞僕僗僞媄弍傪嵦梡偡傞偙偲偱丄徣揹椡惈擻偲崅惈擻壔偺椉棫傪壜擻偵偟偰偄傞丅摨幮暃幮挿 寭 CTO偺僕儍僗僥傿儞丒儔僩僫乕巵偑乽3D僩儔僀僎乕僩僩儔儞僕僗僞媄弍偺妋棫偵傛傝丄CPU偺崅惈擻壔偲徣揹椡壔偺儁乕僗傪傛傝偄偭偦偆岦忋偱偒傞傛偆偵側傞乿偲岅傞傛偆偵丄敿摫懱偺旝嵶壔傪恑傔傞忋偱廳梫側栶妱傪壥偨偡媄弍偩丅

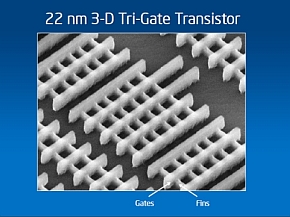

3D僩儔僀僎乕僩僩儔儞僕僗僞媄弍偺桪埵惈傪愢柧偡傞Intel 暃幮挿 寭 CTO偺僕儍僗僥傿儞丒儔僩僫乕巵乮幨恀亖嵍丄2011擭9寧偺IDF 2012 San Francisco偵偰乯丅3D僩儔僀僎乕僩僩儔儞僕僗僞偺奼戝幨恀乮幨恀亖塃乯

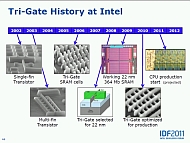

3D僩儔僀僎乕僩僩儔儞僕僗僞媄弍偺桪埵惈傪愢柧偡傞Intel 暃幮挿 寭 CTO偺僕儍僗僥傿儞丒儔僩僫乕巵乮幨恀亖嵍丄2011擭9寧偺IDF 2012 San Francisco偵偰乯丅3D僩儔僀僎乕僩僩儔儞僕僗僞偺奼戝幨恀乮幨恀亖塃乯丂3D僩儔僀僎乕僩僩儔儞僕僗僞媄弍偼丄2002擭偵Intel Resaerch偑敪昞偟丄検嶻壔偵岦偗偰媄弍奐敪傪恑傔偰偒偨丅偙偺媄弍偼丄揹棳傪惂屼偡傞僎乕僩偺峔憿傪2師尦偐傜3師尦偵偡傞偙偲偱丄儕乕僋揹棳傪梷惂偡傞偲偲傕偵丄僩儔儞僕僗僞枾搙偺岦忋傪壜擻偵偡傞丅

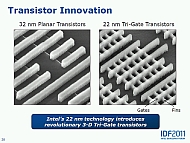

3D僩儔僀僎乕僩僩儔儞僕僗僞媄弍偼丄2002擭偵Intel Resarch偑敪昞偟偰偄傞偑丄幚嵺偺惢昳偵摫擖偡傞傑偱10擭嬤偔傪昁梫偲偟偨乮幨恀亖嵍乯丅32僫僲儊乕僩儖僾儘僙僗儖乕儖傪棙梡偟偰偄傞僾儔僫乕乮暯柺宆乯僩儔儞僕僗僞偲丄22僫僲儊乕僩儖僾儘僙僗儖乕儖傪棙梡偟偰偄傞3D僩儔僀僎乕僩僩儔儞僕僗僞偺揹巕尠旝嬀夋憸乮幨恀亖拞墰乯偲丄偦偺峔憿乮幨恀亖塃乯

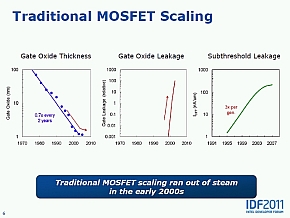

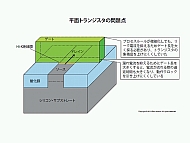

3D僩儔僀僎乕僩僩儔儞僕僗僞媄弍偼丄2002擭偵Intel Resarch偑敪昞偟偰偄傞偑丄幚嵺偺惢昳偵摫擖偡傞傑偱10擭嬤偔傪昁梫偲偟偨乮幨恀亖嵍乯丅32僫僲儊乕僩儖僾儘僙僗儖乕儖傪棙梡偟偰偄傞僾儔僫乕乮暯柺宆乯僩儔儞僕僗僞偲丄22僫僲儊乕僩儖僾儘僙僗儖乕儖傪棙梡偟偰偄傞3D僩儔僀僎乕僩僩儔儞僕僗僞偺揹巕尠旝嬀夋憸乮幨恀亖拞墰乯偲丄偦偺峔憿乮幨恀亖塃乯丂敿摫懱傪峔惉偡傞僩儔儞僕僗僞偺峔憿偼丄乽僜乕僗乿偲屇偽傟傞揹棳偺挋憼僄儕傾偲乽僪儗僀儞乿偲屇偽傟傞攔弌楬偺娫傪丄乽僎乕僩乿偲屇傇墎乮偣偒乯傪愝偗傞偙偲偱丄揹棳傪棳偟偨傝棳偝側偐偭偨傝偲偄偆惂屼傪峴側偭偰偄傞丅偲偙傠偑丄僾儘僙僗儖乕儖偺恑壔偵傛偭偰丄僎乕僩偺旝嵶壔偑恑傓堦曽偱丄儕乕僋揹棳乮楻傟揹棳乯偑媫憹偟丄徚旓揹椡傗敪擬検偑憹戝偡傞偙偲偵側偭偨丅

丂偦偙偱丄嵟嬤偺敿摫懱偱偼僎乕僩傪挿偔偟偰儕乕僋揹棳偺憹戝傪杊偄偱偄偨偑丄崱搙偼丄偙傟偑僩儔儞僕僗僞傪崅枾搙偡傞朩偘偵側偭偨丅偝傜偵丄僎乕僩傪挿偔偡傞偲丄揹婥偑棳傟傞偲偒偺抶墑帪娫偑戝偒偔側傞偨傔丄摦嶌僋儘僢僋傪堷偒忋偘偵偔偔偡傞尨場偵傕側偭偰偄偨丅

僾儘僙僗儖乕儖偺旝嵶壔偱儕乕僋揹棳偑戝暆偵憹偊偨丅偙傟傪杊偖偨傔僎乕僩挿傪挿偔嵦傜偞傞傪摼偢丄僩儔儞僕僗僞偺崅枾搙壔儁乕僗傕撦壔偟偰偄偨乮幨恀亖嵍乯丅22僫僲儊乕僩儖僾儘僙僗儖乕儖偵偍偗傞3D僩儔僀僎乕僩僩儔儞僕僗僞偺徻嵶傪愢柧偡傞儅乕僋丒儃傾巵乮幨恀亖塃丄2011擭9寧偺IDF 2012 San Francisco偵偰嶣塭乯

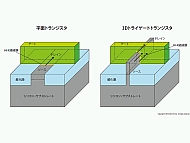

僾儘僙僗儖乕儖偺旝嵶壔偱儕乕僋揹棳偑戝暆偵憹偊偨丅偙傟傪杊偖偨傔僎乕僩挿傪挿偔嵦傜偞傞傪摼偢丄僩儔儞僕僗僞偺崅枾搙壔儁乕僗傕撦壔偟偰偄偨乮幨恀亖嵍乯丅22僫僲儊乕僩儖僾儘僙僗儖乕儖偵偍偗傞3D僩儔僀僎乕僩僩儔儞僕僗僞偺徻嵶傪愢柧偡傞儅乕僋丒儃傾巵乮幨恀亖塃丄2011擭9寧偺IDF 2012 San Francisco偵偰嶣塭乯丂偦偙偱丄僀儞僥儖偼丄戞3悽戙僀儞僥儖 Core 僾儘僙僢僒乕丒僼傽儈儕乕偱嵦梡偟偨3D僩儔僀僎乕僩僩儔儞僕僗僞媄弍偱丄偙傟傑偱暯柺峔憿偱峔抸偟偰偄偨僩儔儞僕僗僞傪埲壓偺傛偆偵曄偊偰偄偭偨丅

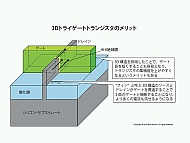

1丗僜乕僗偲僪儗僀儞傪乬戜抧乭偲偟偰僩儔儞僕僗僞忋偵峔抸偟丄偦偺娫偵僎乕僩傪90搙偵幷傞暻偲偡傞偙偲偱丄僜乕僗偲僪儗僀儞傪棫懱揑偵嵡偖乮3師尦壔乯

2丗偙傟傑偱1偮偺柺偩偗偱揹棳惂屼傪峴側偭偰偄偨偲偙傠傪丄3柺偱揹棳惂屼偑偱偒傞傛偆偵偡傞偙偲偱丄儕乕僋揹棳傪掅尭乮僩儔僀僎乕僩偲偼丄乽3柺傪僎乕僩偵偡傞乿偙偲傪堄枴偡傞乯

丂傑偨丄3D僩儔僀僎乕僩僩儔儞僕僗僞媄弍偱偼丄乽僜乕僗偲僪儗僀儞偺柺愊傕憹傗偣傞偺偱丄傛傝懡偔偺揹棳傪僩儔儞僕僗僞偵棳偣傞忋丄僎乕僩挿傪抁偔偱偒傞偨傔丄崅僋儘僢僋壔側偳偺崅惈擻壔傕梕堈偵側傞乿偲丄僀儞僥儖偱僾儘僙僗儖乕儖偺奐敪側偳傪巜婗偡傞儅乕僋丒儃傾巵偼愢柧偡傞丅摨巵偼傑偨丄乽3D僩儔僀僎乕僩僩儔儞僕僗僞媄弍傪摫擖偟偨22僫僲儊乕僩儖僾儘僙僗儖乕儖偼丄廬棃偺32僫僲儊乕僩儖僾儘僙僗儖乕儖偲斾傋偰丄37僷乕僙儞僩偺惈擻岦忋傪幚尰偡傞偐丄傑偨偼丄摨偠惈擻偱偁傟偽50僷乕僙儞僩偺徣揹椡壔偑壜擻偲側傞忋丄儕乕僋揹棳偼10暘偺1偵梷偊傜傟傞乿偲慽媮偡傞丅

僾儔僫乕乮暯柺宆乯僩儔儞僕僗僞偑捈柺偟偰偄偨栤戣揰乮幨恀亖嵍乯偲丄3D僩儔僀僎乕僩僩儔儞僕僗僞嵦梡偺儊儕僢僩乮幨恀亖拞墰乯丅3D僩儔僀僎乕僩僩儔儞僕僗僞媄弍傪嵦梡偡傞偙偲偱丄儕乕僋揹棳傪尭傜偟偰掅徚旓揹椡壔傪恾傝丄掅揹埑偱傕傛傝懡偔偺揹棳傪棳偣傞傛偆偵側傞偙偲偱崅惈擻壔傪恾傞偙偲偑壜擻偵側傞乮幨恀亖塃乯

僾儔僫乕乮暯柺宆乯僩儔儞僕僗僞偑捈柺偟偰偄偨栤戣揰乮幨恀亖嵍乯偲丄3D僩儔僀僎乕僩僩儔儞僕僗僞嵦梡偺儊儕僢僩乮幨恀亖拞墰乯丅3D僩儔僀僎乕僩僩儔儞僕僗僞媄弍傪嵦梡偡傞偙偲偱丄儕乕僋揹棳傪尭傜偟偰掅徚旓揹椡壔傪恾傝丄掅揹埑偱傕傛傝懡偔偺揹棳傪棳偣傞傛偆偵側傞偙偲偱崅惈擻壔傪恾傞偙偲偑壜擻偵側傞乮幨恀亖塃乯

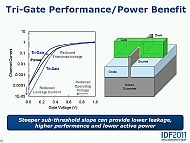

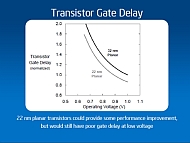

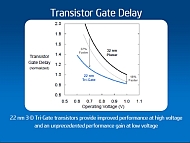

22僫僲儊乕僩儖僾儘僙僗儖乕儖偱傕丄僾儔僫乕宆僩儔儞僕僗僞媄弍傪嵦梡偡傞偲丄僷僼僅乕儅儞僗偺岦忋偼尷掕揑偵側傞偲尒傜傟偰偄偨乮幨恀亖嵍乯丅22僫僲儊乕僩儖僾儘僙僗儖乕儖偱丄3D僩儔僀僎乕僩僩儔儞僕僗僞媄弍傪嵦梡偟偨応崌丄掅揹埑帪偱37僷乕僙儞僩丄崅揹埑帪偱18僷乕僙儞僩偺惈擻岦忋偑婜懸偱偒傞乮幨恀亖塃乯

22僫僲儊乕僩儖僾儘僙僗儖乕儖偱傕丄僾儔僫乕宆僩儔儞僕僗僞媄弍傪嵦梡偡傞偲丄僷僼僅乕儅儞僗偺岦忋偼尷掕揑偵側傞偲尒傜傟偰偄偨乮幨恀亖嵍乯丅22僫僲儊乕僩儖僾儘僙僗儖乕儖偱丄3D僩儔僀僎乕僩僩儔儞僕僗僞媄弍傪嵦梡偟偨応崌丄掅揹埑帪偱37僷乕僙儞僩丄崅揹埑帪偱18僷乕僙儞僩偺惈擻岦忋偑婜懸偱偒傞乮幨恀亖塃乯Copyright © ITmedia, Inc. All Rights Reserved.

採嫙丗僀儞僥儖姅幃夛幮

傾僀僥傿儊僨傿傾塩嬈婇夋乛惂嶌丗ITmedia 亄D 曇廤晹乛宖嵹撪梕桳岠婜尷丗2012擭6寧30擔

傾僋僙僗僩僢僾10

- 敪昞帪偺斸敾偼棤曉傞丠丂僗儁僢僋悩偊抲偒偱傕乬攦偄乭偲尵偊傞丄嬌忋偺晛抜拝僗儅儂乽Pixel 10a乿傪怗偭偰傒偨 乮2026擭04寧27擔乯

- Windows 11偺晄枮夝徚傊丂Microsoft偺嵟桪愭僾儘僕僃僋僩乽Windows K2乿偲偼壗偐 乮2026擭04寧28擔乯

- 僒僀儃僂僘偺幮柤桼棃丂乬朧庡乭偵崬傔傜傟偨堄枴偑怺偡偓傞 乮2016擭07寧29擔乯

- 僉乕儃乕僪乽FILCO乿僽儔儞僪偺僟僀儎僥僢僋偑暵嬈丂4寧22擔晅偱 乮2026擭04寧24擔乯

- 儅僓乕儃乕僪偼乽嵶晹傑偱敀乿偑崱偺庡棳丠丂崅僐僗僷悈椻側偳尒摝偣側偄嵟怴帺嶌PC僷乕僣帠忣 乮2026擭04寧27擔乯

- 戝宆楢媥慜偺傾僉僶偼怴CPU儔僢僔儏両丂AMD乽Ryzen 9 9950X3D2乿偲Intel乽Core Ultra 5 250K Plus乛KF Plus乿偺婥偵側傞嵼屔忬嫷 乮2026擭04寧25擔乯

- 師婜乽DaVinci Resolve 21乿偱幨恀曇廤偑壜擻偵乛Google Cloud偑戞8悽戙TPU傪敪昞 乮2026擭04寧26擔乯

- 僄儗僐儉丄巑榊惓廆僨僓僀儞儅僂僗乽M.A.P.P.乿暅崗儌僨儖偺梊栺斕攧傪4寧6擔偵奐巒 乮2026擭03寧25擔乯

- 15.6宆儌僶僀儖僨傿僗僾儗僀乽ASUS ZenScreen MB169CK-J乿偑21亾僆僼偺1枩7172墌偵 乮2026擭04寧27擔乯

- 庤偺傂傜僒僀僘偱AI偑摦偔両丂嶻嬈丒價僕僱僗傪巟偊傞嵟怴乽儈僯PC乿乽GPU僒乕僶乿揥帵儗億乕僩 乮2026擭04寧28擔乯