大解説! “Broadwell-Y”な「Core M」はここがすごい(前編):14ナノメートル導入のメリットとは(1/2 ページ)

厚さ9ミリ以下のボディで高性能を発揮するCore M

Intelは8月11日(現地時間)、同社の次世代半導体製造技術となる14ナノメートルプロセスルールと、このプロセスルールを採用する次世代CPU「Core M」(開発コード名「Broadwell-Y」)の概要を明らかにした。

IntelでBroadwellアーキテクチャを採用する14ナノメートルプロセスルールの開発を統括するIntel プラットフォームエンジニアリンググループ担当上級副社長のラニ・ボーカー氏は、Core Mの開発にあたり、「厚さ9ミリ以下のファンレスで2-in-1スタイルのデバイスに、Coreプロセッサー・ファミリーの性能を使ってもらうべく、アーキテクチャと半導体プロセスルールの最適化を図った」と説明する。

Core Mは、現行製品と同等の性能であればTDP(Thermal Design Power:熱設計消費電力)を半分以下に抑え、CPUパッケージのサイズも従来の半分にすることで、より薄く、軽量なシステムの構築を可能にする。

Intelは、このCore M搭載システムの第1弾が、2014年の年末商戦に登場するとしており、2015年の前半には多数のモデルが登場することで、14ナノメートルプロセスルールへの移行が本格化すると語っている。

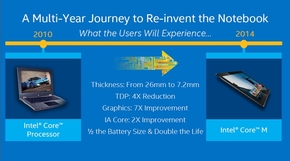

Core Mの特徴。厚さ9ミリ以下のファンレス2-in-1デバイスを実現すべく、設計と最適化がなされた(写真=左)。2010年のWestmereaアーキテクチャを採用するArrandaleベースのノートPCと、Broadwell-Y搭載2-in-1デバイスのリファレンスデザインとなるLama Mountainの比較。その厚さは26ミリから7.2ミリへ、TDPは4分の1となり、グラフィックス性能は7倍、CPUコア性能も2倍向上しつつ、半分のバッテリサイズで倍の駆動時間を実現する(写真=右)

Core Mの特徴。厚さ9ミリ以下のファンレス2-in-1デバイスを実現すべく、設計と最適化がなされた(写真=左)。2010年のWestmereaアーキテクチャを採用するArrandaleベースのノートPCと、Broadwell-Y搭載2-in-1デバイスのリファレンスデザインとなるLama Mountainの比較。その厚さは26ミリから7.2ミリへ、TDPは4分の1となり、グラフィックス性能は7倍、CPUコア性能も2倍向上しつつ、半分のバッテリサイズで倍の駆動時間を実現する(写真=右)第2世代に進化したトライゲート

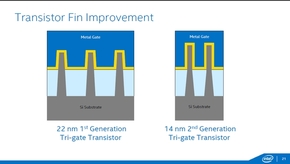

Intelは、14ナノメートルプロセスルールを「第2世代のトライゲートトランジスタ技術」とも呼ぶように、22ナノメートルプロセスルールで採用した立体構造のゲートをさらに進化させている。

半導体を構成するトランジスタは、「ソース」と呼ばれる電流の貯蔵エリアと「ドレイン」と呼ばれる排出路の間に「ゲート」と呼ぶ堰(せき)を設けることで、電流を流したり流さなかったりという制御を行なっている。

このゲートの容積で、トランジスタに流す電流量が決まるため、Intelは22ナノメートルプロセスルールでトランジスタを微細化しても、ソースやドレイン、ゲートを立体構造にすることで、電流量を減らすことなく、高速なCPUを作れるようにした。

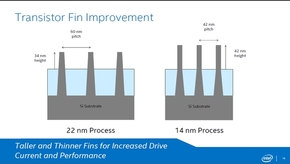

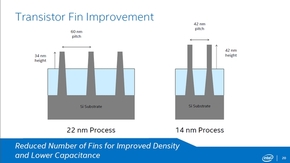

14ナノメートルプロセスルールでは、フィンと呼ばれる立体構造のソースとドレインの間隔やゲート間隔を狭めながら、一方でフィンの高さを増やすことで、微細化しても高性能CPUに必要な電流量を確保できるようにするとともに、トランジスタ密度をさらに高めることを可能にしている。

また、ゲート長が短くなったことで、ソースからドレインの間に電気が流れるときの遅延時間が抑えられ、動作クロックを引き上げることも容易になるため、トランジスタ上に複数のフィンを成形し、より大きな電流を流せるようにすれば、高性能なCPUを設計しやすくなるというメリットもある。

具体的には、第2世代のトライゲートトランジスタ技術を採用した14ナノメートルプロセスルールでは、現行の22ナノメートルプロセスルールと比べて、次のように微細化を実現した。

| 間隔 | 22ナノメートルプロセスルール | 14ナノメートルプロセスルール | 微細化の割合 |

|---|---|---|---|

| フィン間隔 | 60ナノメートル | 42ナノメートル | 約70%の微細化 |

| ゲート間隔 | 90ナノメートル | 70ナノメートル | 約78%の微細化 |

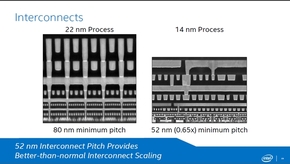

| インターコネクト間隔 | 80ナノメートル | 52ナノメートル | 65%の微細化 |

第2世代のキーワードは「狭くしたら高くする」

その一方で、ゲート高だけは34ナノメートルから42ナノメートルと約124%に拡大した。ゲートを高くすることで微細化にともなう電流量の低減を抑えるとともに、より少ないフィン数でトランジスタを構成することで、高密度化を可能にしている。

14ナノメートルプロセスルールでは、22ナノメートルプロセスルールと比較して、フィン間隔を狭くする一方で、ゲートを高くして電流量を確保した。より少ないフィンでトランジスタを構成できるようにすることで、高密度化も可能にしている

14ナノメートルプロセスルールでは、22ナノメートルプロセスルールと比較して、フィン間隔を狭くする一方で、ゲートを高くして電流量を確保した。より少ないフィンでトランジスタを構成できるようにすることで、高密度化も可能にしている

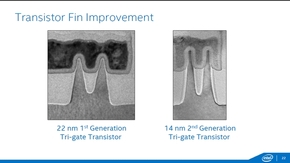

ゲート電極に金属を使ったメタルゲートとフィンの絶縁膜には、従来通りにHi-K素材を採用し、リーク電流を最小限に抑える(写真=左)。22ナノメートルプロセスルールトライゲートプロセスと14ナノメートルプロセスルール第2世代トライゲートのトランジスタを電子顕微鏡で比較する(写真=右)

ゲート電極に金属を使ったメタルゲートとフィンの絶縁膜には、従来通りにHi-K素材を採用し、リーク電流を最小限に抑える(写真=左)。22ナノメートルプロセスルールトライゲートプロセスと14ナノメートルプロセスルール第2世代トライゲートのトランジスタを電子顕微鏡で比較する(写真=右)

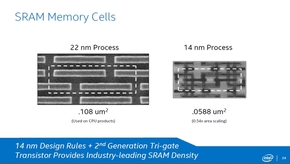

トランジスタの各層を接合するインターコネクト間隔も80ナノメートルから52ナノメートルに微細化され、チップの薄型化を可能にしている(写真=左)。2次キャッシュメモリなどに利用されるSRAMのメモリセルで比較すると、14ナノメートルプロセスルールは22ナノメートルプロセスルールの54%のダイサイズに微細化することができるという(写真=右)

トランジスタの各層を接合するインターコネクト間隔も80ナノメートルから52ナノメートルに微細化され、チップの薄型化を可能にしている(写真=左)。2次キャッシュメモリなどに利用されるSRAMのメモリセルで比較すると、14ナノメートルプロセスルールは22ナノメートルプロセスルールの54%のダイサイズに微細化することができるという(写真=右)Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- きょう発売の「MacBook Neo」、もうAmazonで割安に (2026年03月11日)

- セールで買った日本HPの約990gノートPC「Pavilion Aero 13-bg」が想像以上に良かったので紹介したい (2026年03月11日)

- 10万円切りMacが17年ぶりに復活! 実機を試して分かったAppleが仕掛ける「MacBook Neo」の実力 (2026年03月10日)

- 12機能を凝縮したモニタースタンド型の「Anker 675 USB-C ドッキングステーション」が27%オフの2万3990円に (2026年03月11日)

- 3万円超でも納得の完成度 VIA対応の薄型メカニカルキーボード「AirOne Pro」を試す キータッチと携帯性を妥協したくない人向け (2026年03月12日)

- 「MacBook Neo」を試して分かった10万円切りの衝撃! ただの“安いMac”ではなく絶妙な引き算で生まれた1台 (2026年03月10日)

- エンスージアスト向けCPU「Core Ultra 200S Plus」登場 Eコア増量+メモリアクセス高速化+バイナリ最適化でパフォーマンス向上 (2026年03月11日)

- 新型「MacBook Air」はM5搭載で何が変わった? 同じM5の「14インチMacBook Pro」と比べて分かったこと (2026年03月10日)

- 高音質・良好な装着感・バッテリー交換式――JBLのフラッグシップ「Quantum 950 WIRELESS」は妥協なきヘッドセットか (2026年03月12日)

- M5 Max搭載「14インチMacBook Pro」がワークステーションを過去にする 80万円超の“最強”モバイル AI PCを試す (2026年03月13日)