第2回 Coreマイクロアーキテクチャ [前編]:新約・見てわかる パソコン解体新書(3/4 ページ)

複数の命令を同時実行するスーパースケーラ

パイプラインをどんなに細分化しても、パイプラインの最後から処理結果が出てくるスピードは、1クロックごとに1つです。これがPentium以前のCPUの限界でした。初代Pentiumで画期的だったのは、1クロックで1つ以上の命令を実行可能な、スーパースケーラという技法を取り入れている点です。

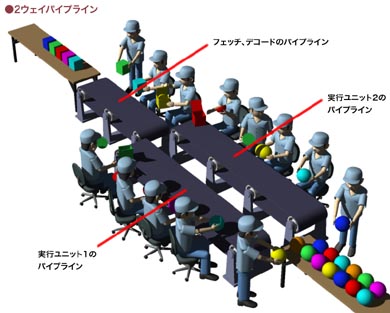

スーパースケーラを簡単に説明したのが、下の図です。

ご覧の通り、命令を実行処理するパイプラインが2本並べて設置されています。これで1クロックで2命令が実行できるというわけです。さらに、パイプラインを3本に増やせば、1クロックで3命令が実行できます!

というのは実はウソで、話はそう簡単ではありません。まず、すべての種類の命令を処理可能なパイプラインを複数用意するのは、CPUの回路が大規模になりすぎて難しいのです。そこで、最初のPentiumでは、片方のパイプラインはすべての命令が処理できるけれども、もう一方のパイプラインは回路規模が小さくて、単純な命令だけしか処理できないようになっていました。機能が高度な命令は片方のパイプラインでしか処理できないので、プログラム中で高度な命令が連続している部分は、片方のパイプラインだけを動かして命令を1つずつ処理することになります。

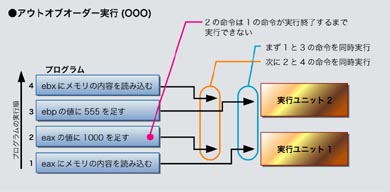

また、1つの命令の処理結果を次の命令が参照する、命令間に依存関係がある場合は、その2つの命令は同時に実行できないことは明らかです。このような場合は、後の命令の処理を止めて、前の命令が終了するのを待たなければいけません。

以上のように、両方のパイプラインが常に働くわけではない(片方のパイプラインが時々止まる)ので、平均的な命令実行効率は1クロックあたり2命令以下になります。できるだけ複数あるパイプラインを止めずに命令の処理を進められるように、現在のCPUにはOOO(アウト・オブ・オーダー)という機能が搭載されています。OOOでは、プログラムされた命令の並びを無視して、実行可能な命令から先に処理を進めてしまいます。

空いている回路を有効利用してもう1つのCPUを作り出す!

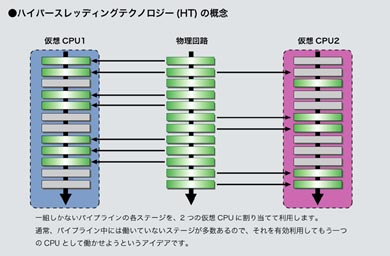

残念ながら、OOOを採用しても、実行ユニットの使用効率は100%にはなりません。実行ユニットだけではなく、パイプラインのいろいろなステージの回路が、処理すべき命令が回ってこなくて待機状態になることが頻繁にあるからです。たとえば、分岐予測ミスが発生したときはパイプライン内が空にされて、それからしばらくはパイプラインの下流には命令が流れて行きません。

インテルは、この無駄に遊んでいる回路を有効活用するために、ハイパー・スレッディング・テクノロジー(HT)という手法を編み出しました。遊んでいる回路を、もう1つ別のCPUとして働かせようと言うのです。HTにより、実際にはCPUは1つしかないけれど、デュアルコアのように見えるCPUができあがるのです。このHTは、個人向けCPUではPentium 4 3.06GHzで初めて実装されました。

マイクロOps

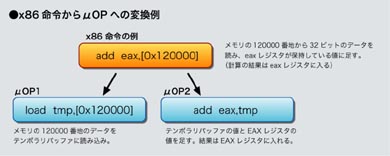

前のほうで、x86命令の1つ1つは単純な働きしかしないと書きました。しかし、単純とは言いながらある程度の複雑さを持っているのがx86命令の特徴です。たとえば、add eax,[120000h]という命令は、「メモリの120000h番地からデータを読んで、eaxレジスタの値に足す」という働きをしますが、よく見ればメモリへのアクセスと足し算という、2つの仕事をすることが分かります。CPUの回路にとっては、これは十分に複雑なことなのです。

また、x86命令は、マシンコードの長さが1バイトから数バイトと一定していない点も複雑と言えます。CPUの中にある、命令の意味を判断するデコード回路が複雑になってしまいます。ちなみに、最近までアップルコンピュータのPower Macが採用していたPowerPCシリーズのCPUは、メモリアクセスと演算は必ず別命令となっているうえ、マシンコードの長さも一定です。

x86命令のような複雑な命令系を持つCPUのことをCISC(複雑命令セットコンピュータ)、PowerPCのようなシンプルな命令系を持つCPUのことをRISC(縮小命令セットコンピュータ)と呼んで区別することがあります。

複雑なx86命令は、高速に処理したり、スーパースケーラで複数命令を同時実行するのに不利です。そこで、1995年11月登場のPentium Proにおいて、複雑なx86命令をマイクロOpsと呼ばれる複数の単純命令に置き換えたうえでパイプラインに投入してスーパースケーラで処理するという仕組みが実装されました。

x86命令のうち、働きが単純なものについては1命令が1つのマイクロOpsに変換されますが、働きが複雑な命令は2個から4個のマイクロOps(μOps)に変換されます。インテルはマイクロOpsの詳細を公開していませんが、命令の長さは118ビットの固定長と言われています。

なお、OpsはOperations(作業、操作の複数形)のことです。

Pentium 4のアーキテクチャ

Pentium 4の内部構造に、インテルは「NetBurstマイクロアーキテクチャ」という名前を付けています。NetBurstの大きな特徴として、実行トレースキャッシュの存在があります。実行トレースキャッシュは、普通のCPUのL1命令キャッシュに相当するものです。メインメモリ内にある、x86命令で作られたプログラムは、Pentium 4の内部に読み込まれて、マイクロOpsのプログラムに変換されます。変換されたプログラムは、実行トレースキャッシュに格納されます。そして、実行トレースキャッシュからマイクロOpsが読み出されてパイプラインに投入され、実行されるという仕組みです。

実行するプログラムの部分が実行トレースキャッシュに入っている限りは、x86命令からマイクロOpsへの変換作業が不要で、素早く処理を進めることができます。

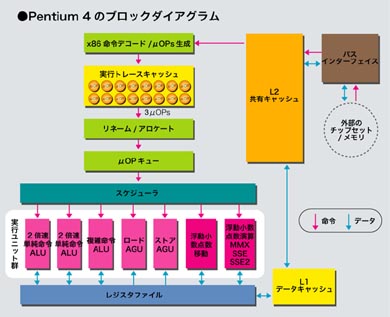

Pentium 4の単純化したブロックダイアグラムを下に示します。実際には、各ブロックが複数のステージで構成されていて、全体が長いパイプラインを形成します。

Pentium 4のパイプラインは31段と言われますが、これは実行トレースキャッシュより下流の部分だけを指しています。x86命令のデコードを行うブロックも、パイプライン構造をとっていますが、ここは実行トレースキャッシュにヒットし続ける限りは動きません。

実行トレースキャッシュから読み出されたマイクロOpsは、必要な前処理を済ませてマイクロOpsキューに蓄えられます。スケジューラは、このキューの中からすぐに実行可能なマイクロOpsを選択して、7個ある実行ユニットに分配され、同時実行されます。とはいえ、いろいろな理由から7つのマイクロOpsが同時に実行できるわけではなく、最大でも同時実行マイクロOps数は5つ、平均では3つ以下です。

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- スウェーデンのファンドが「価格.com」「食べログ」約5900億円でカカクコムを買収へ AI戦略を加速 (2026年05月13日)

- 待望のカラー版も選べて大型化! Amazonが「Kindle Scribe」2026年モデルを発表 Google Drive連携など機能も強化 (2026年05月12日)

- Googleが「Googlebook」をチラ見せ AndroidとChromeOSを“融合”した全く新しいノートPC 詳細は2026年後半に紹介 (2026年05月13日)

- 「MacBook Neo」は「イラスト制作」に使えるか? Appleが仕掛ける“価格の暴力”を考える (2026年05月12日)

- NVIDIA“一強”を突き崩すか AMDのAIソフトウェア「ROCm」と次世代GPU「Instinct MI400」がもたらす新たな選択肢 (2026年05月12日)

- 高騰続くパーツ市場、値札に衝撃を受ける人からDDR4使い回しでしのぐ自作erまで――連休中のアキバ動向 (2026年05月11日)

- ノートPCを4画面に拡張できる“変態”モバイルディスプレイ「ROADOM 14型 モバイルマルチディスプレイ X90M」が6万1560円に (2026年05月12日)

- 約2000円で購入できる「エレコム USB扇風機 FAN-U177BK」 (2026年05月12日)

- 画面を持たない約12gの超軽量ウェルネストラッカー「Google Fitbit Air」 1万6800円で5月26日に発売 (2026年05月07日)

- AIでギターやボーカルを消去! JBLの楽器練習向け次世代スピーカー「BandBox」が公開 クラファン価格は3万5200円から (2026年05月13日)