第2回 Coreマイクロアーキテクチャ [前編]:新約・見てわかる パソコン解体新書(4/4 ページ)

CPUのパフォーマンスを向上させる技法

人類は、35年前にCPUを生み出して以来、ひたすらパフォーマンス(性能)の向上を追求してきました。

CPUのパフォーマンスの指標はいくつかありますが、ここではIPC値(Instruction Per Clock:1クロックあたりの平均命令実行数)と動作周波数を掛けた値、すなわち1秒あたりの処理命令数をパフォーマンスとして示すことにします。

よりパフォーマンスの高いCPUを作るためには、IPC値と動作周波数のいずれか、あるいは両方を高くすればよいことは簡単に理解できるでしょう。

IPC値を高めるための代表的な手法が、複数の命令を並列処理するスーパースケーラと呼ばれる機能です。たとえば命令の実行ユニットを5つ実装すれば、瞬間最大風速としてのIPC値は5になります。ただし、命令の依存関係そのほかの事情からすべての実行ユニットが常に働くことはできません。また、分岐予測ミスの発生も、IPC値を低下させるので、平均的なIPC値は実行ユニットの個数よりもかなり低い値になります。

IPC値を高くする手法を列挙します。

1.スーパースケーラ

2.高速大容量のキャッシュメモリ

3.分岐予測機能と投機実行

4.レジスタリネーミング

次に、動作周波数を高くする方法ですが、これは3つあります。

1.パイプラインを細分化してステージ数を増やす

2.製造プロセスの微細化

3.駆動電圧を高くする

これらの方法は、それを採用することによって次のようなデメリットがあります。

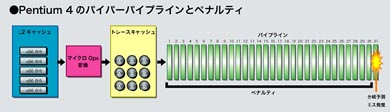

1.パイプライン細分化のデメリット

パイプラインのステージ数が増えるほど、分岐予測が外れたときのペナルティが重くなり、IPC値を低下させます。PrescottコアのPentium 4は、パイプラインを31ステージに細分化することで、3GHz以上という高い動作周波数を実現しましたが、分岐予測ミスのペナルティが大きく、IPC値が低くなっています。Pentium 4が、動作周波数が高い割にパフォーマンスが低いと言われるのはこのためです。

2.製造プロセス微細化のデメリット

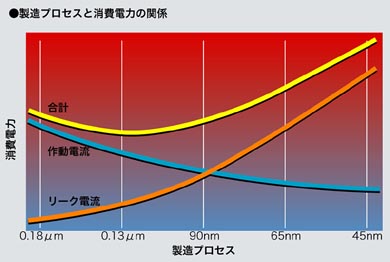

CPUの回路を構成するトランジスタは、小さく作るほどスイッチング速度が速くなります。製造プロセスはPentium IIまでは0.35マイクロメートルでしたが、Pentium IIIで0.18マイクロメートルに縮小されました。Pentium 4では、0.13マイクロメートルからスタートして、90ナノメートル、65ナノメートル へと微細化が進められました。最新のCore 2 Duoは65ナノメートルで製造されています。

トランジスタは、製造プロセスを微細化するほど、スイッチングが速くなると同時に、スイッチング動作時の消費電力も減る特性があります。ところが、製造プロセスが微細化すると、リーク電流が大きくなります。リーク電流というのは、トランジスタの中で勝手に漏れて流れる電流で、トランジスタが動作していないときにも電流が流れ続けて無駄に電力を消費します。

製造プロセスが0.13マイクロメートルになるまでは、作動電流の減少の方がリーク電流の増加よりも大きかったために、CPU全体の消費電力を下げることができました。ところが、Pentium 4の製造プロセスが90ナノメートル以下になると、リーク電流が激しく増大してしまい、作動電流の減少分など焼け石に水という状況になってしまったのです。これは、CPU製造メーカーが直面している大きな壁の1つです。

インテルは、90ナノメートルの製造プロセスにおいて、いくつかのリーク電流抑制技術を採用し、それをさらに改良して65ナノメートルの製造プロセスに投入しています。詳しくは次回お話しする予定です。

3.駆動電圧を高めることのデメリット

CPUの回路は、CMOSと呼ばれる回路構造を採用していますが、CMOS回路は電圧が高いほどスイッチング動作が高速になる特性があります。ところが、CPUの消費電力は、電圧の二乗に比例して増大します。電圧を少し上げただけで、消費電力は大きく上がってしまうのです。

上の式の通り、CPUの消費電力は、トランジスタ数と動作周波数にも比例して増大します。PrescottコアのPentium 4のトランジスタ数は1億2500万個と膨大なうえ、動作周波数は最大3.8GHz。さらにリーク電流が加わって3重苦。消費電力が100ワットを大きく超えるところまで来てしまいました。このまま消費電力が増え続けると、普通の方法では冷却しきれなくなる恐れすらあります。

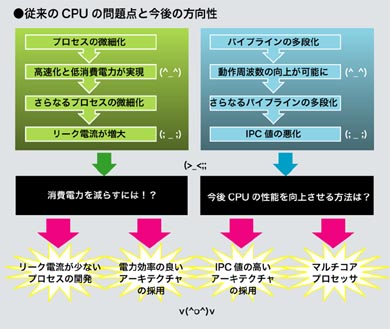

インテルがこれまで進めてきた、プロセスの微細化とパイプラインの多段化による高クロック、高パフォーマンスの追求は、Pentium 4で限界に達したと言えます。この壁を破ってさらに高いパフォーマンスを実現する方法はあるのでしょうか? インテルはいま2つのアプローチを試みています。

1.1つのCPUパッケージに、複数のCPUコアを実装するマルチコアCPU

2.低い動作周波数でも高いパフォーマンスを得られるIPC値の高い新しいアーキテクチャ

1のアプローチの最初の応用製品がPentium Dで、Core Duo、Core 2 Duoへとつながり、次は4コアの製品が登場予定です。

Core DuoとCore2 Duoは、デュアルコアであり、さらに2のアプローチである新しいアーキテクチャを採用したCPUです。

なお、プロセスの微細化によってリーク電流は増えるものの、トランジスタのスピードアップと製造コストダウンというメリットがありますから、プロセスの微細化は今後も続けられます。リーク電流を減らす技術の研究も進められていて、その成果はPentium4やCoreシリーズにも投入されています。

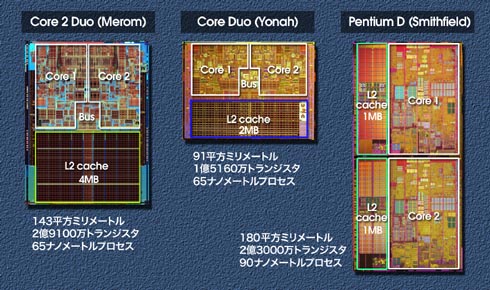

下は、Core 2 Duo、Core Duo、Pentium Dのダイ写真です。1つのダイの上に、2つのCPUコアが形成されていることがわかります。Core 2 Duoは、最新の65ナノメートルプロセスで製造されています。1世代前の、90ナノメートルで製造されるPentium Dと比べて、Core 2 Duoはトランジスタ数が増えているにもかかわらず、ダイの面積は縮小しています。

なお、CPUのコア(核)とは、命令を処理するための回路を指します。L1キャッシュは命令の読み込み回路と密につながっているためにコアに含まれていると考えますが、L2キャッシュと外部バスの回路はコア外になります。

次回はCore 2 Duoが採用する、インテルの新しいCPUアーキテクチャ、Coreマイクロアーキテクチャの秘密を追うことにします。お楽しみに!

関連記事

第1回 パソコン解体新書ができるまで

第1回 パソコン解体新書ができるまで

「見てわかるパソコン解体新書」が、オンライン版で復活することになりました。 名前は「パソコン解体全書」です

名前は「パソコン解体全書」です

PC USERでおなじみの「見てわかる パソコン解体新書」が1冊の本になりました。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- スウェーデンのファンドが「価格.com」「食べログ」約5900億円でカカクコムを買収へ AI戦略を加速 (2026年05月13日)

- 待望のカラー版も選べて大型化! Amazonが「Kindle Scribe」2026年モデルを発表 Google Drive連携など機能も強化 (2026年05月12日)

- Googleが「Googlebook」をチラ見せ AndroidとChromeOSを“融合”した全く新しいノートPC 詳細は2026年後半に紹介 (2026年05月13日)

- 「MacBook Neo」は「イラスト制作」に使えるか? Appleが仕掛ける“価格の暴力”を考える (2026年05月12日)

- NVIDIA“一強”を突き崩すか AMDのAIソフトウェア「ROCm」と次世代GPU「Instinct MI400」がもたらす新たな選択肢 (2026年05月12日)

- 高騰続くパーツ市場、値札に衝撃を受ける人からDDR4使い回しでしのぐ自作erまで――連休中のアキバ動向 (2026年05月11日)

- ノートPCを4画面に拡張できる“変態”モバイルディスプレイ「ROADOM 14型 モバイルマルチディスプレイ X90M」が6万1560円に (2026年05月12日)

- 約2000円で購入できる「エレコム USB扇風機 FAN-U177BK」 (2026年05月12日)

- 画面を持たない約12gの超軽量ウェルネストラッカー「Google Fitbit Air」 1万6800円で5月26日に発売 (2026年05月07日)

- AIでギターやボーカルを消去! JBLの楽器練習向け次世代スピーカー「BandBox」が公開 クラファン価格は3万5200円から (2026年05月13日)