AMD、45ナノ“Shanghai”Opteron発表──Denebは「Phenom II」に:元麻布春男のWatchTower(1/2 ページ)

最高クロック2.7GHzの45ナノプロセスルールOpteron

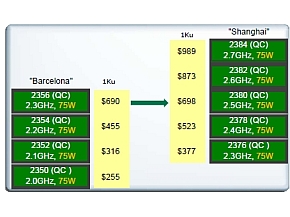

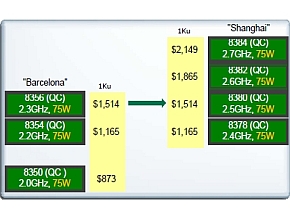

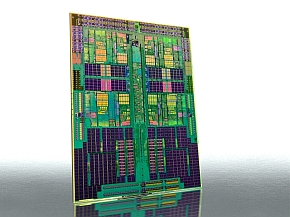

AMDは、11月13日に同社初の45ナノメートルプロセスルールを採用したCPUとして、これまで“Shanghai”という開発コード名で知られてきたクアッドコアOpteronの2300番台5モデル(デュアルソケットサーバ向け)と、同じく8300番台4モデル(4ソケットサーバ向け)を発表した。最高動作クロックはOpteron 2384とOpteron 8384の2.7GHzで、今回登場したすべてのモデルが消費電力75ワット(ACP、平均消費電力)となっている(熱設計時消費電力であるTDPは95ワット)。

消費電力を55ワット(ACP)に抑えたHE版、消費電力を105ワット(同)へ引き上げる代わりに動作クロックを向上させるSE版は、2009年第1四半期に追加される予定だ。また、時期は明言されなかったものの、1ソケットサーバ向けのOpteron 1000番台(開発コード名“Suzuka”)も、後に投入するとしている。

AMDの45ナノプロセスルールは、基本的に従来の65ナノプロセスルールの延長にある。SOIウェハ、歪みシリコン技術など、主要な要素技術を継承しつつ、改良を重ねた。AMDは製造部門を別会社に分離する意向を示しているが、現時点で次世代以降の製造技術ロードマップに変更はない。

次の32ナノプロセスルールではSOIウェハに加え、バルクウェハ(バルクシリコン)を用いたプロセス技術を採用すると同時に、High-k/Metal Gate技術を採用する。ただし、主力となるCPUについては引き続きSOI技術が用いられる見込みで、バルクウェハはGPUやチップセット、あるいは分離される新会社が展開する予定のファウンダリ事業で利用されることになる(CPUとGPUの合体であるFusionがSOIとバルクのどちらになるかは注目される)。

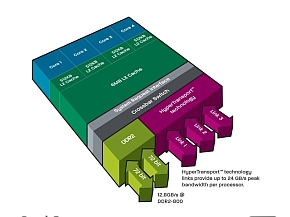

製造プロセスが45ナノメートルに縮小されたことの最大の利点は、3次キャッシュメモリが6Mバイトに増量されたことに現れている。従来のクアッドコアOpteronのマイクロアーキテクチャでは、1次、および2次キャッシュメモリがコアごとに独立しており、4つのコアで2Mバイトの3次キャッシュメモリを共有していた。Shanghaiでは基本的なキャッシュメモリのアーキテクチャ(コアごとに独立した512Kバイトの2次キャッシュメモリ)は不変のまま、3次キャッシュメモリが3倍になったことになる。

Barcelonaと比べて20%の性能向上を実現

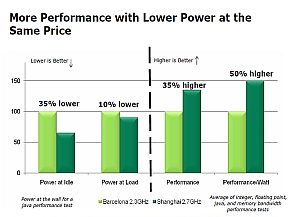

3次キャッシュメモリがほぼ同じ(小改良の)マイクロアーキテクチャでありながら、Shanghaiは同一クロックのBarcelonaに対し、約20%の性能向上が図られたとAMDは説明している。さらに45ナノプロセスルールの採用により、最高動作クロックが2.7GHzに引き上げられたこと、メモリクロックが400MHzに向上したこと(DDR2-800対応)により、トータルで従来のBarcelona 2.3GHzに対し、35〜50%の性能向上が期待されている。その一方で、消費電力はアイドル時で35%、ロード時で10%ほど引き下げられており、1ワットあたりの性能はさらに向上したこともAMDは強く訴求している。

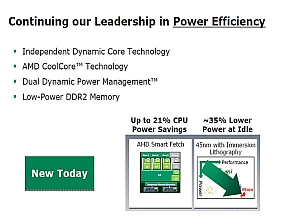

“Barcelona”Opteron、“Shanghai”Opteronで比較したベンチマークテストの結果。このデータは動作クロックが異なるモデルで比較しているが、同クロックでも20%の性能向上が期待できるとAMDはアピールする(写真=左)。45ナノプロセスルールの採用で、CPUの省電力は21%も進み、アイドル時消費電力は35%も低減した(写真=右)

“Barcelona”Opteron、“Shanghai”Opteronで比較したベンチマークテストの結果。このデータは動作クロックが異なるモデルで比較しているが、同クロックでも20%の性能向上が期待できるとAMDはアピールする(写真=左)。45ナノプロセスルールの採用で、CPUの省電力は21%も進み、アイドル時消費電力は35%も低減した(写真=右)Shanghaiのもう1つの特徴は、メモリクロックを除き、ソケット、消費電力、熱設計などの点で、既存のSocket Fプラットフォーム(HyperTransport 1.0×3、デュアルチャネルDDR2メモリ)と互換性を持つことだ。DDR2-667メモリで構わなければ、そのままBarcelonaと差し替えて運用できる。初期においてShanghaiは、DDR2-667メモリとHyperTransport 1.0に対応した現行の第2世代プラットフォームで使われることになるだろう。

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- 「ANAオリジナル タフなビジネスリュック」を試す 収納力もバツグンで鳥肌が立つほどにカッコいい (2026年04月07日)

- GoogleのAシリーズ最新作「Pixel 10a」は7万9900円から カメラの出っ張りが消えて新色も追加 (2026年04月07日)

- レノボが「ThinkPad」2026年モデルを一挙発表! 12年ぶりの構造刷新やUSB Type-Cの自力交換対応でメンテナンス性も向上 (2026年04月07日)

- 「Google Pixel 10a」に日本限定カラー登場! ヘラルボニーとのコラボで多様性を表現する特別な「Isai Blue」(異彩青) (2026年04月07日)

- ANAがビジネスユースに特化した耐久性重視のビジネスバッグ3製品を発売 (2025年11月14日)

- 待望の「Core Ultra 7 270K Plus」は静かな船出――アキバでは激安ピラーレスケースなど“高コスパ”パーツに熱視線 (2026年04月06日)

- Googleが最新オープンAIモデル「Gemma 4」を公開 (2026年04月06日)

- NVIDIAが「G-SYNC Pulsar」対応ディスプレイを日本初披露 何がすごい? (2026年04月06日)

- 迷走の5年間を経て――MicrosoftがWindows 11の“不都合な真実”を認め、改善を宣言した背景 (2026年04月01日)

- FCCLがこだわりのキーボード「FMV Keyboard X」をクラファン形式で販売 約2.3万円から (2026年04月07日)