マルチコアから高性能コアで進化を目指すインテルのCPU:Sandy Bridgeは“12畳半”のはずだった(3/4 ページ)

CPUにVRMを統合するのは省電力の流れ

IDF 2008で紹介した電圧変換回路をCPU上に搭載するCMOS電圧レギュレタ技術。試作チップではCPUコアとチップセットコアに加えCMOS電圧レギュレータチップを搭載していたが、Haswellでは、CPUやチップセットにこの技術が統合される

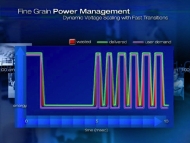

IDF 2008で紹介した電圧変換回路をCPU上に搭載するCMOS電圧レギュレタ技術。試作チップではCPUコアとチップセットコアに加えCMOS電圧レギュレータチップを搭載していたが、Haswellでは、CPUやチップセットにこの技術が統合されるラトナー氏は、CPUの低消費電力化の第1歩は「CPUに電圧レギュレータを統合することだ」と説明する。ラトナー氏は、2005年の8月に開催されたIDF Fall 2005の基調講演で、現在マザーボード上に搭載している電圧変換回路(VRM:Voltage Regulation Module)をCPUに統合するCMOS電圧レギュレータに関する発表を行なった。同氏は「現在、CPUの電力リクエストに応じてオンボードの電圧変換回路を動かしていたのでは、電力効率が悪い。これをCPU上に統合すれば、単一電圧供給で、より高速に電圧を変更できるため、電力効率を15〜30%ほど向上する」という。

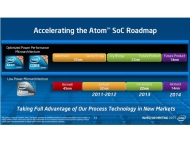

さらにラトナー氏は、「この技術は、2013年に市場投入する“Haswell”(開発コード名)で実装するほか、Atomについても、22ナノメートルプロセスルールと3Dトライゲートを採用する“Silvermont”(開発コード名)で同技術を採用する」と明らかにしている。

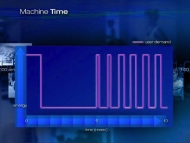

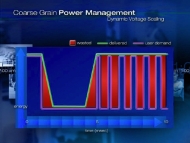

CPUの電力要求(写真=左)と2005年当時の一般的なシステムにおける電力供給(写真=中央)。CPUの電圧変動や電力要求の速さに電圧変換回路側が追従できず、電力がムダになっていると指摘。CMOS電圧レギュレータでは、CPU上で電圧をより拘束かつ小まめに変換できるようになるため、電力効率や消費電力も向上するという(写真=右)

CPUの電力要求(写真=左)と2005年当時の一般的なシステムにおける電力供給(写真=中央)。CPUの電圧変動や電力要求の速さに電圧変換回路側が追従できず、電力がムダになっていると指摘。CMOS電圧レギュレータでは、CPU上で電圧をより拘束かつ小まめに変換できるようになるため、電力効率や消費電力も向上するという(写真=右)

IDF Fall 2005のラトナー氏のキーノートで公開されたCMOS電圧レギュレータのデモシステム(写真=左)。IDF Fall 2005において、電圧変換回路やチップセット機能をCPUに統合することで、マザーボードから不要な部品を取り除くとどうなるかを示したマザーボード。MCHや大半の電圧変換回路が外されている(写真=中央、右)

IDF Fall 2005のラトナー氏のキーノートで公開されたCMOS電圧レギュレータのデモシステム(写真=左)。IDF Fall 2005において、電圧変換回路やチップセット機能をCPUに統合することで、マザーボードから不要な部品を取り除くとどうなるかを示したマザーボード。MCHや大半の電圧変換回路が外されている(写真=中央、右)

Haswellでは、電圧変換回路の統合技術を採用することで大幅に電力効率を向上させようとしている(写真=左)。IDF San Francisco 2011で公開されたHaswell(写真=中央)。ラトナー氏は22ナノメートルプロセスルールを採用する将来のAtom“Silvermont”でも電圧変換回路をCPUに統合するという(写真=右)

Haswellでは、電圧変換回路の統合技術を採用することで大幅に電力効率を向上させようとしている(写真=左)。IDF San Francisco 2011で公開されたHaswell(写真=中央)。ラトナー氏は22ナノメートルプロセスルールを採用する将来のAtom“Silvermont”でも電圧変換回路をCPUに統合するという(写真=右)10ミリワットでPentiumを動かす!

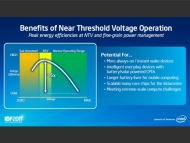

次に続くのは、ラトナー氏がIDF San Francisco 2011で披露した「ニアしきい電圧駆動技術」の実装だ。ここでいう「しきい電圧」とは、トランジスタを駆動できる最低限の電圧のことだ。トランジスタは一定の電圧を加えることでオンになり、それ以下の電圧ではオフになる。この動作を繰り返すことで、デジタル信号の“0”と“1”を生成する。しかし、現在のプロセッサでは、半導体のしきい電圧よりもかなり高い値を通常駆動電圧にしている。これは、ウエハから採れるチップごとにしきい電圧が異なることや、しきい電圧ぎりぎりの低電圧では、動作が安定しなかったりパフォーマンスがでないためだ。

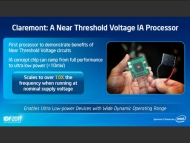

そこで、Intel Labsは、Socket 7のPentium(P54C)をベースにこの技術を実装した試作プロセッサ“Claremont”(クレアモント)で、当時15ワット前後で実現していた性能を、10ミリワット以下で実現できることを示している。IDF 2011の基調講演で行ったClaemontのデモで、小型ライトに照らされた太陽電池(インテルは切手サイズと表現したが、ラトナー氏は切手にしてはちょっと大きすぎるよね、と語っていた)で駆動し、3Dゲームや動画再生を行なったが、「Claremontでは電力効率を5倍に高めているが、CPUをニアしきい電圧技術に最適化してイチから設計すれば、電力効率を10倍以上高めることも可能だ」と説明する。

ニアしきい電圧技術開発のために試作されたPentiumベースのCPU“Claremont”。10ミリワット以下で動画再生などを可能にする(写真=左)。ニアしきい電圧技術では、より低電圧でもCPUが一定のパフォーマンスを発揮できるようにすることで、エネルギー効率を大幅に引き上げられる(写真=右)

ニアしきい電圧技術開発のために試作されたPentiumベースのCPU“Claremont”。10ミリワット以下で動画再生などを可能にする(写真=左)。ニアしきい電圧技術では、より低電圧でもCPUが一定のパフォーマンスを発揮できるようにすることで、エネルギー効率を大幅に引き上げられる(写真=右)

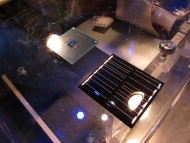

ニアしきい電圧技術のデモシステム。右側の太陽電池でCPUは駆動している(写真=左)。ニアしきい電圧技術のデモシステムの起動画面。BIOS上は“Pentium-S 66MHz”と認識されていた(写真=中央)。ニアしきい電圧技術のための試作プロセッサClaremontと、同CPUを駆動していた太陽電池(写真=右)

ニアしきい電圧技術のデモシステム。右側の太陽電池でCPUは駆動している(写真=左)。ニアしきい電圧技術のデモシステムの起動画面。BIOS上は“Pentium-S 66MHz”と認識されていた(写真=中央)。ニアしきい電圧技術のための試作プロセッサClaremontと、同CPUを駆動していた太陽電池(写真=右)Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- キーボード「FILCO」ブランドのダイヤテックが閉業 4月22日付で (2026年04月24日)

- 次期「DaVinci Resolve 21」で写真編集が可能に/Google Cloudが第8世代TPUを発表 (2026年04月26日)

- 大型連休前のアキバは新CPUラッシュ! AMD「Ryzen 9 9950X3D2」とIntel「Core Ultra 5 250K Plus/KF Plus」の気になる在庫状況 (2026年04月25日)

- 持ち運びを極めた超軽量キーボード「ロジクール KEYS TO GO 2」が17%オフの9980円に (2026年04月23日)

- ACアダプター不要の外付けHDD「Seagate One Touch Desktop External Hard Drive」を試す 超大容量で配線スッキリ (2026年04月24日)

- Windows 11の使い勝手はどう変わる? 「Copilot」名称外しやInsider Program再編に見るMicrosoftの本気度 (2026年04月24日)

- 2026年版Surfaceはどうなる? 正面衝突を避けるMicrosoft、10万円切り「MacBook Neo」対抗への秘策はあるか (2026年04月21日)

- 「Apple AirPods 4」が20%オフの2万3798円に (2026年04月24日)

- 部屋の雰囲気を一瞬で変えられる「SwitchBot RGBIC フロアライト」が15%オフの7633円に (2026年04月24日)

- 強力なドッキングステーション「Anker PowerExpand Elite 13-in-1 Thunderbolt 3 Dock」が28%オフの2万6490円に (2026年04月23日)