マルチコアから高性能コアで進化を目指すインテルのCPU:Sandy Bridgeは“12畳半”のはずだった(4/4 ページ)

目指すのは、2018年のエクサスケールHPC

さらにラトナー氏は、「しきい電圧ギリギリで駆動できるようにすれば、省電力性能を向上させるだけではなく、パフォーマンスも向上できる」と説明する。この技術をデスクトップPC向けのハイエンドCPUに活用した場合、しきい電圧から最大駆動電圧までのダイナミックレンジの広さを生かし、より高クロックで動作できるようになるというわけだ。インテルは、この技術を生かし、2018年にエクサFLOPS(10の16乗FLOPSの浮動小数点演算性能)を実現するスーパーコンピュータを実現する計画を明らかしているが、ラトナー氏は「ニアしきい電圧駆動技術は、クライアント向けCPUの省電力化にも役立つ」として、3〜5年後をめどに、同技術をノートPCやデスクトップ向けCPUにも応用していく姿勢を示す。

もう1つの段階は、CPUの演算性能を向上させることだ。同社はHPC向けにMIC(Many Integrated Core)を展開しており、32ナノメートルプロセスルールを採用し、50コアを統合した「Knights Corner」を発表している。同製品は50コアで1テラFLOPSの演算性能を実現しており、長期的にはこのメニーコア技術を一般のCPUにも統合することも検討している。

また、Intel LabsではGPUコアを使ったアクセラレーションのサポートも検討しており、2011年のIDFでは現行の“Sandy Bridge”世代のCore i7で内蔵するグラフィックスコア(Intel HD Graphics 3000)を使って、JavaScriptの高速化を実現するデモも公開した。ただし、メニーコア化やGPU利用を推進していく上では、CPUの作業領域となるメモリとのインタフェースを高速化することが不可欠となる。そこでインテルは、チップに小さな穴を開け、そこに電極となる金属を充填する「TSV」(Through Silicon Via:シリコン貫通電極)技術によって、より広い帯域でメモリチップをチップ上で接続する手法なども模索している。

シングルチップで1テラFLOPSの演算性能を実現したIntel MICアーキテクチャを採用する「Knights Corner」(写真=左、中央)。CPU内蔵グラフィックスコアを使ったJava Scriptのアクセラレーションも将来的にサポートされる(写真=右)

シングルチップで1テラFLOPSの演算性能を実現したIntel MICアーキテクチャを採用する「Knights Corner」(写真=左、中央)。CPU内蔵グラフィックスコアを使ったJava Scriptのアクセラレーションも将来的にサポートされる(写真=右)

GPUを使ったJavaScriptのアクセラレーションデモとして宇宙空間における星々の干渉のしかたをシミュレーションする「N-Body」をFirefox上で動作させた。LGA 1155版Core i7 2600KのCPUのみを利用した場合でフレームレートはわずか3fpsしか出ていないが(写真=左)、GPUコアを並列処理に利用するRiver Trailを利用することで、同じCPUでも内蔵GPUも利用して45fpsのフレームレートを実現できるという(写真=中央)。TSV技術を使ってCPUチップ上にDRAMチップを直接搭載するHybrid memory Cube技術。同技術を使えばDDR3 DRAMを使用しても128Gバイト/秒の広帯域を確保できるという(写真=右)

GPUを使ったJavaScriptのアクセラレーションデモとして宇宙空間における星々の干渉のしかたをシミュレーションする「N-Body」をFirefox上で動作させた。LGA 1155版Core i7 2600KのCPUのみを利用した場合でフレームレートはわずか3fpsしか出ていないが(写真=左)、GPUコアを並列処理に利用するRiver Trailを利用することで、同じCPUでも内蔵GPUも利用して45fpsのフレームレートを実現できるという(写真=中央)。TSV技術を使ってCPUチップ上にDRAMチップを直接搭載するHybrid memory Cube技術。同技術を使えばDDR3 DRAMを使用しても128Gバイト/秒の広帯域を確保できるという(写真=右)それもこれも自社工場があるから可能になる

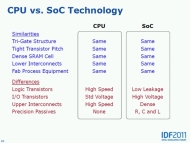

Intelが、こうした技術革新を続けられるのも、半導体製造施設を自社で持ち、最新技術に最適なプロセスルールの開発ができることが大きい。2012年第1四半期末〜第2四半期初に市場投入が計画されている次期主力CPUの“Ivy Bridge”で3Dトライゲートトランジスタ技術を初めて投入する22ナノメートルプロセスルールに適用できたのも、2006年に45ナノメートルプロセスルールの立ち上げにおいて、SRAMチップの試作で3Dトライゲートトランジスタ技術を採用し、この技術を使った半導体の量産に向けて研究を重ねるなど、製造技術の確立にも5年を費やしてきたからだ。

3Dトライゲートトランジスタの開発は2002年にスタートし、2006年には45ナノメートルプロセスルールの立ち上げ時におけるSRAMチップの試作で、すでに同技術を採用していた(写真=左)。インテルの半導体製造ロードマップ。同社は最先端プロセスの採用や3Dトライゲートトランジスタなどの先端技術において、競合他社に比べ3年以上のアドバンテージを保っているとアピールする(写真=中央)。22ナノメートルトライゲートトランジスタプロセスルールでは、よりリーク電力が低いSoC向けプロセスも立ち上げられ、Atomなどに採用する(写真=右)

3Dトライゲートトランジスタの開発は2002年にスタートし、2006年には45ナノメートルプロセスルールの立ち上げ時におけるSRAMチップの試作で、すでに同技術を採用していた(写真=左)。インテルの半導体製造ロードマップ。同社は最先端プロセスの採用や3Dトライゲートトランジスタなどの先端技術において、競合他社に比べ3年以上のアドバンテージを保っているとアピールする(写真=中央)。22ナノメートルトライゲートトランジスタプロセスルールでは、よりリーク電力が低いSoC向けプロセスも立ち上げられ、Atomなどに採用する(写真=右)振り返れば、インテルはシングルコアで4つのスレッドを実行できる拡張版Hyper Threadingを採用するとされた第5世代のPentium 4プロセッサ“Tejas”(開発コード名)で2005年の市場投入を計画していた。しかし、リーク電流に起因する消費電力の増大などを理由にキャンセルしている。このことがきっかけとなって、CPUのロードマップをマルチコアへ転換せざるを得ない状況となった。

そのころ研究が本格的にスタートしたCMOS電圧レギュレータや3Dトライゲートトランジスタ技術が、ようやく実用化したことで、インテルのCPUロードマップは、再び高性能化のペースを取り戻すことも期待できる。実際、ラトナー氏は「22ナノメートルプロセスにおける3Dトライゲートトランジスタ技術の確立で、今後もムーアの法則を堅持できる。さらにHigh-Kに代わる新素材の研究が進めば、半導体プロセスの進化をペースアップすることも可能だ」と今後の半導体の進化に自信を見せる。同氏は、2ワットで100ギガFLOPSの性能を実現するモバイルシステムも、早ければ2018年には実現できると見ており、CPUは次の40年に向けて、より低消費電力なものから、より高性能な製品まで、さらに幅広い進化が期待できるようになりそうだ。

関連記事

20メガワットエクサスケールは破壊的イノベーションで実現する

20メガワットエクサスケールは破壊的イノベーションで実現する

HPCで必要なエクサスケースコンピュータでは、消費電力の抑制が必須だ。NVIDIAは、GPUコンピューティングによる“脱CPU依存”がHPCの進化に不可欠と訴える。 Gen.3とX79とSandy Bridge-Eの関係

Gen.3とX79とSandy Bridge-Eの関係

COMPUTEX TAIPEI 2011に続いて登場したIntel X79 Expressチップセット搭載マザーボード。MSIは一気に3モデルを公開。とはいえ、展示は多いけれど謎は深い。 エクサスケールは2018年に来る!

エクサスケールは2018年に来る!

インテルが同社のデータセンター事業に関する説明会を行い、その中で、次世代Xeon、Itaniumのほか、インテル MIC アーキテクチャについて言及した。 Intelの研究成果が集結!──「Research@Intel Day June 2011」

Intelの研究成果が集結!──「Research@Intel Day June 2011」

自作PCユーザーが注目するインテルのロードマップ。そのロードマップの先を進むのがインテルの研究機関だ。彼らの成果が集合するイベントで「その先」が見えるか? 米Intel、“Ivy Bridge”で「3D-Tri Gate」を採用

米Intel、“Ivy Bridge”で「3D-Tri Gate」を採用

米Intelは、Sandy Bridgeの後継となる“Ivy Bridge”において、3D-Tri Gateが採用されることを明らかにし、動作する“Ivy Bridge搭載PC”も公開した。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- キーボード「FILCO」ブランドのダイヤテックが閉業 4月22日付で (2026年04月24日)

- 次期「DaVinci Resolve 21」で写真編集が可能に/Google Cloudが第8世代TPUを発表 (2026年04月26日)

- 大型連休前のアキバは新CPUラッシュ! AMD「Ryzen 9 9950X3D2」とIntel「Core Ultra 5 250K Plus/KF Plus」の気になる在庫状況 (2026年04月25日)

- 持ち運びを極めた超軽量キーボード「ロジクール KEYS TO GO 2」が17%オフの9980円に (2026年04月23日)

- ACアダプター不要の外付けHDD「Seagate One Touch Desktop External Hard Drive」を試す 超大容量で配線スッキリ (2026年04月24日)

- Windows 11の使い勝手はどう変わる? 「Copilot」名称外しやInsider Program再編に見るMicrosoftの本気度 (2026年04月24日)

- 「Apple AirPods 4」が20%オフの2万3798円に (2026年04月24日)

- 2026年版Surfaceはどうなる? 正面衝突を避けるMicrosoft、10万円切り「MacBook Neo」対抗への秘策はあるか (2026年04月21日)

- 部屋の雰囲気を一瞬で変えられる「SwitchBot RGBIC フロアライト」が15%オフの7633円に (2026年04月24日)

- 強力なドッキングステーション「Anker PowerExpand Elite 13-in-1 Thunderbolt 3 Dock」が28%オフの2万6490円に (2026年04月23日)