NVIDIAの最新アーキテクチャ“Maxwell”を徹底解説:Keplerと何が違う?(1/3 ページ)

メインストリームで新アーキテクチャを投入

ついに、NVIDIAが新アーキテクチャ“Maxwell”ベースのGPUを市場投入する。ただし、これまでの同社の戦略と大きく異なるのは、メインストリーム市場向け製品で最初に新しいアーキテクチャを採用したことだ。

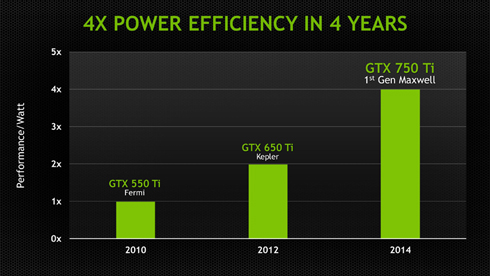

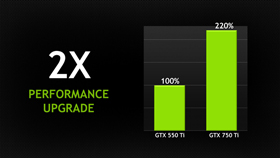

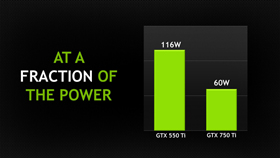

同社でGeForce製品を担当するジャスティン・ウォーカー氏(Justin Walker、GeForce Senior Product Manager)は、「“第1世代”のMaxwellは、Keplerが実現した消費電力あたりのパフォーマンスをさらに向上させたアーキテクチャ」と位置づける。

そのカギとなるのが、CUDAコアクラスタとなるSM(Streaming Multiprocessor)の構成を見直し、CUDAコアの利用効率を高めることで、大幅なパフォーマンスアップと省電力性の維持を実現した点だ。

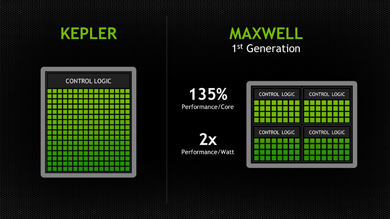

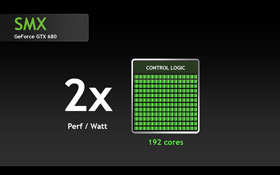

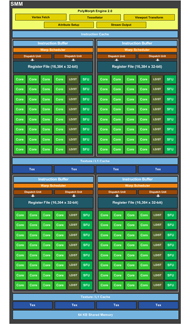

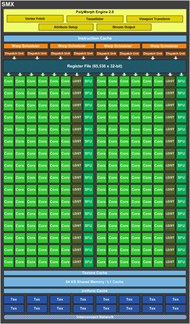

Maxwellアーキテクチャでは、Keplerが192基のCUDAコアでSMXを構成していたのに対し、128基のCUDAコアをプロセシングブロック(PB)と呼ぶ32コアごと、4つのパーティションに分け、それぞれのプロセシングブロックにコントロールロジックとなるWarpスケジューラと2つの命令発行ユニット(ディスパッチユニット)、64Kバイト(16384×32ビット)のレジスタファイルを持ち、命令発行の効率化を図るとともに、プロセシングブロックごとにクロック制御をすることで、低負荷時の省電力化を図りやすくする。

MaxwellアーキテクチャのSMM構成。128基のCUDAコアを4つのプロセシングブロックに分けている(写真=左)。KeplerアーキテクチャのSMX構成。192基のCUDAコアを1つのクラスタにまとめている(写真=右)

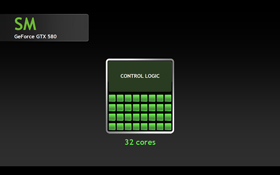

MaxwellアーキテクチャのSMM構成。128基のCUDAコアを4つのプロセシングブロックに分けている(写真=左)。KeplerアーキテクチャのSMX構成。192基のCUDAコアを1つのクラスタにまとめている(写真=右)この32 CUDAコアという構成は、“数”だけを見れば、GeForce GTX 280で採用した“Fermi”フェルミアーキテクチャと同じだ。しかし、SMのクロック制御はKeplerと同じ単一クロック動作をベースとしており、スケジューリングに関してもKepler同様ソフトウェア制御を多用するもので、Fermi世代とは大きく構成が異なる。

特に超越関数演算に用いるスペシャルファンクションユニット(Special Function Unit:SFU)や、ロード・ストアユニット(Load/Store Unit:LD/ST)の割合は、Kepler世代よりも増えていることが、下の表からも見て取れるだろう。

L1キャッシュはテクスチャキャッシュと共用する一方、4つのプロセシングブロックが共用するユニファイドメモリを搭載するデザインに変更されており、Fermiや同社初のCUDA GPUとなったG80世代に採用した手法に立ち返った部分もある。

| SMM/SMX構成比較 | ||

|---|---|---|

| アーキテクチャ | Maxwell Gen.1 | Kepler |

| プロセス技術 | TSMC 28nm | TSMC 28nm |

| CUDAコア | 128 | 192 |

| プロセシング・ブロック(パーティション) | 32コア×4 | ー |

| Warpスケジューラ | 4 (1×4) | 4 |

| 命令発行ユニット(ディスパッチユニット) | 8 (2×4) | 8 |

| スペシャルファンクションユニット(SFU) | 32基(8×4) | 32基 |

| ロード・ストアユニット | 32基(8×4) | 32基 |

| レジスタファイル | 256KB (64KB:16,384×32bit×4) | 256KB (65,536×32bit) |

| テクスチャユニット | 8 | 16 |

| PolyMorph Engine | 1 | 1 |

ウォーカー氏によれば、Maxwellに採用したCUDAコアや、SFUなどは、基本的にKepler世代と同じものであり、テッセレータなどを統合するジオメトリ処理用の固定ファンクションユニットのPolyMorph Engineも手は加えられていないという。

その意味では、“第1世代”のMaxwellアーキテクチャは、同社のモバイルSoC「Tegra K1」への実装も果たしたKeplerアーキテクチャの省電力性能を、さらに突き詰めた改良版アーキテクチャという色が濃いようにも感じる。

実際、ウォーカー氏は「“第1世代”のMaxwellコアとなるGK107では、消費電力あたりのパフォーマンスを追究することを最優先に開発が進められた」としており、パフォーマンスを最大限に引き出すことよりも、エネルギー効率を高めることを優先したことが分かる。

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- 発表時の批判は裏返る? スペック据え置きでも“買い”と言える、極上の普段着スマホ「Pixel 10a」を触ってみた (2026年04月27日)

- サイボウズの社名由来 “坊主”に込められた意味が深すぎる (2016年07月29日)

- キーボード「FILCO」ブランドのダイヤテックが閉業 4月22日付で (2026年04月24日)

- マザーボードは「細部まで白」が今の主流? 高コスパ水冷など見逃せない最新自作PCパーツ事情 (2026年04月27日)

- 大型連休前のアキバは新CPUラッシュ! AMD「Ryzen 9 9950X3D2」とIntel「Core Ultra 5 250K Plus/KF Plus」の気になる在庫状況 (2026年04月25日)

- 次期「DaVinci Resolve 21」で写真編集が可能に/Google Cloudが第8世代TPUを発表 (2026年04月26日)

- エレコム、士郎正宗デザインマウス「M.A.P.P.」復刻モデルの予約販売を4月6日に開始 (2026年03月25日)

- エレコム、「士郎正宗 復刻マウス」発売日を延期 5月下旬の予定に (2026年04月27日)

- 持ち運びを極めた超軽量キーボード「ロジクール KEYS TO GO 2」が17%オフの9980円に (2026年04月23日)

- 部屋の雰囲気を一瞬で変えられる「SwitchBot RGBIC フロアライト」が15%オフの7633円に (2026年04月24日)