クアッドコアは11月に登場、80コア搭載CPUのプロトタイプも公開──オッテリーニ氏基調講演:IDF Fall 2006(2/3 ページ)

クアッドコアの次はメニーコアに。80コアのプロトタイプを公開

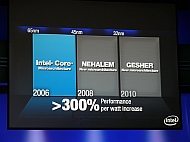

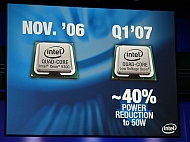

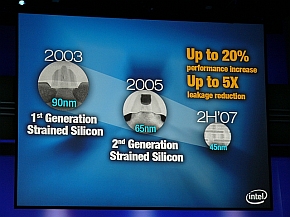

オッテリーニ氏はクアッドコアCPUの発表に続けて、2007年以降のロードマップについて言及した。インテルは2005年後半に65ナノメートルプロセスルールを採用したCPUをリリースして以来、デュアルコアベースの低消費電力プロセッサ「Core Duo」を2006年初頭に、さらに低消費電力とパフォーマンスを強化した新アーキテクチャの「Core2 Duo」を2006年夏にリリースしている。Core2 Duoのアーキテクチャは65ナノプロセスルールによる製造が行われる2007年いっぱいまで用いられることになり、2007年後半の45ナノプロセスルールを採用した製品の登場を持って新アーキテクチャへと移行する。2008年以降の45ナノプロセスルール世代では「Nehalem」(ネハーレム)、2010年以降の32ナノプロセスルール世代では「Gesher」(ゲシャー)と、ほぼ2年おきのペースでアーキテクチャが入れ替わることになる。

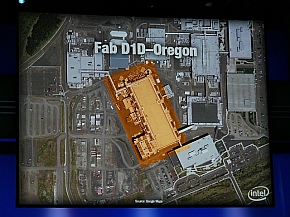

「現時点で、すでに65ナノプロセスルールのCPUがインテルから4000万個出荷されている。だが業界他社が出荷した65ナノプロセスルールのCPUはゼロだ。プロセス技術の面で、インテルが依然として業界をリードしており、現在米オレゴン州にあるFab D1Dを皮切りに、米アリゾナ州のFab 32、イスラエルのFab 28と、45ナノプロセスルールの時代でも業界をリードしていくことになるだろう」とオッテリーニ氏はインテルの優位な立場を強調する。同氏によれば、45ナノプロセスルールをベースにした15種類の製品開発が現在行われているという。

最近、インテルがよく掲げるキーワードに「テラスケールコンピューティング」がある。順調なプロセス技術の移行とクアッドコアにみられるコアの多重化は、このテラスケールコンピューティング時代を予感させる。

テラスケールコンピューティングとは、テラバイト級のデータをテラフロップス(TFLOPS)の速度で処理するアーキテクチャの総称である。同社は今後数年をかけて段階的にCPUのコア数を増やし、このテラスケールコンピューティングへと近づこうとしている。

オッテリーニ氏は、1つのダイ上に80のコアを搭載したテラスケールコンピューティング時代CPUのプロトタイプウェハを公開た。ダイスタッキングによるキャッシュメモリとの高速インターコネクトなど、研究段階の技術が多数詰め込まれている。オッテリーニ氏は今後プロセス技術が移り変わる4〜5年のスパンで、PCアーキテクチャがテラスケールの時代に到達する準備が整いつつあることを示した。

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- ワコムが有機ELペンタブレットをついに投入! 「Wacom Movink 13」は約420gの軽量モデルだ (2024年04月24日)

- わずか237gとスマホ並みに軽いモバイルディスプレイ! ユニークの10.5型「UQ-PM10FHDNT-GL」を試す (2024年04月25日)

- 「社長室と役員室はなくしました」 価値共創領域に挑戦する日本IBM 山口社長のこだわり (2024年04月24日)

- QualcommがPC向けSoC「Snapdragon X Plus」を発表 CPUコアを削減しつつも圧倒的なAI処理性能は維持 搭載PCは2024年中盤に登場予定 (2024年04月25日)

- 「Surface Go」が“タフブック”みたいになる耐衝撃ケース サンワサプライから登場 (2024年04月24日)

- 16.3型の折りたたみノートPC「Thinkpad X1 Fold」は“大画面タブレット”として大きな価値あり (2024年04月24日)

- AI PC時代の製品選び 展示会「第33回 Japan IT Week 春」で目にしたもの AI活用やDX化を推進したい企業は要注目! (2024年04月25日)

- あなたのPCのWindows 10/11の「ライセンス」はどうなっている? 調べる方法をチェック! (2023年10月20日)

- アドバンテック、第14世代Coreプロセッサを採用した産業向けシングルボードPC (2024年04月24日)

- マウス、GeForce RTX 3050を搭載したスリム/ミニタワーPCの販売を開始 (2024年04月25日)