NVIDIAが最新GPU/モバイルSoCのロードマップを披露――GTC 2014基調講演まとめ:Pascal、Erista、TITAN Z(1/3 ページ)

NVIDIAは、3月24日〜27日4日間、米カリフォルニア州サンノゼ市のSan Jose McEnery Convention Centerにおいて、GPUに関する技術会議「GPU Technology Conference 2014」(GTC 2014)を開催中だ。その2日目の3月25日にオープニングキーノートに登場したジェンスン・ファンCEOは、同社の最新GPUロードマップやSoCロードマップを披露するとともに、PCやスーパーコンピューターだけでなく、自動車分野などにも積極的にGPUの持つ優れたコンピューティング性能を生かせるプラットフォームを展開していく意向を示した。

GTC 2014の会場となったSan Jose McEnery Convention Center(写真=左)。オープニングキーノートで同社のCUDAエコシステム戦略を説明するジェンスン・ファンCEO(写真=右)

GTC 2014の会場となったSan Jose McEnery Convention Center(写真=左)。オープニングキーノートで同社のCUDAエコシステム戦略を説明するジェンスン・ファンCEO(写真=右)80Gバイト/秒の帯域を実現する「NVLINK」でCPU−GPU間のボトルネックを解消

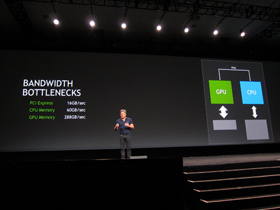

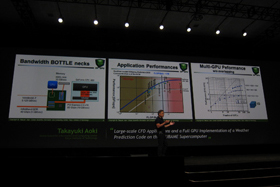

ファン氏はまず、同社独自のGPUコンピューティング言語「CUDA」を取り上げ、CPU+GPUの組み合わせは、CPUの持つ柔軟な演算能力とGPUの持つ強力な並列演算性能を生かせる完璧なソリューションと位置づける一方で、GPUコンピューティングのパイオニアでもある東京工業大学の青木尊之教授の論文を紹介しつつ、「ビッグデータや複雑な演算処理を行なううえでは、CPUとGPU間のデータ帯域の狭さがボトルネックになっている」と指摘。CPU−GPU間のインタフェースとなっているPCI Express 3.0 x16の16Gバイト/秒、システムメモリ帯域の60Gバイト/秒、GPUメモリの288Gバイト/秒というアンバランスさが、CPUとGPUの密なる連係を阻んでいると説明する。そこで、同社の次世代GPUアーキテクチャでは、「NVLINK」と呼ぶ、新しいCPU−GPUインタフェースを採用する意向を表明した。

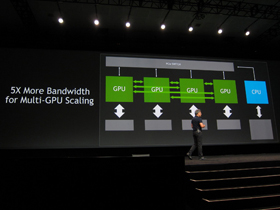

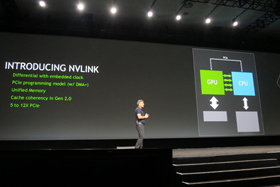

NVLINKは、IBMと共同開発したオプティカルインタフェースで、PCI Express 3.0 x16の5倍となる80Gバイト/秒の帯域を実現するもの。基本的にPCI ExpressやDMA(Direct Memory Access)を拡張するカタチで実装され、差動信号にクロック信号を埋め込むことで、より高速なインタフェースを実現し、CPUとGPUが共通のメモリ空間に効率よくアクセスできるようにする。

むろん、同技術をサポートするためには、CPU側の対応も不可欠となるため、最初の対応プラットフォームはIBMのPower CPU環境となるが、「ほかのCPUへの対応も話し合っている」(同社関係者)という状況だ。NVLINKでは複数のGPU間のデータ共有にも生かすことができる。

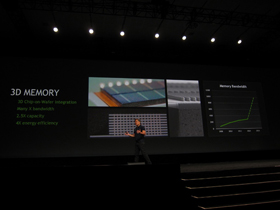

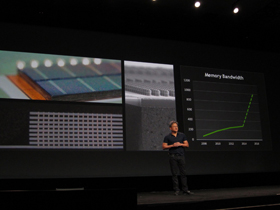

また、ファン氏は、このNVLINKの第2世代ではCPUとGPUのキャッシュコヒーレンシをハードウェアで採れるようにするとともに、192Gバイト/秒の帯域を実現する計画であることも明らかにした。さらにファン氏は、次世代GPUでは複数のメモリダイをTSV(Through Silicon Via:シリコン貫通電極)で積層することで、広帯域かつ大容量で、エネルギー効率にも優れた3Dメモリを採用する意向を明らかにした。

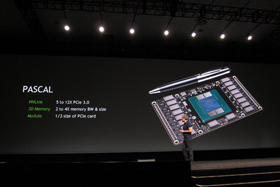

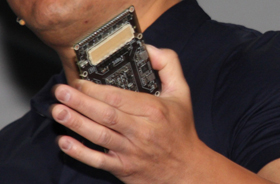

ファン氏はその次世代GPUアーキテクチャにフランスの自然哲学者で、近代物理学の先駆者とされるブレーズ・パスカル(Blaise Pascal)から“Pascal”というコードネームを与えることを明らかにし、同GPUに対応したモジュールも披露した。

同モジュールは、現行のPCI Expressベースのグラフィックスカードに比べて3分の1というコンパクトなフォームファクターで、背面にはNVLINKと電源供給用と考えられる高密度コネクタを2つ搭載していた。

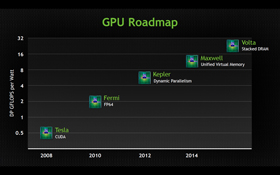

ただし、同モジュールはあくまでもNVLINKなどのエンジニアリング用のモジュールであり、搭載されているチップはPascalとは別物と考えるべきだ。なお、ファン氏は、このPascalを2016年に市場投入する意向を示すとともに、最新GPUロードマップを公開している。

NVLinkや3Dメモリの動作検証用に作られたPascalモジュール。ただしGPUそのものはPascalではない(写真=左)。Pascalモジュールの裏面にはNVLinkと電源供給のための高密度コネクタが2つ搭載していることが確認できる(写真=右)

NVLinkや3Dメモリの動作検証用に作られたPascalモジュール。ただしGPUそのものはPascalではない(写真=左)。Pascalモジュールの裏面にはNVLinkと電源供給のための高密度コネクタが2つ搭載していることが確認できる(写真=右)このロードマップで注目すべきは、2013年のGTCで公開された「Volta」(ヴォルタ)が「Pascal」に置き換えられたように見える点だが、複数のNVIDIA関係者は「Volta」は、いまもロードマップに留まっているという見解を示す。

また、Pascalの目玉となるNVLINKと、今回披露された「Pascalモジュール」は、あくまでもスーパーコンピュータやデータセンター向けなどのHPC(High Performance Computer)向けにTeslaとして展開予定のフォームファクターであり、PC向けにはPCI Expressベースの製品も用意される。

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- 発表時の批判は裏返る? スペック据え置きでも“買い”と言える、極上の普段着スマホ「Pixel 10a」を触ってみた (2026年04月27日)

- サイボウズの社名由来 “坊主”に込められた意味が深すぎる (2016年07月29日)

- キーボード「FILCO」ブランドのダイヤテックが閉業 4月22日付で (2026年04月24日)

- マザーボードは「細部まで白」が今の主流? 高コスパ水冷など見逃せない最新自作PCパーツ事情 (2026年04月27日)

- 大型連休前のアキバは新CPUラッシュ! AMD「Ryzen 9 9950X3D2」とIntel「Core Ultra 5 250K Plus/KF Plus」の気になる在庫状況 (2026年04月25日)

- 次期「DaVinci Resolve 21」で写真編集が可能に/Google Cloudが第8世代TPUを発表 (2026年04月26日)

- エレコム、士郎正宗デザインマウス「M.A.P.P.」復刻モデルの予約販売を4月6日に開始 (2026年03月25日)

- エレコム、「士郎正宗 復刻マウス」発売日を延期 5月下旬の予定に (2026年04月27日)

- 持ち運びを極めた超軽量キーボード「ロジクール KEYS TO GO 2」が17%オフの9980円に (2026年04月23日)

- 部屋の雰囲気を一瞬で変えられる「SwitchBot RGBIC フロアライト」が15%オフの7633円に (2026年04月24日)