SSDの容量、性能、耐久性、電力効率を高める「3D V-NAND」とは何か?:NANDフラッシュは1Tビット時代へ(2/4 ページ)

» 2014年07月11日 13時30分 公開

[鈴木雅暢,ITmedia]

一戸建てから高層マンションへ

3D V-NANDについての技術解説は、ジム・エリオット氏に紹介されて登壇したキーヒュン・キョン氏が行った。同氏は、NANDフラッシュメモリにおけるプロセスルールの微細化、高記録密度化の歴史を振り返りつつ、現在の1xnm(nmはナノメートル)世代やその先のプロセスルールの問題点を指摘した。

なお、「1xnm」というのは業界独特の呼び方で、19nm前後のプロセスルールをいう。「1ynm」がより微細な16nm前後、「1znm」がその先の10nm台前半のプロセスルールを指している。

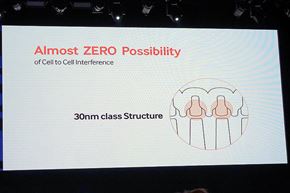

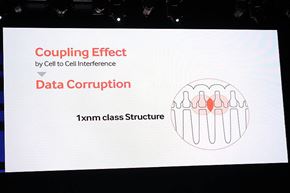

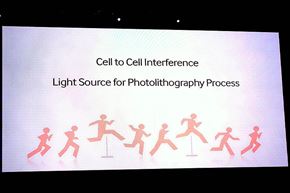

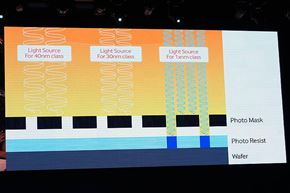

同氏が、微細化に伴う問題として指摘するのが、セル間の電気的干渉と露光装置だ。電気的干渉はすでに1xnmクラスでも深刻な課題となっており、書き込みを行う際には、コントローラに複雑なエラー訂正アルゴリズムが必要としている。また、微細化を進めると回路パターンが狭くなるため、より短波長レーザーを使った高価な露光装置が必要になるとした。

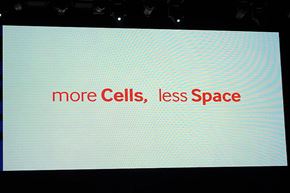

キーヒュン・キョン氏(フラッシュメモリ設計の担当上級副社長)は、3D V-NAND技術を解説した(写真=左)。NANDフラッシュメモリ容量を増大させるカギは、いかに小さいスペースに、より多くのメモリセルを実装するかだ(写真=右)

キーヒュン・キョン氏(フラッシュメモリ設計の担当上級副社長)は、3D V-NAND技術を解説した(写真=左)。NANDフラッシュメモリ容量を増大させるカギは、いかに小さいスペースに、より多くのメモリセルを実装するかだ(写真=右)

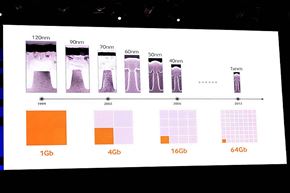

NANDフラッシュは1999年の120nm以来、微細化を続け、1xnm(19nm前後)では64Gビット、128Gビットへと記録密度を向上させてきた(写真=左)。微細化には2つの課題がある(写真=右)。セル間の電気的な干渉、そして露光装置のレーザーだ

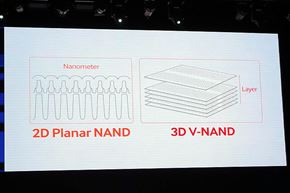

NANDフラッシュは1999年の120nm以来、微細化を続け、1xnm(19nm前後)では64Gビット、128Gビットへと記録密度を向上させてきた(写真=左)。微細化には2つの課題がある(写真=右)。セル間の電気的な干渉、そして露光装置のレーザーだその課題を根本的に解決するのが3次元構造であり、同社が世界に先駆けて実用化した3D V-NANDだ。同氏はNANDフラッシュを住居に例え、従来のNAND構造は一戸建て、3D V-NANDは高層マンションのようなものだと説明した。

限られた土地にたくさんの一戸建てを建てれば、必然的に1つ1つの家の大きさ、間隔とも小さくなり、隣り合う家に入居した世帯同士で騒音問題などのトラブルが発生しやすくなる。NANDフラッシュメモリにおけるセル間干渉はそれに相当するという。

一方、高層ビルのように垂直方向に積み上げれば、一世帯あたりの居住面積、間隔とも小さくすることなく、たくさんの世帯が入居できる。

1xnmでの電気的な干渉によるデータ汚染、それはお互いの家のすぐ隣にうるさい騒音を立てる隣人がいるようなものだ(写真=左)。微細化を進めると、従来の波長のレーザーでは露光ができず、より短い波長のレーザーを使った高価な露光装置が必要になる(写真=右)

1xnmでの電気的な干渉によるデータ汚染、それはお互いの家のすぐ隣にうるさい騒音を立てる隣人がいるようなものだ(写真=左)。微細化を進めると、従来の波長のレーザーでは露光ができず、より短い波長のレーザーを使った高価な露光装置が必要になる(写真=右)

その課題を解決するのが、3次元構造であり、3D V-NANDだ(写真=左)。従来は平面のまま細かく区切ることでセルを増やしていたが、3D V-NANDでは垂直方向にセルを積むことでセルを増やせる。従来のNAND構造を一戸建てに例えると、土地は限られており、1つ1つの家は小さくせざるを得ないため、さまざまなトラブルが発生する(写真=右)。3D V-NANDでは高層マンションのように垂直方向にセルを形成するため、そういったトラブルなしに入居者を増やせる

その課題を解決するのが、3次元構造であり、3D V-NANDだ(写真=左)。従来は平面のまま細かく区切ることでセルを増やしていたが、3D V-NANDでは垂直方向にセルを積むことでセルを増やせる。従来のNAND構造を一戸建てに例えると、土地は限られており、1つ1つの家は小さくせざるを得ないため、さまざまなトラブルが発生する(写真=右)。3D V-NANDでは高層マンションのように垂直方向にセルを形成するため、そういったトラブルなしに入居者を増やせるCopyright © ITmedia, Inc. All Rights Reserved.

SpecialPR

SpecialPR

アクセストップ10

2026年04月07日 更新

- NVIDIAが「G-SYNC Pulsar」対応ディスプレイを日本初披露 何がすごい? (2026年04月06日)

- メモリ高騰でRaspberry Piが再値上げ/Adobe CCがユーザーに無断でhostsファイルを書き換え? (2026年04月05日)

- アキバの一部ショップでHDD購入制限の動き――大容量モデルを中心に品薄感 (2026年04月04日)

- 待望の「Core Ultra 7 270K Plus」は静かな船出――アキバでは激安ピラーレスケースなど“高コスパ”パーツに熱視線 (2026年04月06日)

- 迷走の5年間を経て――MicrosoftがWindows 11の“不都合な真実”を認め、改善を宣言した背景 (2026年04月01日)

- Googleが最新オープンAIモデル「Gemma 4」を公開 (2026年04月06日)

- Windows 11(24H2/25H2)の3月オプション更新でインストールできないトラブル 「帯域外更新」で対処 (2026年04月02日)

- 「10歳でもプロを目指せる」――マウスコンピューター軣社長が語る、eスポーツ支援の理由とゲーミングPCの未来 (2026年04月06日)

- 安いMacは「使えない」? MacBook Neo 8GBモデルで試す、後悔しないための活用術と注意点 (2026年04月02日)

- デジタル化もできるレコードプレーヤー「オーディオテクニカ AT-LP120XBT-USB」が20%オフの4万4000円に (2026年04月03日)

最新トピックスPR