大解説! “Broadwell-Y”な「Core M」はここがすごい(後編):これはもうTickじゃない(1/2 ページ)

低電圧駆動でも高クロック動作を可能にするCore M

8月11日(現地時間)、同社の次世代半導体製造技術となる14ナノメートルプロセスルールと、このプロセスルールを採用する次世代CPU「Core M」(開発コード名「Broadwell-Y」)の概要を明らかにした。

前回は、14ナノメートルプロセスルールの特徴を、第2世代のトライゲートを中心に解説した。今回は、この14ナノメートルプロセスルールを採用するCore Mの概要を紹介する。

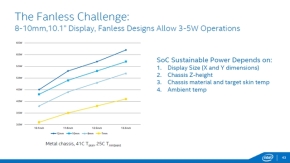

Intelで、Core Mのアーキテクチャ開発を担当するIntel プラットフォームエンジニアリンググループ システム オン チップアーキテクチャ責任者でIntel フェローのステファン・ジョルダン氏は、「10.1型ディスプレイを搭載するデバイスで8〜10ミリ厚のファンレスデザインを実現しようとすると、SoCの消費電力は3〜5ワットにする必要がある」と説明する。

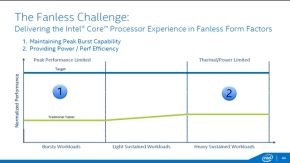

その一方で、Coreプロセッサー・ファミリーで、ピーク性能や高負荷が持続する環境でも優れた性能を発揮できるよう、消費電力あたりのパフォーマンスを追究する必要があったとしたうえで、次に掲げる改善を行うことで、低消費電力、かつ、パワフルなSoCを実現したという。

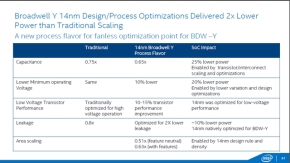

- 14ナノメートルプロセスルールの採用とSoC設計の最適化

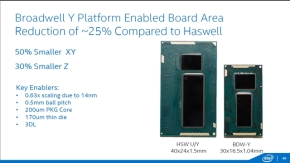

- SoCパッケージやフォームファクタの改良

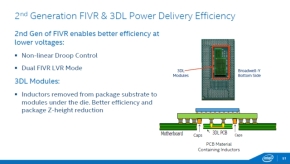

- 第2世代FIVR(Fully Integrated Voltage Regulator)と3DLテクノロジの採用

- パワーマネジメント機能の拡張

- よりアグレッシブな消費電力削減

10.1型ディスプレイで8〜10ミリ厚のファンレスデザインを実現しようとすると、SoCの消費電力は3〜5ワットにする必要がある(写真=左)。ファンレスシステムにCoreプロセッサーファミリーと同等の性能を持たせるには、ピーク性能だけでなく、持続的に負荷がかかる状態でも一定以上の処理能力を発揮できる消費電力あたりのパフォーマンスを実現する必要がある(写真=右)

10.1型ディスプレイで8〜10ミリ厚のファンレスデザインを実現しようとすると、SoCの消費電力は3〜5ワットにする必要がある(写真=左)。ファンレスシステムにCoreプロセッサーファミリーと同等の性能を持たせるには、ピーク性能だけでなく、持続的に負荷がかかる状態でも一定以上の処理能力を発揮できる消費電力あたりのパフォーマンスを実現する必要がある(写真=右)14ナノメートルプロセスルールへの最適化については、「低電圧駆動時に高いパフォーマンスを発揮できるように設計しており、リーク電流も従来の半分に低減した。、それだけでも消費電力を10%低くできる」と説明する。さらに、駆動電圧の低減によりトランジスタ駆動電力も大幅に低減しており、通常の微細化に比べて、倍の省電力化(半分の消費電力)を実現した。

Core Mは14ナノメートルプロセスルールの採用により、機能拡張を施しながらも、Haswell-Yと比べてダイサイズを63%微細化しただけでなく、SoCパッケージのサイズ(面積)も半分に、厚さも30%ほど薄くすることで、より薄いシステムの構築をサポートする。

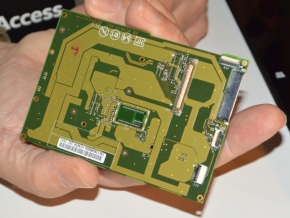

CPUコアに統合した電圧変換回路(FIVR)は、第2世代に進化した。こちらも低電圧動作に最適化するとともに、これまでは、SoCの裏に実装されていたインダクタを別の基板でSoCパッケージの裏に実装する3DL技術(Lはインダクタンスを示す記号。レンツの法則のHeinrich Lenz氏の頭文字が起源)を採用することで、チップサイズが小さくなっても一定の電力をまかなえるコンデンサやインダクタを搭載できるようにしている。

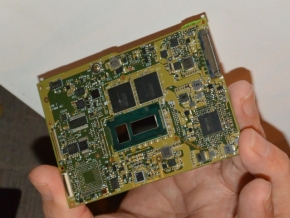

また、チップの高さを抑える一助にもしている。この3DLは、COMPUTEX TAIPEI 2014で公開したLama Mountainのシステム基板でも確認できる。

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- 発表時の批判は裏返る? スペック据え置きでも“買い”と言える、極上の普段着スマホ「Pixel 10a」を触ってみた (2026年04月27日)

- サイボウズの社名由来 “坊主”に込められた意味が深すぎる (2016年07月29日)

- キーボード「FILCO」ブランドのダイヤテックが閉業 4月22日付で (2026年04月24日)

- マザーボードは「細部まで白」が今の主流? 高コスパ水冷など見逃せない最新自作PCパーツ事情 (2026年04月27日)

- 大型連休前のアキバは新CPUラッシュ! AMD「Ryzen 9 9950X3D2」とIntel「Core Ultra 5 250K Plus/KF Plus」の気になる在庫状況 (2026年04月25日)

- 次期「DaVinci Resolve 21」で写真編集が可能に/Google Cloudが第8世代TPUを発表 (2026年04月26日)

- エレコム、士郎正宗デザインマウス「M.A.P.P.」復刻モデルの予約販売を4月6日に開始 (2026年03月25日)

- エレコム、「士郎正宗 復刻マウス」発売日を延期 5月下旬の予定に (2026年04月27日)

- 持ち運びを極めた超軽量キーボード「ロジクール KEYS TO GO 2」が17%オフの9980円に (2026年04月23日)

- 部屋の雰囲気を一瞬で変えられる「SwitchBot RGBIC フロアライト」が15%オフの7633円に (2026年04月24日)