AMDのデータセンター向けGPU「Instinct MI350シリーズ」って? 歴史と構造、シリコンなどをチェック!(2/2 ページ)

新製品「Instinct MI350シリーズ」の概要

最新のCDNA 4アーキテクチャを採用したGPUは「Instinct MI350シリーズ」として展開される。製品は空冷タイプの「Instinct MI350X」と、水冷タイプの「Instinct MI355X」の2種類だ。

詳細は後述するが、2モデル共にハードウェア的な大きな違いは無い。しかし、水冷タイプのMI355Xの方がより高い動作クロックで動作し、性能も10〜15%ほど高くなる。その代わり、1枚当たりの最大消費電力(TBP)はMI350Xが1000W、MI355Xが1400Wとなっている。当然、導入価格や運用コストはMI355Xの方が高い。

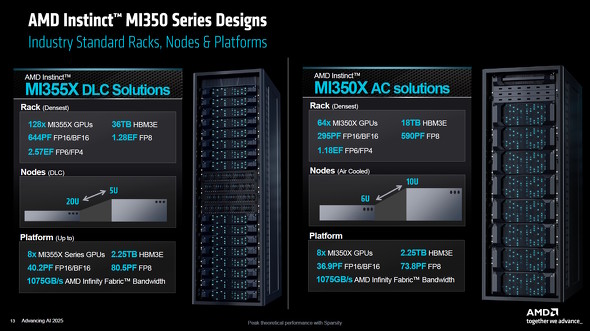

実際にラックマウントされた運用状態では以下のような見た目になる。

両モデル共に、1ノード当たり最大で8基の搭載に対応する。ラック数は「MI355X DLCソリューション」では最大16ノード、「MI350X ACソリューション」では最大8ノードとなるので、MI355X DLCソリューションでは最大128GPU構成(8基×16ノード)、MI350X ACソリューションでは最大64GPU構成(8基×8ノード)を構築/運用できる。

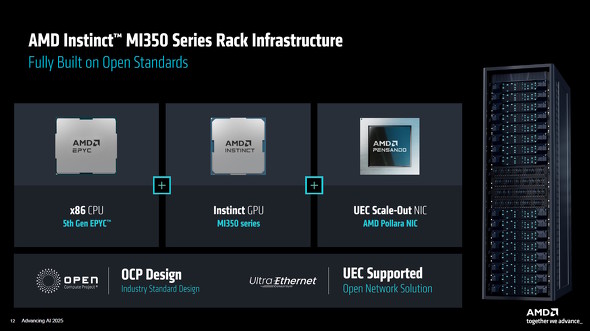

CPUはAMDの第5世代EPYCの「EPYC 9005シリーズ」を、ノード間通信にはAMDのUltra Ethernet規格準拠の高速ネットワークカード「Pollara」を組み合わせるのが標準構成だ。

Instinct MI350シリーズのパッケージング

ここからは、Instinct MI350シリーズを“シリコン”視点で深く解説したい。

まずは、パッケージ的な見どころをチェックしていこう。ここには民生向けGPUであるRadeon RXシリーズには見られないような、先進のチップレットアーキテクチャの適用と、高度なパッケージング技術が見て取れる。

Instinct MI350シリーズを構成する主要ダイ(チップ)は2つある。1つは、TSMCのプロセスノード「N3P」で製造される演算コアダイ「Accelerator Compex Die(XCD)」で、もう1つはTSMCのプロセスノード「N6」で製造された「I/O Base Die(IOD)」だ。IODは後述する計8基のHBM3Eメモリとの入出力インタフェースと、PCI Expressバスなどの各種バスインターフェースを内包した入出力プロセッサにあたる。

8基のXCDと2基のIODを合わせると、トランジスタ数は1850億個で、ちょうど「GeForce RTX 5090」の920億個の2倍となる(メモリ部のトランジスタ数はカウントしていない)。

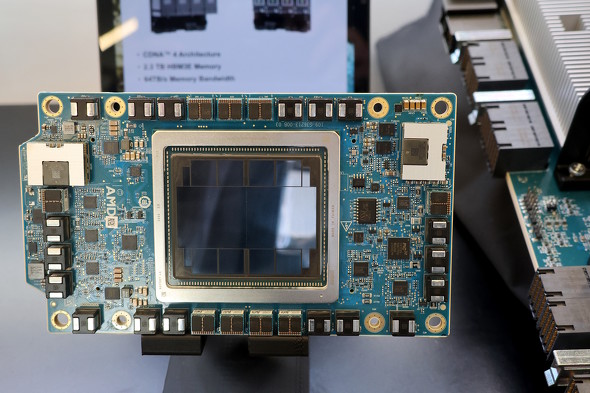

イベント会場で展示されていたInstinct MI350シリーズのカード(350Xか355Xかは不明)。巨大なチップにおいて上下に4基ずつあるのがHBM3Eメモリチップで、中央の巨大なダイがIODだ。写真ではよく見えないが「田の字」状にXCDが実装されており、中央にはIODの接続“跡”がある

イベント会場で展示されていたInstinct MI350シリーズのカード(350Xか355Xかは不明)。巨大なチップにおいて上下に4基ずつあるのがHBM3Eメモリチップで、中央の巨大なダイがIODだ。写真ではよく見えないが「田の字」状にXCDが実装されており、中央にはIODの接続“跡”があるXCDとIODとの接続とパッケージングには、TSMCの「CoWoS-S(Chip on Wafer on Substrate with Silicon interposer)」が用いられており、4つのXCDはIODの上に載せるような形で、TSV(Through-Silicon Via)による3D接続がなされている。

下のパッケージング図解では、このIODが2基描かれているのが見えると思う。事実、Instinct MI350シリーズではIODを隣接する辺で連結させている。接続方式は「2.5D式」「AMD Infinty Fabric Advanced Package」という説明があるのみで、具体的な方式に言及はないものの、CoWoS-Sが活用されている以上、「シリコンブリッジ」か「シリコンインターポーザー(TSV)」が用いられていると見られる。

後述するHBM3Eメモリも、同じ「2.5D式」を使って接続されている。

Instinct MI350シリーズが採用しているHBM3Eメモリは、1スタック(1カ所のフットプリント)当たり12層(12Hi)構成となっており、8GHz(8Gbps)で駆動する。量産されているHBM3Eチップは1枚当たり3GB(24Gbit)となっているので、12層重ねると1スタック当たり36GBとなる。

上の図解を見ても分かるように、MI350シリーズは左右4スタックずつ、計8スタックを備えるので「36GB×8スタック=288GB」の容量があることが分かる。

メモリ帯域についても計算してみよう。HBM3系のメモリは1024bitバスを備えるので、メモリ帯域は「1024bit×8Gbps×8スタック÷8bit=毎秒8TB」となる。ちなみにHBM系メモリでは積層数の大小でメモリバス幅に変化はない。そのため、メモリ帯域は積層(Hi)数と無関係である。

まとめると、Instinct MI350シリーズのスタイルは以下の通りとなる。

- IOD上には4基のXCDが3D実装され、IODは4基のHBM3Eと2.5D接続されている

- このセットを2つ、パッケージ基板上に実装した上で、2つのIODも2.5D接続している

最先端の3nm“級”プロセスノード採用に加え、高度な3D×2.5Dパッケージングまでも併用していることもあり、製造コストは相当に高いことが推察される。

将来のことは分からないが、直近でこの技術をコンシューマー向けのRadeon RXシリーズに採用するのは難しいだろう。

CDNA 4アーキテクチャの詳細な説明と、Instinct MI350シリーズのパフォーマンスに関する考察は別の記事に譲る。楽しみにしていてほしい。

関連記事

AMDが「Instinct MI350シリーズ」を2025年第3四半期に出荷開始 275台以上のラックシステムを2030年までに“1台”にまとめる計画も

AMDが「Instinct MI350シリーズ」を2025年第3四半期に出荷開始 275台以上のラックシステムを2030年までに“1台”にまとめる計画も

AMDが、新しいGPUアクセラレーター「Instinct MI350シリーズ」の出荷を2025年第3四半期に開始する。今後のGPUアクセラレーターに関するロードマップもチラ見せされた。 AMDのGPUアクセラレーター「Instinct」のロードマップを公表 「Insinct MI350X」は2025年内に登場

AMDのGPUアクセラレーター「Instinct」のロードマップを公表 「Insinct MI350X」は2025年内に登場

AMDが、AI処理やハイパフォーマンスコンピューティング向けに発売しているGPU「AMD Instinct」のロードマップを発表した。2024年後半には現行アーキテクチャにおける改良版をリリースし、2025年には新アーキテクチャ、2026年にはさらなる新アーキテクチャの製品を投入する予定だという。 AMDが新型GPUアクセラレータ「Instinct MI300シリーズ」の詳細を発表 「NVIDIA H100」よりも強い?

AMDが新型GPUアクセラレータ「Instinct MI300シリーズ」の詳細を発表 「NVIDIA H100」よりも強い?

AMDが、投入を予告していたGPUアクセラレータ「Instinct MI300シリーズ」の詳細情報を公表した。「NVIDIA H100」のSMX5ボード版と比べると、ほぼ同じか上回るパフォーマンスを発揮できるという。 AMD、HPC向けのGPUアクセラレーター「AMD Instinct MI200」シリーズを発表 業界初のマルチダイGPU構成を採用

AMD、HPC向けのGPUアクセラレーター「AMD Instinct MI200」シリーズを発表 業界初のマルチダイGPU構成を採用

米AMDは、このほど開催したオンラインイベント「AMD Accelerated Data Center Premiere」にて最新GPUアクセラレーターとなる「AMD Instinct MI200」シリーズの発表を行った。 AMDが次世代GPU「Radeon RX 5000」ファミリーを7月投入

AMDが次世代GPU「Radeon RX 5000」ファミリーを7月投入

AMDが、台湾国際会議中心で次世代GPUや第3世代Ryzenプロセッサなどの製品群を紹介した。ここでは「NAVI」の開発コード名で開発された次世代GPUについて見ていく。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- キーボード「FILCO」ブランドのダイヤテックが閉業 4月22日付で (2026年04月24日)

- 次期「DaVinci Resolve 21」で写真編集が可能に/Google Cloudが第8世代TPUを発表 (2026年04月26日)

- 大型連休前のアキバは新CPUラッシュ! AMD「Ryzen 9 9950X3D2」とIntel「Core Ultra 5 250K Plus/KF Plus」の気になる在庫状況 (2026年04月25日)

- 持ち運びを極めた超軽量キーボード「ロジクール KEYS TO GO 2」が17%オフの9980円に (2026年04月23日)

- ACアダプター不要の外付けHDD「Seagate One Touch Desktop External Hard Drive」を試す 超大容量で配線スッキリ (2026年04月24日)

- Windows 11の使い勝手はどう変わる? 「Copilot」名称外しやInsider Program再編に見るMicrosoftの本気度 (2026年04月24日)

- 「Apple AirPods 4」が20%オフの2万3798円に (2026年04月24日)

- 2026年版Surfaceはどうなる? 正面衝突を避けるMicrosoft、10万円切り「MacBook Neo」対抗への秘策はあるか (2026年04月21日)

- 部屋の雰囲気を一瞬で変えられる「SwitchBot RGBIC フロアライト」が15%オフの7633円に (2026年04月24日)

- Microsoftの新日本語IME「Copilot Keyboard」が正式版に “お前を消す方法”で有名なキャラ「カイル」も追加 (2026年04月23日)