AMDの「Instinct MI350シリーズ」は競合NVIDIAよりもワッパに優れるAIドリブンなGPU 今後の展開にも注目(2/4 ページ)

CDNA 4におけるComute Unitの改良ポイント

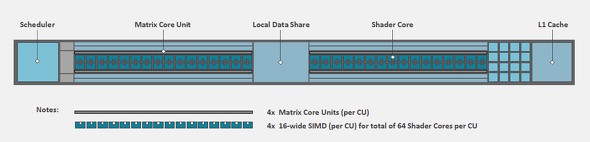

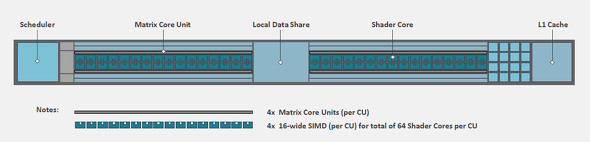

続いて、CDNA 4アーキテクチャにおけるCUの構成を見ていきたい。

実際のところ、大ざっぱな構成は「CDNA 2アーキテクチャ」(Instinct MI200シリーズ)以来変わっていない。内包される演算器たちの“ポテンシャル”を向上させる形でパワーアップを図っている。ということで、参考までにCDNA 2アーキテクチャにおけるCUのブロックダイアグラムを示す。

CDNA 2/3と同じく、CDNA 4でも1基のCUにはシェーダーコアを64基(SIMD16×4基)、マトリックスコアを4基搭載している。ブロックダイアグラムの見た目的には変わり映えがないものの、細部はいくつか改良されている。

改良点1:共有メモリ(LDS)の容量増加

改良点の1つが、CU間の共有メモリ「Loca Data Share(LDS)」だ。実態的にいうと、LDSはキャッシュメモリと同等の速度で動作する超高速なSRAMとなる。

CDNA 3アーキテクチャまでのLDSは1バンク当たり32bitを512エントリーという構成で、これを32バンク備えていた。そのため、総容量は「32bit×512エントリー×32バンク=64KB」となり、データへのアクセスは直接アドレスを指定して行う形態を取っていた。

それに対し、AMDによるとCDNA 4アーキテクチャのLDSは「160KBに増量された」のだという。詳細の説明がなかったが、従来の延長線上で考えると「160KB=32bit×640エントリー×64バンク」という感じの構成だと思われる。このLDS強化は昨今の人気のニューラルネットワークである「トランスフォーマーモデルへ対応するための最適化の一環だ」という。

改良点2:シェーダーコアにおけるL2キャッシュの仕様

シェーダーコアのベクトル演算器側にあるL1キャッシュは「総容量32KBの64ウェイアソシアティブ(キャッシュラインサイズは128バイト)」で、CDNA 3以前と同一仕様となっている。一方で、L2キャッシュには、2つほど興味深い“手入れ”がなされている

【非コヒーレントデータをL2キャッシュに置ける】

1つは、非コヒーレントデータをL2キャッシュへ置くことを“OK”とする制御を導入したことだ。この際は、「NC(非コヒーレント)フラグ」を立ててキャッシュするようになっている。

「なんでそんな制御をするのか?」という点だが、ストリーミングデータや入出力(I/O)バッファーといった「使い捨てが明確なデータ」、あるいは「処理が同一XCD内で収まることが自明なデータ」では、L2キャッシュにヒットさせても問題ないからだ。

このような制御をすることで、HBM3E(グラフィックスメモリ)や他のXCDにあるL2キャッシュとの同期取りを省略できるので、その分だけパフォーマンスの向上が期待できる。

【ダーティー状態のキャッシュラインの内容を存置できる】

2つ目は、いわゆる「ダーティ状態」のL2キャッシュラインの内容がグラフィックスメモリに書き出されたとしても、そのラインのエントリーを「クリーン」(同期済み)と見なしてL2キャッシュに残す制御の導入だ。ダーティー状態は、L2キャッシュ側がデータが新しい(グラフィックスメモリ側のデータが古い)状態を指す。

CDNA 3までのアーキテクチャでは、L2キャッシュにダーティ状態のキャッシュラインがある場合、その内容がグラフィックスメモリにライトバックされると、そのラインをクリア(消去)していた。この場合、このキャッシュラインに該当するアドレスを同一XCD内の別CUが参照しようとした場合、再度メモリにアクセスして読み出すことになる。「さっきまであったデータをもう一度取りに行く」という挙動は、シンプルにもったいない。

この新しい制御によって、複数のCUが隣接するアドレスを反復的に読み書きする場合に、L2キャッシュのヒット率が劇的に改善し、パフォーマンスが向上する。

ここまでの解説が難しかったという人は、「L2キャッシュにデータをなるべく長く安全に残しておけるようになり、データの再利用性を高められたので、無駄なメモリ帯域の消費を減らせた」と思ってもらえればよい。

マトリックスコアは「低精度演算」の高速化を重視

3Dグラフィックス処理に未対応なのに「シェーダーコア」と呼ぶのはどうなんだ、という違和感はさておいて、ここでいうシェーダーコアは「スカラ演算」と「ベクトル演算」を行う演算器ということになる。当然、ベクトル演算は1CU当たり4基ある「16要素SIMD演算器」で行う事になる。一方、スカラ演算は、1CU当たり1基備える「専用スカラ演算器」で行われる。

その名の通り、マトリックスコアは実態として「行列演算器」となる。RDNA系アーキテクチャでは「AIアクセラレーター」に相当するもので、昨今のNVIDIA製GPUなら「Tensorコア」に相当する。

ここで、Instinct MI350シリーズの理論性能を計算してみようと思う。

CDNA系のGPUアーキテクチャでは、CDNA2の時にSIMD演算器がFP64(64bit浮動小数点)演算にネイティブ対応する仕様に改められた。これにより、FP32(32bit浮動小数点)演算時のスループット(実効演算性能)が最大2倍となった。

このことを踏まえて、空冷タイプの「Instinct MI350X」(最大2.2GHz駆動)のFP32ベクトル演算時の理論性能値を求めると、以下の通りとなる。

32 CU×8 XCD×64 SIMD×2.2GHz×2倍スループット×2FLOPS(積和)≒144.2TFLOPS

同様に、水冷タイプのInstinct MI355X(2.4GHz)でも理論性能値を求めると、以下の通りとなる。

32 CU×8 XCD×64 SIMD×2.4GHz×2倍スループット×2FLOPS(積和)≒157.3TFLOPS

いずれも、AMDが公表している公式スペックと一致している。

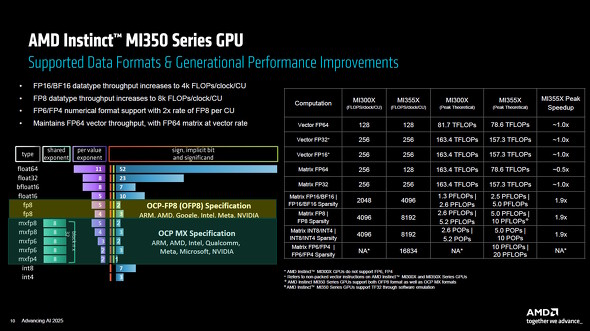

Instinct MI350シリーズが対応する演算フォーマットと、同シリーズにおける公称演算性能。FP32でベクトル演算を行った際の性能値は、本文で計算した結果とほぼ一致しており、CDNA 3世代の「Instinct MI300X」から着実にパフォーマンス向上していることが分かる

Instinct MI350シリーズが対応する演算フォーマットと、同シリーズにおける公称演算性能。FP32でベクトル演算を行った際の性能値は、本文で計算した結果とほぼ一致しており、CDNA 3世代の「Instinct MI300X」から着実にパフォーマンス向上していることが分かるマトリックスコアの演算パフォーマンスを深掘り

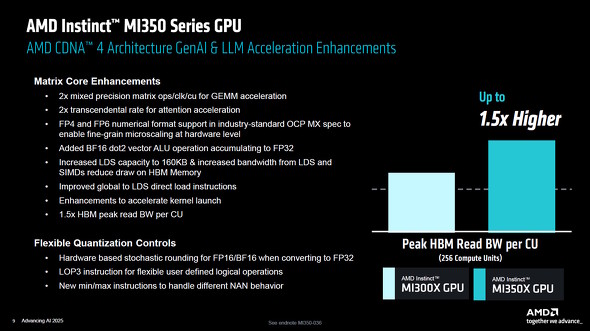

CDNA 4アーキテクチャにおけるマトリックスコアを見てみよう。

同アーキテクチャのマトリックスコアは、1要素当たりFP64に対応した「4×4×4サイズ」の行列演算を4クロックでこなせる。このことは、先の図にある「Matrix FP64」の1CU当たりの演算性能が1クロック/1CU当たり128FLOPSとなっていることからも分かる。

どういうことか、もう少し詳しくみていく。CU1基につきMatrix Coreは4基あるので、4×4×4サイズの行列の積和算(2FLOPS)を行う時の総演算量は以下の通りとなる。

4×4×4サイズの行列積和算(2FLOPS)×4基=512FLOPS

「あれ、演算性能が4倍になってるじゃん!」と思うかもしれないが、先ほどの図においてInstinct MI355Xの「Matrix FP64」のMI355Xの1クロック/1CU当たりの公称性能が128FLOPSとなっていることを鑑みると、512FLOPS分の計算に掛かるクロック数は「512FLOPS÷128FLOS=4クロック」となるため、これで正解となる。

上の図を再度見てもらうと分かるが、Instinct MI300Xでは、1クロック/1CU当たりの演算性能は256FLOPSなので、CDNA 4ではこの部分の性能が“半減”されてしまったことがわかる。

しかし逆に、CDNA 4ではFP16(16bit浮動小数点)以下の精度の演算性能が“2倍”に向上しているのも分かる(「MI355X Peak Speedup」に注目してほしい)。シェーダーコアにおけるベクトル演算性能は前世代を維持(同等)としているのに、ここは対照的である。

その理由を考察すると、CDNA 4では「行列演算はAI(人工知能)用途で利用頻度の高いFP16以下の低精度の高性能化にフォーカスした」といったところだろう。

以上を踏まえて、Instinct MI355XにおけるMatrix FP64の理論性能値を求めてみると、以下の通りとなる。

32 CU×8 XCD×(4×4×4行列)×2.4GHz×2FLOPS(積和)×4基÷4クロック≒78.6TFLOPS

FP16はパック化することで「16×16×16サイズ」で行列演算を行えるが、先の図を見る限りは8クロック掛けとなるようだ(Matrix FP16における1CUあたりの演算性能が1クロック/1CU当たり4096FLOPSとなっている点に注目)。

ということで、今度はマトリックスコアの理論性能値を、FP16で求めてみよう。

32 CU×8XCD×(16x16x16行列)×2.4GHz×2倍スループット×2FLOPS(積和)×4基÷8クロック≒2.5PFLOPS

先の図にある公式スペックと一致した。

OCPの最新フォーマットに対応

先ほどの図の左側を再度見てほしい。AMDは、CDNA 4アーキテクチャにおいて「OCP(Open Compute Project)」が規定する最新数値フォーマットに一通り対応していることをアピールしている。

先代のCDNA 3アーキテクチャでは、既に「E5M2」「E4M3」の2タイプのFP8(8bit浮動小数点)に対応済みだが、CDNA 4アーキテクチャでは新たにOCPが規定した、比較的新しいMicroscaling Formats(MX)形式「Block n×32」にも対応した。

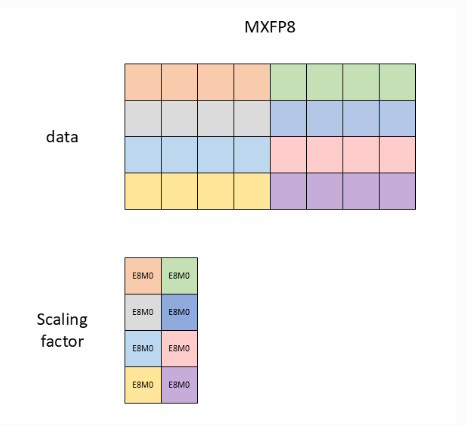

この形式の意味だが、MXFP8の「Block 4×32」の場合で考えると、以下のような感じになる。

まず、1ブロックは「FP8を4個」と定義され(E5M2でもE4M3でもOK)、共通指数項は1ブロック当たり1個を与える(つまり4個のFP8で共用)。共通指数項は8bitとなるので、この例では1ブロックのサイズは5バイトとなる。

このブロックが行列などのイメージで32セット並ぶ――これがMXFP8の「Block 4×32」だ。CDNA 4では、このデータを読み出すと自動的にハードウェアデコードして、レジスタに代入するようになっている。CDNA 4ではMXF8Pの他に「MXFP6」「MXFP4」もサポートしている。

読者の中には気付いた方もいるかもしれないが、このマイクロスケール形式はブロック要素数が少ないと、データの圧縮効果はそれほど高くない。それでもあえてマイクロスケール形式を規定したのは、何よりも「ダイナミックレンジの維持」目的の方が強いのだ。

関連記事

AMDのデータセンター向けGPU「Instinct MI350シリーズ」って? 歴史と構造、シリコンなどをチェック!

AMDのデータセンター向けGPU「Instinct MI350シリーズ」って? 歴史と構造、シリコンなどをチェック!

AMDが新型のデータセンター向けGPU「Instinct MI350シリーズ」を発表した。どのようなGPUなのか、そのあらましを見てみよう。【訂正】 AMDが「Instinct MI350シリーズ」を2025年第3四半期に出荷開始 275台以上のラックシステムを2030年までに“1台”にまとめる計画も

AMDが「Instinct MI350シリーズ」を2025年第3四半期に出荷開始 275台以上のラックシステムを2030年までに“1台”にまとめる計画も

AMDが、新しいGPUアクセラレーター「Instinct MI350シリーズ」の出荷を2025年第3四半期に開始する。今後のGPUアクセラレーターに関するロードマップもチラ見せされた。 AMDのGPUアクセラレーター「Instinct」のロードマップを公表 「Insinct MI350X」は2025年内に登場

AMDのGPUアクセラレーター「Instinct」のロードマップを公表 「Insinct MI350X」は2025年内に登場

AMDが、AI処理やハイパフォーマンスコンピューティング向けに発売しているGPU「AMD Instinct」のロードマップを発表した。2024年後半には現行アーキテクチャにおける改良版をリリースし、2025年には新アーキテクチャ、2026年にはさらなる新アーキテクチャの製品を投入する予定だという。 AMDが新型GPUアクセラレータ「Instinct MI300シリーズ」の詳細を発表 「NVIDIA H100」よりも強い?

AMDが新型GPUアクセラレータ「Instinct MI300シリーズ」の詳細を発表 「NVIDIA H100」よりも強い?

AMDが、投入を予告していたGPUアクセラレータ「Instinct MI300シリーズ」の詳細情報を公表した。「NVIDIA H100」のSMX5ボード版と比べると、ほぼ同じか上回るパフォーマンスを発揮できるという。 AMD、HPC向けのGPUアクセラレーター「AMD Instinct MI200」シリーズを発表 業界初のマルチダイGPU構成を採用

AMD、HPC向けのGPUアクセラレーター「AMD Instinct MI200」シリーズを発表 業界初のマルチダイGPU構成を採用

米AMDは、このほど開催したオンラインイベント「AMD Accelerated Data Center Premiere」にて最新GPUアクセラレーターとなる「AMD Instinct MI200」シリーズの発表を行った。

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- 迷走の5年間を経て――MicrosoftがWindows 11の“不都合な真実”を認め、改善を宣言した背景 (2026年04月01日)

- 安いMacは「使えない」? MacBook Neo 8GBモデルで試す、後悔しないための活用術と注意点 (2026年04月02日)

- Windows 11(24H2/25H2)の3月オプション更新でインストールできないトラブル 「帯域外更新」で対処 (2026年04月02日)

- “録画文化”は死ぬのか? 物理メディアの終わりが見えてきた今、TV番組保存の現実的な代替案を考える (2026年04月01日)

- 3COINSで1430円の「PCケース:13.3インチ」を試す 収納ポケット充実、フリーアドレスのオフィス移動に便利 (2026年04月02日)

- 視野2.4倍に拡大したオートフォーカスアイウェア「ViXion2」を試す 近視と老眼の悩みを一気に解消、11万円の価値はあるか? (2026年04月03日)

- 3COINSで880円の「3D構造マウスクッション」を試す 通気性抜群、これはトラックボールや分割キーボードに適したリストレストかも (2026年04月03日)

- ケンジントンの「SlimBlade Pro トラックボール」がセールで約1万円に (2026年03月31日)

- 液晶なのにE Ink風? 約10万円の価値はある? TCLの異色電子ノート「Note A1 NXTPAPER」徹底レビュー (2026年04月03日)

- 200Hzの高速駆動、Mini LED搭載の「IODATA ゲーミングディスプレイ GigaCrysta EX-GDQ271JLAQ」がセールで22%オフの4万6580円に (2026年04月01日)