AMDの「Instinct MI350シリーズ」は競合NVIDIAよりもワッパに優れるAIドリブンなGPU 今後の展開にも注目(3/4 ページ)

NVIDIAの「Blackwell」と比べて性能はどうなのか?

ここまで来て、中には「ご託はいいから性能はどうなんだ?」と思っている人もいるだろう。それを意識してか、AMDもその辺のアピールを忘れていない。

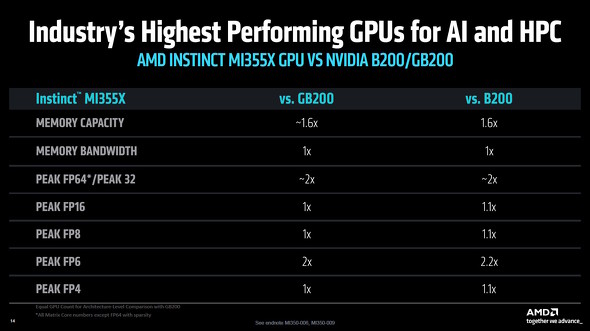

下の図は、Instinct MI355Xと競合製品である「NVIDIA GB200」「NVIDIA B200」の理論性能値を比べたものだが、GPU単体ではほぼ同等の性能を発揮できていることが分かる。

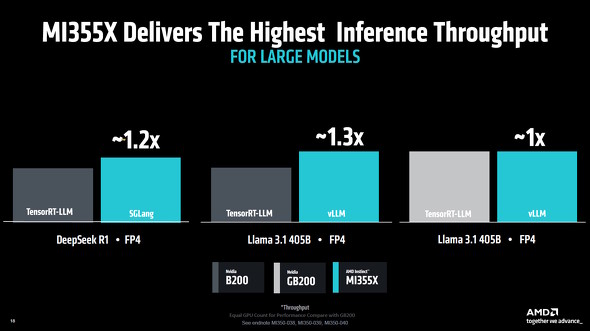

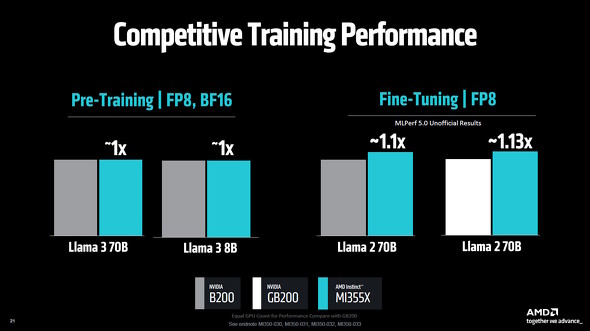

実際の大規模言語モデル(LLM)でパフォーマンスを比較した場合でも、FP4/FP8/BF16演算を用いる場合は同等かそれ以上の結果を出せているという。

AMDとしては「絶対性能において、NVIDIAのBlackwellには引けを取らない」ということをアピールしたいのだろう。

「Infinty Fabric」と「Infinity Cache」の様子

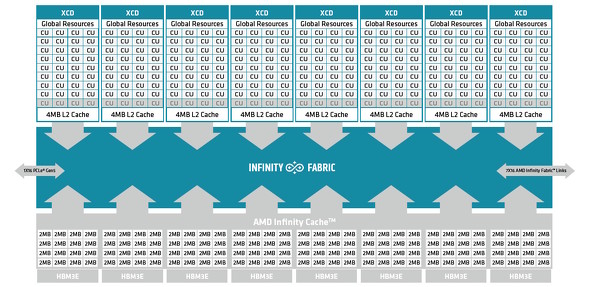

AMDでは、半導体のインターコネクト(内部接続)に「Infinity Fabric」を利用している。

先代のCDNA 3アーキテクチャ世代のInfinity Fabricは、4基の小さな「I/O Base Die(IOD)」を互いに全て接続する「フルメッシュ接続」状態だった。それに対してCDNA 4アーキテクチャのInfinity Fabricは、2基のIODが“一辺で”2.5D的に接合されている。ネットワーク網としては、随分と簡略化されている。

ただし、AMDによるとIOD間のデータ伝送帯域は毎秒5.5TBで、「Accelerator Compex Die(XCD)」の伝送速度も最大14%高速化されたという。

IODの構成自体は大きく変わった一方で、CDNA 4のメモリ階層を支える「Infinity Cache」システムは、CDNA 3から大きく変わっていない。

HBM3Eの各メモリスタックには、2MB単位のバンク型アレイが16基ある構成となっている。このスタックは全部で8個あるので、Infinity Cacheの総容量は「2MB×16バンク×8スタック=256MB」となる。

Infinity Cacheは、事実上のL3キャッシュだ。「なぜ2MB単位でバンク管理がなされているの?」という点だが、これは256MBの単一キャッシュ構成にすると、キャッシュの当落判定時間が増大する上に、アクセスの並列性も悪化するからだ。

今回のInstinct MI350シリーズでは、2MBバンクが全体で128個(16バンク×8スタック)あるため、HBM3Eメモリ全体がカバーするアドレスの全域を128分割したイメージで均等にカバー可能だ。さらに、128バンク分の並列アクセスも実現できる。

なお、AMDによれば、Infinity Cacheのキャッシュ構成は「16ウェイのセットアソシエイティブ」だという。実際の運用においては、恐らくアドレスの一部ビットに基づいて、自動的に特定の2MBバンクが決定される方式となっていると思われる。

CDNA 4における演算とメモリのパーティショニングを深掘り

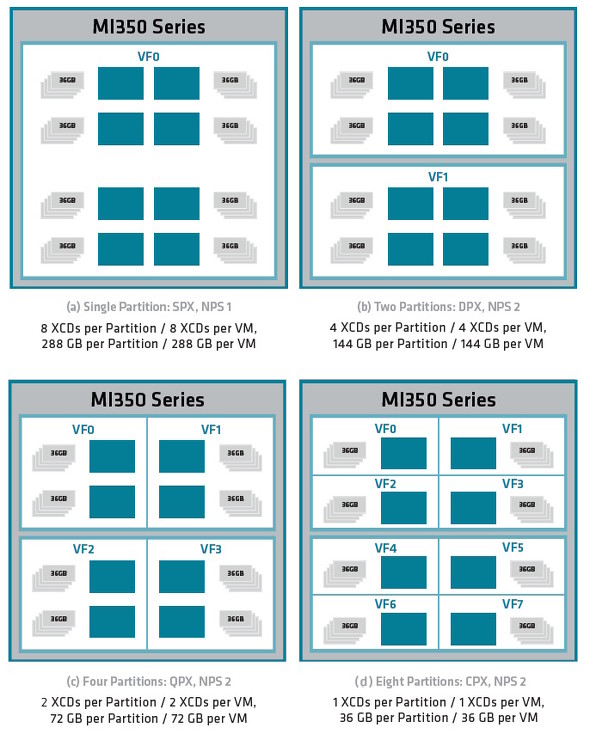

CDNA4アーキテクチャは、1万6384基ものシェーダーコアがもたらす強大な演算パワーと、毎秒8TBの超高速なアクセスが可能な288GBのHBM3Eメモリを、用途に応じて内部構造(リソース配分)を仮想的に変えつつ利用可能だ。

まず演算能力については、8基のXCDを「1基」「2基」「4基」「8基」の4形態に設定することが可能だ。

8基のXCDを全て活用する「SPX(Single Processor Expansion)モード」は、大規模なデータに対して“全力で”演算に取りかかる必要のあるAI開発におけるトレーニングフェーズに向いている。逆に、小規模な推論モデルを動作させるフェーズでは、8基のXCDを個別に使う「CPX(Coherent Processor Expansion)」が適している。

グラフィックスメモリに関しては、「2基のIODを1つに連結して統合した」という物理構造に起因したパーティショニングモードが2種類用意される。

1つ目の「NPS1モード」は、1ソケットを1NUMAノードとして取り扱う。全てのXCDが8基のHBM3Eメモリの全体に渡ってインターリーブアクセスを行えるため、大規模AI開発における学習フェーズにおいて有効だ。

2つ目の「NPS2モードは、2ソケットを1NUMAノードとして取り扱う。物理IODごとにメモリパーティションを区切る形で、具体的には1基のIOD当たり4つのHBM3Eスタックを割り当てて、2つのメモリーパーティションとして管理する。

どちらのモードにしても、反対側のIODに実装されているHBM3Eメモリへのアクセスは遅延が大きくなることに変わりない。しかし、NPS2モードでは各XCDに割り当てられるメモリ空間が、優先的に同じIOD側にあるHBM3Eメモリで確保されるようになる。

この特性を理解していれば、CDNA 4アーキテクチャでボトルネックとなりうるIOD間通信を抑止しつつ、システムを運用可能だ。ただし、演算パーティションとメモリーパーティションの切り替えは、GPUシステムの再起動が必要となる。

関連記事

AMDのデータセンター向けGPU「Instinct MI350シリーズ」って? 歴史と構造、シリコンなどをチェック!

AMDのデータセンター向けGPU「Instinct MI350シリーズ」って? 歴史と構造、シリコンなどをチェック!

AMDが新型のデータセンター向けGPU「Instinct MI350シリーズ」を発表した。どのようなGPUなのか、そのあらましを見てみよう。【訂正】 AMDが「Instinct MI350シリーズ」を2025年第3四半期に出荷開始 275台以上のラックシステムを2030年までに“1台”にまとめる計画も

AMDが「Instinct MI350シリーズ」を2025年第3四半期に出荷開始 275台以上のラックシステムを2030年までに“1台”にまとめる計画も

AMDが、新しいGPUアクセラレーター「Instinct MI350シリーズ」の出荷を2025年第3四半期に開始する。今後のGPUアクセラレーターに関するロードマップもチラ見せされた。 AMDのGPUアクセラレーター「Instinct」のロードマップを公表 「Insinct MI350X」は2025年内に登場

AMDのGPUアクセラレーター「Instinct」のロードマップを公表 「Insinct MI350X」は2025年内に登場

AMDが、AI処理やハイパフォーマンスコンピューティング向けに発売しているGPU「AMD Instinct」のロードマップを発表した。2024年後半には現行アーキテクチャにおける改良版をリリースし、2025年には新アーキテクチャ、2026年にはさらなる新アーキテクチャの製品を投入する予定だという。 AMDが新型GPUアクセラレータ「Instinct MI300シリーズ」の詳細を発表 「NVIDIA H100」よりも強い?

AMDが新型GPUアクセラレータ「Instinct MI300シリーズ」の詳細を発表 「NVIDIA H100」よりも強い?

AMDが、投入を予告していたGPUアクセラレータ「Instinct MI300シリーズ」の詳細情報を公表した。「NVIDIA H100」のSMX5ボード版と比べると、ほぼ同じか上回るパフォーマンスを発揮できるという。 AMD、HPC向けのGPUアクセラレーター「AMD Instinct MI200」シリーズを発表 業界初のマルチダイGPU構成を採用

AMD、HPC向けのGPUアクセラレーター「AMD Instinct MI200」シリーズを発表 業界初のマルチダイGPU構成を採用

米AMDは、このほど開催したオンラインイベント「AMD Accelerated Data Center Premiere」にて最新GPUアクセラレーターとなる「AMD Instinct MI200」シリーズの発表を行った。

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- 迷走の5年間を経て――MicrosoftがWindows 11の“不都合な真実”を認め、改善を宣言した背景 (2026年04月01日)

- 安いMacは「使えない」? MacBook Neo 8GBモデルで試す、後悔しないための活用術と注意点 (2026年04月02日)

- Windows 11(24H2/25H2)の3月オプション更新でインストールできないトラブル 「帯域外更新」で対処 (2026年04月02日)

- “録画文化”は死ぬのか? 物理メディアの終わりが見えてきた今、TV番組保存の現実的な代替案を考える (2026年04月01日)

- 3COINSで1430円の「PCケース:13.3インチ」を試す 収納ポケット充実、フリーアドレスのオフィス移動に便利 (2026年04月02日)

- 視野2.4倍に拡大したオートフォーカスアイウェア「ViXion2」を試す 近視と老眼の悩みを一気に解消、11万円の価値はあるか? (2026年04月03日)

- 3COINSで880円の「3D構造マウスクッション」を試す 通気性抜群、これはトラックボールや分割キーボードに適したリストレストかも (2026年04月03日)

- ケンジントンの「SlimBlade Pro トラックボール」がセールで約1万円に (2026年03月31日)

- 液晶なのにE Ink風? 約10万円の価値はある? TCLの異色電子ノート「Note A1 NXTPAPER」徹底レビュー (2026年04月03日)

- 200Hzの高速駆動、Mini LED搭載の「IODATA ゲーミングディスプレイ GigaCrysta EX-GDQ271JLAQ」がセールで22%オフの4万6580円に (2026年04月01日)