Qualcommの新SoC「Snapdragon X2 Elite」に見るPCのトレンド:Snapdragon Summit 2025(3/4 ページ)

パフォーマンスと省電力のバランスをいかに採るか

一般にプロセッサのパフォーマンスを向上させようとすると、(トランジスタ数が増加するため)半導体の“ダイ”サイズが大きくなり、それに伴って消費電力も上昇する。コスト上昇や発熱の原因となるが、これを抑えつつ性能向上を実現するのが製造プロセスの微細化と改良であり、その進化サイクルは「ムーアの法則」などと呼ばれたりする。

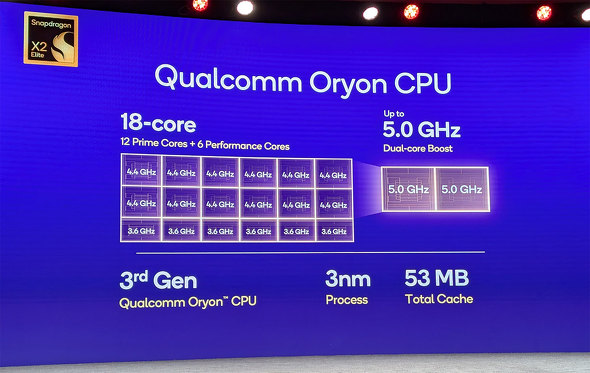

Snapdragon X Eliteも前世代ではTSMCの4nm製造プロセスを用いていたが、今回のSnapdragon X2 Eliteでは同じくTSMCのN3Pのプロセスを用いており、特に重要な部分のみN3Xを用いることで微細化の世代が3nmまで上昇している。

結果として、CPUコアでは50%の速度向上が実現し、GPUでは最大2.3倍、NPU性能でも8割近く上昇して80TOPSを実現している。前述のデシュパンデ氏によれば、製造プロセスの変更ももちろん大きいが、ハードウェアからソフトウェアまで、アーキテクチャ全般にわたるチューンアップで効率化を実現できたのが大きいという。

ただ、ダイサイズはコストに直結するため、これら全体の性能向上を図った場合、どの機能にどれだけチップ上の面積を与えるかが大きな鍵となり、このバランスが重要となる。

加えて、Qualcommの講演やインタビューでは毎回のように「省電力」が最重要ポイントとしてキーワードとして頻出しており、これがいかに設計に影響を与えたのかが分かる。

例えば興味深いのが、今回のAdreno GPUで採用されたHPM(High Performance Memory)という仕組みだ。GPUコアが内蔵する18MBのSRAMキャッシュだが、これはもともとSnapdragonが持っていたGPUキャッシュの仕組みを外部からAPIなどを通して利用できるようになったもので、高速メモリアクセスを実現する。

米Qualcomm TechnologiesバイスプレジデントでAI/生成AI担当製品マネジメントのヴィネッシュ・スクマール(Vinesh Sukumar)氏によれば、「歴史的にみて、消費電力の40%はメモリと計算モジュールの間のデータ転送にかかっており、SRAMユニットを計算ブロックの近くに配置することで速度向上と省電力化を実現している」(同氏)という。

つまり、データ転送のオーバーヘッドを軽減させるだけで速度向上と省電力が両立できるという考えだ。

この消費電力の話題はAI処理にもからむ。例えばSnapdragon X2 EliteではNPUの推論処理にFP8をサポートした。浮動小数点演算の型だが、一般的なAIアプリケーションの推論処理ではそれほど演算精度を求められないため、浮動小数点でもFP16(単精度)やFP32(倍精度)より軽量動作が可能なFP8のような型が好まれる。

これにより、データの転送量やメモリ占有量が半分または4分の1程度まで減少するので、いわゆる“エッジAI”のようなローカルデバイスでのAI動作における恩恵が大きい。

一方で、同じデータ転送量やメモリ占有量となるINT8のような整数型をAIの推論処理に用いた場合、消費電力はFP8よりも大幅に削減できる。理由は小数点演算よりも整数演算の方が負荷が軽いからだ。

動作させるLLM(大規模言語モデル)の種類にもよるが、学習データを工夫することでエッジデバイスでのAI動作が消費電力の面で大幅に軽くなることを意味しており、開発者らは演算精度と消費電力のバランスをみてどちらを選択するのかを選ぶことになる。

関連記事

生成AIが笑ってしまうほど高速に――Qualcommが450TOPSの“外付け”NPUを開発 Dell Technologiesのx86ノートPCに搭載

生成AIが笑ってしまうほど高速に――Qualcommが450TOPSの“外付け”NPUを開発 Dell Technologiesのx86ノートPCに搭載

Qualcommは自社のSnapdragon Xシリーズを搭載するPCを強く訴求している。しかし、COMPUTEX TAIPEI 2025に合わせて設置したプライベート展示場に足を向けると、なぜかx86 PCが主体となって展示されているコーナーがあった。どうやら、Qualcommの“新製品”が展示されているそうだ。 Epic GamesのアンチチートツールがArm版Windowsに対応完了 “スナドラ”搭載PCで遊べるフォートナイトも近日リリース

Epic GamesのアンチチートツールがArm版Windowsに対応完了 “スナドラ”搭載PCで遊べるフォートナイトも近日リリース

3月に対応を予告していた「Easy Anti-Cheat」のArm対応が完了した。 レノボの小型PC「ThinkCentre neo 50q Tiny Snapdragon」を試す ArmアーキテクチャのデスクトップPCはアリ?

レノボの小型PC「ThinkCentre neo 50q Tiny Snapdragon」を試す ArmアーキテクチャのデスクトップPCはアリ?

レノボ・ジャパンが、Snapdragon X搭載の小型PC「ThinkCentre neo 50q Tiny Snapdragon」を発売した。今までノートPCばかりだったArmアーキテクチャのWindows PCだが、ようやくデスクトップの選択肢も出てきた格好だ。実際に試してみよう。 約10万円で買えるWindows on ARMの検証機として「Lenovo IdeaPad Slim 5x Gen 9」はちょうど良い

約10万円で買えるWindows on ARMの検証機として「Lenovo IdeaPad Slim 5x Gen 9」はちょうど良い

「検証機の調達コストをある程度抑える方法はないのだろうか」と考えていたところちょうどいいデバイスを見つけたので紹介したい。 ARグラスで仕事はできるか? スマホサイズの「XREAL BEAM Pro 5G」と老眼にやさしい「XREAL One」で試す

ARグラスで仕事はできるか? スマホサイズの「XREAL BEAM Pro 5G」と老眼にやさしい「XREAL One」で試す

ガッツリではないものの、出先でちょこっと仕事をこなしたいという場合の装備は軽い方が良い。狭いテーブルのスペースを占有しないよう、デバイスは小さい方が良い。それができるのが「XREAL BEAM Pro 5G」と「XREAL One」だ。

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- 「MacBook Neo」は「イラスト制作」に使えるか? Appleが仕掛ける“価格の暴力”を考える (2026年05月12日)

- 高騰続くパーツ市場、値札に衝撃を受ける人からDDR4使い回しでしのぐ自作erまで――連休中のアキバ動向 (2026年05月11日)

- NVIDIA“一強”を突き崩すか AMDのAIソフトウェア「ROCm」と次世代GPU「Instinct MI400」がもたらす新たな選択肢 (2026年05月12日)

- 画面を持たない約12gの超軽量ウェルネストラッカー「Google Fitbit Air」 1万6800円で5月26日に発売 (2026年05月07日)

- オンプレミスAIを高速化する「AMD Instinct MI350P PCIe GPU」登場 グラボ形態で既存システムに容易に組み込める (2026年05月11日)

- ノートPCを4画面に拡張できる“変態”モバイルディスプレイ「ROADOM 14型 モバイルマルチディスプレイ X90M」が6万1560円に (2026年05月12日)

- USB Type-Cの映像出力をワイヤレスでHDMI入力できる「エレコム ワイヤレス HDMI 送受信機セット DH-CW4K110EBK」がセールで1万2580円に (2026年05月08日)

- 過去最高の受注急増と苦渋の全モデル受注停止――マウスコンピューター 軣社長が挑む“脱・メーカーのエゴ”と激動の2026年 (2026年05月11日)

- サンワ、サイドホイールを備えた多機能ワイヤレスマウス (2026年05月11日)

- ノートPCとスマホを同時急速充電できる「Anker Charger (140W, 4 Ports)」がタイムセールで8990円に (2026年05月12日)