Intelの新型CPU「Core Ultraプロセッサ(シリーズ3)」を支える「Intel 18A」と「PowerVia技術」を見てきた(2/3 ページ)

Intel肝いりの技術「RibbonFET」は何が優れている?

CPUやGPUを始めとして、PCやゲーム機に搭載される各種プロセッサは、無数の微細なトランジスターを“相互接続”して構築した論理回路を組み合わせることで成立している。

例えば、近年の高性能GPUは1チップ内に地球人口(約82億人)の10倍以上の数のトランジスターが実装されている。NVIDIAの「GeForce RTX 5090」の総トランジスター数は920億個だ。750mm2のダイに、地球人口の約11.2倍のトランジスターが“住んでいる”。

このように、高性能かつ高機能なプロセッサを作るには、単位面積当たりにより多くのトランジスターを実装しなければならない。なので、半導体業界はトランジスターをより小さく実現するための技術に磨きをかけているのだ。

このトランジスターの実装密度の目安が,この記事でもたびたび使っている「プロセスノード」というキーワードだ。以前はナノメートル(nm)単位で表記してきたが、今後は先述の通りオングストローム(A)で表記されるようになっていく流れがある。

プロセスノードが22nmくらいまでは、トランジスターの「ゲート長≒ノード値」となることが多かった(90nmくらいから、ズレは出ていたが)。最近では、ゲート長はほとんどそのままで、トランジスターを立体集積させることで集積度を上げる手法が使われるようになったため、プロセスノードは「ゲート長換算で何nm相当」という意味合いで表されるようになっている。

FinFETに限界が見えてきた

さて今回、Intelが実用化した新プロセスノード「Intel 18A」を実現するために開発された新構造のトランジスターについて解説を始めよう。

そもそも「トランジスター」とは、「ゲート」と呼ばれる部位に対する電力制御を行うための素子で、「ソース」部と「ドレイン」部の間(≒チャネル)の通電を制御する。

22nmプロセス以降で活用された「FinFET(Fin Field-Effect Transistor)」と呼ばれるトランジスターのおかげで、半導体のプロセスノードは一桁台まで順調に微細化が進んだ。しかし、2nmのあたりから、ソース部とドレイン部からの電界の回り込み(ノイズ)の影響が強くなり、結果的にゲートの静電制御が効きにくくなるようになってしまった。

ゲートを短くし過ぎたことで、ソース側/ドレイン側の電界の影響を受けて、ゲートが言うことを聞かなくなってしまう――この現象は「短チャネル効果(SCE:Short-Channel Effect)」と呼ばれるものだ。トランジスターの話をするときにはゲートを「水門」、チャネルを水流(水路)で例えることが多いが、2nmプロセスあたりから水路を短くしすぎた結果、水の流れがむしろ悪くなってしまったと考えると理解しやすい。

そこで登場したのが「RibbonFET」

この問題を解決すべく登場したのが、Intel 18Aプロセスで実用化された新構造のトランジスター「RibbonFET(Ribbon Fin Effect Transistor)」だ。これはIntel独自の呼称で、一般的には「GAAFET(Gate All Around Fin Effect Transistor)」と呼ばれる。

GAAFETを世界で初めて実用化したのはサムスン電子で、2022年に3nm相当プロセスで採用している。TSMCも、Intelとほぼ同じタイミングで「N2」という2nm相当プロセスで実用化した。

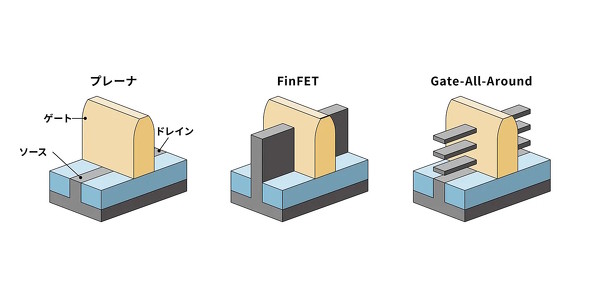

下の図は最もベーシックな「PlanarFET」、FinFET、そしてGAAFET(RibbonFET)の構造を簡単に図示したものだ。

3種類のFET(Fin Effect Transistor)を図示したもの。FinFETの“ひれ”、GAAFETの“ひげ”のようなものは、ゲートに接触しているものの貫通はしていない。実際のソース/ドレイン端子は垂直方向に別途引き出した端子となるが、図示する際は描かれない(省かれる)ことが多い

3種類のFET(Fin Effect Transistor)を図示したもの。FinFETの“ひれ”、GAAFETの“ひげ”のようなものは、ゲートに接触しているものの貫通はしていない。実際のソース/ドレイン端子は垂直方向に別途引き出した端子となるが、図示する際は描かれない(省かれる)ことが多い図を見比べると、RibbonFETではソース部からドレイン部に流れるヒゲのようなものが複数あることに気が付く。この構造によって、トランジスターのチャネル量が事実上増えたことになるため、ノイズの影響が小さくなり、短チャネル効果も解消され、ゲート制御がよりうまく働くようになるのだ。

おまけに、チャネル量が事実上増えたことで水(=チャネル)の流れが良くなる効果も付いてくる。

「PowerVia」の採用でプロセッサの作り方も変わる

従来のプロセッサ製造法では、微細なトランジスター群がつながりあって形成される微細な信号線と、電源を供給する配線が隣接/混在する構造となっていた。

超高速な信号のやりとりを行うトランジスターと、その入出力信号用の配線にとって、強い電気が流れる電力供給配線はノイズ源となりやすい。このことは、プロセッサのパフォーマンス向上の妨げともなりうる。

この問題を解決するために、Intelが業界一番乗りで実用化した新技術が「PowerVia」だ。端的にいうと、PowerViaは「トランジスター層」「給電回路」「信号回路」をほぼ完全に分離した構造のプロセッサを製造できる工法だ。

ノイズ源とトランジスター群と信号配線層を完全に分離できることから、動作クロックを引き上げやすく、太い給電回路と細い信号回路を分離できることから、信号配線(回路)の最適化、ひいてはトランジスターの増量にも貢献する。

ただし、イメージの通りPowerViaは高コストなチップ製造法だ。それだけに、今回のCore Ultraプロセッサ(シリーズ3)がそうであるように、プロセッサ全体に適用するのではなく、高機能/高性能が必要なチップ(タイル)の製造に活用するという。

PowerViaを採用して形成したプロセッサの断面図。茶色配線は給電回路を、そして黄色配線はトランジスターや信号回路を表している。中央がトランジスター層で、先に紹介したRibbonFETがここに並ぶことになる

PowerViaを採用して形成したプロセッサの断面図。茶色配線は給電回路を、そして黄色配線はトランジスターや信号回路を表している。中央がトランジスター層で、先に紹介したRibbonFETがここに並ぶことになるところで、PowerViaを用いた半導体の製造工程は、従来の工法とは手順が異なる。下図はその製造手順だ(流れとしては、左から右に工程が進む)。

PowerVia工法では、最初に「トランジスター層」と「信号配線層」だけをウエハー上に積層し、そこでいったん作業を終了する(上図の左から1番目と2番目)。その後、ウエハー自体を“ひっくり返して”、今度は先ほどとは反対方向に「電源配線」を積層していく(上図の左から3番目)。このウエハーの反転工程は「ウエハ−フリップ」と呼ばれる。その後、今度は反転させたウエハーに対し「電源供給配線」を積層して形成していく。

こうして、電源配線と信号配線が極力分離された構造が成立し、プロセッサがより高クロックで動作ができるようになるわけである。配線の最適化によって、電気抵抗も抑えられるので、省電力効果も期待できるとされる。

なお、チップからの出力信号線は信号配線層(Frontside)から取り出して「再配線層(RDL)」や貫通ビアなどで裏面側に引き出してパッケージに接続する。この工程は「フリップチップ」と呼ばれる(先述のウエハーフリップとは全く異なる工程)。

関連記事

Intelの新型CPU「Core Ultraプロセッサ(シリーズ3)」は何が変わった? Lunar Lakeからの進化をチェック!

Intelの新型CPU「Core Ultraプロセッサ(シリーズ3)」は何が変わった? Lunar Lakeからの進化をチェック!

Intelが2025年末に出荷を開始する予定のPanther Lakeこと「Core Ultraプロセッサ(シリーズ3)」。その技術的特徴を数回に分けて解説する。今回は、全体的な概要を紹介する。 2030年までに“世界第2位”を目指す! Intelが半導体の「受託生産」に乗り出す理由【前編】

2030年までに“世界第2位”を目指す! Intelが半導体の「受託生産」に乗り出す理由【前編】

Intelの半導体受託生産事業「Intel Foundry」が本格的に始動した。研究/開発から生産まで一貫して行う垂直統合体制だった同社が、ここに来て受託生産(ファウンドリー)事業に注力し始めたのはなぜなのだろうか。この記事では、その動機(モチベーション)について考察していきたい。 IntelがAI時代を見据えた半導体の「受託生産」ロードマップを発表 2030年までに世界第2位を目指す

IntelがAI時代を見据えた半導体の「受託生産」ロードマップを発表 2030年までに世界第2位を目指す

Intelが、半導体の受託生産(ファウンドリー)サービスに関するイベントを開催した。その中で、 2024年に「ムーアの法則」が再び走り出す? Intelが「PowerVia」の近況を報告 Meteor Lake(仮)のEコアをベースに実証実験

2024年に「ムーアの法則」が再び走り出す? Intelが「PowerVia」の近況を報告 Meteor Lake(仮)のEコアをベースに実証実験

Intelが「Intel 20A」プロセスから採用する予定の裏面電源供給技術「PowerVia」の近況を報告した。Meteor Lake(仮)のEコアをベースに本技術を適用したCPUの稼働について実験に成功したといい、6月中旬に京都市で開催されるイベントで論文が公開される。 Intelが新プロセス「Intel 3」の詳細を発表 消費電力当たりの性能を最大18%向上

Intelが新プロセス「Intel 3」の詳細を発表 消費電力当たりの性能を最大18%向上

Intelが、VLSIシンポジウム2024に合わせて「Intel 3」の詳細を発表した。「Intel 4」の細かい部分を改良したプロセスだが、それが最大18%のパフォーマンス改善につながっているという。

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- 画面を持たない約12gの超軽量ウェルネストラッカー「Google Fitbit Air」 1万6800円で5月26日に発売 (2026年05月07日)

- USB Type-Cの映像出力をワイヤレスでHDMI入力できる「エレコム ワイヤレス HDMI 送受信機セット DH-CW4K110EBK」がセールで1万2580円に (2026年05月08日)

- NAS向け低容量HDD枯渇に「Core Ultra 200S Plus」品薄も――大型連休明けのストレージとメモリ最新動向 (2026年05月09日)

- まるで工芸品な3kg超のアルミ塊! 官能的すぎる“磁気×メカニカル”なキーボード「Lofree Hyzen」を試す (2026年05月07日)

- VAIO事業が絶好調のノジマ、第4四半期の出荷台数は過去最高に 「AI PC」需要で次期も成長を見込む (2026年05月07日)

- 「SwitchBot スマートサーキュレーター(スタンド型)」を試す インテリアになじむ木目調、扇風機の代わりはなる? (2026年05月08日)

- 16型で約1.2kg、USキーボード搭載! こだわり派のあなたに適した「LG gram Pro 16」が33%オフの19万9800円に (2026年05月08日)

- Microsoftが4月度のWindows非セキュリティプレビューパッチを公開/PCI-SIGが次世代規格「PCI Express 8.0」のドラフト版を公開 (2026年05月10日)

- Microsoftが描く「定額+従量課金」のAI新時代と、無制限の“エッジAI”へと向かうWindowsのゆくえ (2026年05月08日)

- M5Stack、AI連携にも対応したデスクトップロボット「M5 スタックチャン」 (2026年05月08日)