2024年に「ムーアの法則」が再び走り出す? Intelが「PowerVia」の近況を報告 Meteor Lake(仮)のEコアをベースに実証実験:RibbonFETは分離

Intelは6月5日(米国太平洋時間)、同社が2024年に生産を開始する予定の半導体プロセスで使われる裏面電源供給技術「PowerVia」の近況を明らかにした。2023年内に発売予定の「Metor Lake」の高効率コア(Eコア)をベースにテストチップを作成し、裏面電源供給の有効性が確認できたという。本件に関する論文は、6月11日〜16日に京都で開催される「2023 Symposium on VLSI Technology and Circuits」に合わせて公開される。

理屈ではメリットが多いが……

PowerViaは、Intelが2024年に生産を開始する予定の新プロセス「Intel 20A」で採用される予定の技術で、新たな電源半導体「RibbonFET」とセットで用いることでコンパクトでも高い性能を備えるCPUを実現するという。

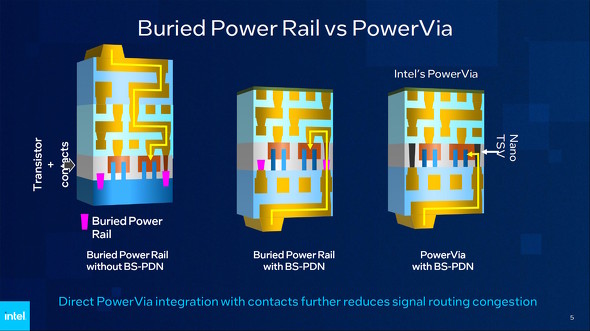

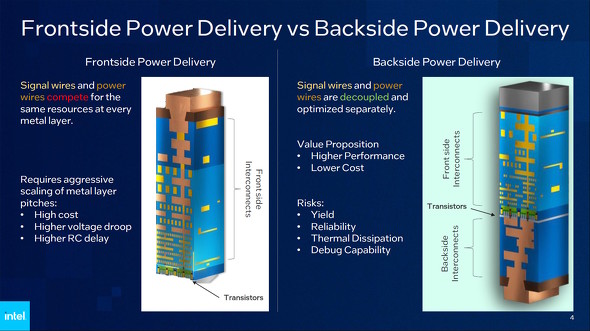

従来のトランジスタ技術では、動作に必要な電力線と信号線は基板の“表面”に配置される。しかし、プロセスの微細化が進むにつれて、1本の電力線と信号線が「競合」関係になり、互いに足を引っ張ってパフォーマンスの低下を引き起こしてしまうという問題が発生しているという。

パフォーマンスの低下を抑える方法としては、「電力をより多く突っ込む」という方法もある。しかし、それではCPUの消費電力(と発熱)がより高まってしまうため、現実的とはいえない。

もう1つの方法として、複数の半導体メーカーは電力線を半導体の裏面に移す「裏面電源供給(Backside Power)」の実現を考えてきた。信号線は表面、電力線は裏面とすることで相互の干渉を抑え、消費電力を抑えつつパフォーマンスを向上できるようにしようという算段である。Intelも例外でなく、「PowerVia」と銘打って検討を続けてきた。

「なぜ、分かっていてやらなかったのか?」というと、「現在の作り方の方が簡単で、今までは問題なかったから」だそうだ。

片面実装(左)と裏面電源供給(右)の長短比較。裏面電源供給は「理論上は性能向上(と消費電力やコストの低下)に有利だが、今まで作ったことがない」ということで、発熱特性や信頼性といった開発する上で参考にすべきデータの蓄積がないことが実現への課題であるようだ

片面実装(左)と裏面電源供給(右)の長短比較。裏面電源供給は「理論上は性能向上(と消費電力やコストの低下)に有利だが、今まで作ったことがない」ということで、発熱特性や信頼性といった開発する上で参考にすべきデータの蓄積がないことが実現への課題であるようだ「ピザ作りをやめる」

しかし、裏面電源供給のトランジスタを作らないことには、今後のCPUの性能向上は難しくなってしまう。そこでIntelは「ピザ(≒片面実装のトランジスタ)作り」をやめ、裏面電源供給(PowerVia)トランジスタの技術開発と実装に注力することにしたという。

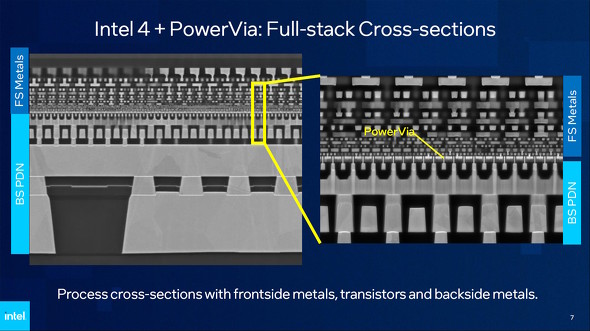

PowerViaを適用したトランジスタ作りは、まずウエハー上にトランジスタを構築し、そこに信号線(相互接続層)を追加する。ここまでは、従来の作り方と変わりない。

信号線を追加した後、PowerViaではウエハーを“ひっくり返して”研磨を行い、電力線をつなぐための層が露出したら、信号線を載っける。ゆえに「ウエハー上に残るシリコンは微量」となる。

「ムーアの法則」が再来?

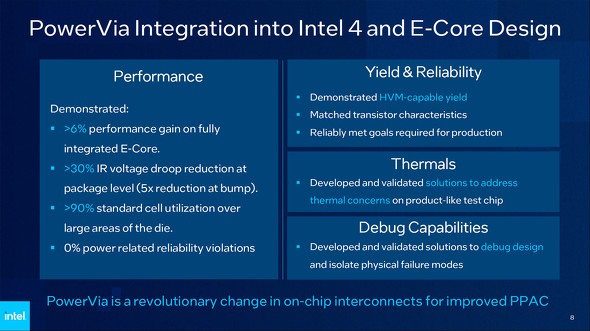

先述の通り、IntelはMeteor LakeのEコアをベースにPowerViaのテストチップとして「Blue Sky Creek」を作った。この実験を通して、同社は以下の結果を得られたという。

- 本来の設計(=オリジナルのEコア)比で6%超のパフォーマンス向上

- パッケージ段階で最大30%超の電圧低下を抑制

- 標準セルの90%超の有効化を確認

- 電力に関わる不正動作はなし

Intelとしては「より少ない電力で作業を早く完了できるようになるという観点で、(多くのユーザーにとっての)『ムーアの法則』を再び実現できる」としている。

なお、このチップには検証チームに気付かれないように「意図的なバグ」を仕込んでいたようだが、検証チームはそれをしっかり見つけられたとのことで、万が一不具合が発生した場合でも検証を問題なく行えそうとのことだ。

PowerViaの開発はRibbonFETから“切り離し”

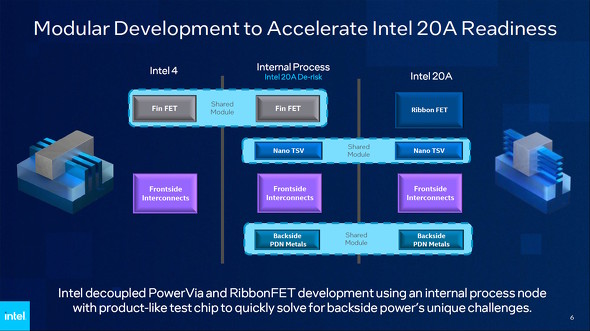

裏面電源供給には、チップの発熱特性や信頼性といった、開発上において参考にすべきデータの蓄積がないことが課題としてある。そこでIntelでは、当初計画ではセット実装を前提としていたPowerViaとRibbonFETの開発を“分離”して進めることになった。

分離した結果が先述のBlue Sky Creekの誕生で、これにより「PowerViaの有効性を先んじて確認できた」としている。また、RibbonFETを実装するIntel 20Aプロセスとの“中間”存在として従来のトランジスタ(FinFET)を搭載した「Intel 20A De-risk(リスク回避版)」も設計できるようになったそうだ。

関連記事

Intelが次世代CPU「Meteor Lake」の概要をチラ見せ 全モデルに「AIエンジン」を搭載

Intelが次世代CPU「Meteor Lake」の概要をチラ見せ 全モデルに「AIエンジン」を搭載

Intelが「Meteor Lake(メテオレイク)」というコード名で開発を進めているCPUの概要情報を公開した。同社初の7nmプロセスCPUは、全モデルにCPUコアとは別体の「AIエンジン」を搭載するという。 2025年までに「1.8nm相当」に――Intelが半導体生産のロードマップを説明

2025年までに「1.8nm相当」に――Intelが半導体生産のロードマップを説明

Intelが半導体生産のロードマップを説明するイベントを開催した。2022年には7nmプロセスの製品が、2024年には新技術を取り入れた製品が登場する見通しだ。 イスラエルのIntelハイファラボで見た“ちょっと未来”のPC像

イスラエルのIntelハイファラボで見た“ちょっと未来”のPC像

Intelはイスラエルに一大拠点を構えている。先日、報道関係者向けにその現状を伝えるツアーが開催されたが、今回は「Intel 8088」や「MMX Pentium」などを生み出したハイファにあるIDC(Israel Development Center)において実際に研究/開発された技術のデモンストレーションの様子をお伝えする。 AI処理パフォーマンスを大きく改善 4nmプロセスのモバイルAPU「Ryzen 7040シリーズ」登場 搭載製品は3月以降に登場

AI処理パフォーマンスを大きく改善 4nmプロセスのモバイルAPU「Ryzen 7040シリーズ」登場 搭載製品は3月以降に登場

AMDの最新CPUアーキテクチャ「Zen 4」が、いよいよモバイル向けに登場する。メインストリームとなるRyzen 7040シリーズでは、CPUコアが4nmプロセスとなり省電力性能が高まった他、最新の「RDNA 3アーキテクチャ」のGPUや独立したAIアクセラレーターも統合していることも特徴だ。 Intelが「第4世代Xeonスケーラブルプロセッサ」を正式発表 後から機能を拡張できる「Intel On Demand」対応モデルも

Intelが「第4世代Xeonスケーラブルプロセッサ」を正式発表 後から機能を拡張できる「Intel On Demand」対応モデルも

Intelが、データセンター(サーバ)/HPC向けCPU「Xeonスケーラブルプロセッサ」の第4世代製品を正式に発表した。先行リリースされたHBM2付きの「Xeon CPU Max」と合わせて、一部モデルを除き後から機能を追加できる「Intel On Demand」にも対応する。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- キーボード「FILCO」ブランドのダイヤテックが閉業 4月22日付で (2026年04月24日)

- 次期「DaVinci Resolve 21」で写真編集が可能に/Google Cloudが第8世代TPUを発表 (2026年04月26日)

- 大型連休前のアキバは新CPUラッシュ! AMD「Ryzen 9 9950X3D2」とIntel「Core Ultra 5 250K Plus/KF Plus」の気になる在庫状況 (2026年04月25日)

- 持ち運びを極めた超軽量キーボード「ロジクール KEYS TO GO 2」が17%オフの9980円に (2026年04月23日)

- ACアダプター不要の外付けHDD「Seagate One Touch Desktop External Hard Drive」を試す 超大容量で配線スッキリ (2026年04月24日)

- Windows 11の使い勝手はどう変わる? 「Copilot」名称外しやInsider Program再編に見るMicrosoftの本気度 (2026年04月24日)

- 「Apple AirPods 4」が20%オフの2万3798円に (2026年04月24日)

- 2026年版Surfaceはどうなる? 正面衝突を避けるMicrosoft、10万円切り「MacBook Neo」対抗への秘策はあるか (2026年04月21日)

- 部屋の雰囲気を一瞬で変えられる「SwitchBot RGBIC フロアライト」が15%オフの7633円に (2026年04月24日)

- Microsoftの新日本語IME「Copilot Keyboard」が正式版に “お前を消す方法”で有名なキャラ「カイル」も追加 (2026年04月23日)