「80コア」の誤解と真実:IDF Fall 2006(2/2 ページ)

「パフォーマンス向上=コア数の増加」となるか

今回のIDFではさまざまな要素技術が登場し、おぼろげながら将来におけるCPUの姿を垣間見ることができた。Intelはこれらどのように組み合わせて、どんなCPUを作り上げようとしているのだろうか。

最近、米国で開催された「Hotchips」などの半導体会議で話題になるのは、CPUにおけるIPC(Instruction Per Cycle:1サイクルあたりの実行可能な命令数)の上昇カーブが限界に差し掛かっており、もはや並列化以外にCPUのパフォーマンスを向上させる手段はないだろうとの予測だ。またIntelがPentium 4でクロック周波数のアップに挫折したように、消費電力と発熱の問題も重くのしかかる。高速処理のためにトランジスタ数を増やせば発熱量は増大する。クロック周波数を増やせない以上、コア数を増やしてCPU全体でのパフォーマンスを稼ぐ方向へと向かうのは自然の成り行きだ。Intelだけでなく、業界全体がメニーコアへと向かうのは避けられない流れとなる。

だが、メニーコアの実現にはいくつかの方向性がある。それがCPU上のすべてのコアに同じ機能を与える「ホモジニアス・マルチコア」と機能別に異なる種類のコアを集める「ヘテロジニアス・マルチコア」の選択だ。現状のIntelやAMDのCPUは、すべてのコアが等価なホモジニアス・マルチコアである。一方で、PlayStation 3への搭載が予定されているCellプロセッサは、専用の演算ユニットを複数搭載したヘテロジニアス・マルチコアである。AMDでは、将来的にCPUの機能をコンポーネント化し、いずれはヘテロジニアス・マルチコアへと向かう可能性を示唆している。では、Intelはどうするのだろうか?

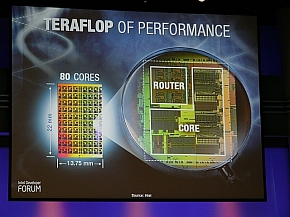

IntelCTOのジャスティン・ラトナー氏によれば、どちらの方法を選択するかは検討中だという。前述のリング型とメッシュ型のCPU間通信のトポロジも含め、あらゆる可能性を模索するのがプロトタイプの役割だという。同氏によれば、プロトタイプの中身はIA-32非互換のホモジニアスなコアの集合体で、基本的な整数演算機能のみを備え、浮動小数点演算ユニットは内蔵していないという。各コアにはルーティング機能を司るユニットが備え付けられており、どのコアからでもダイ・スタッキングされた別のコアのメモリユニットにランダムアクセスが可能だと述べていることから、一種のメッシュ型ネットワークが張り巡らされていることが分かる。おそらく、今後のIntelのメニーコアはこのプロトタイプを改良していき、技術的にはその延長線上にあるものだと考えられるだろう。

コア数と単位コアあたりの性能のバランス

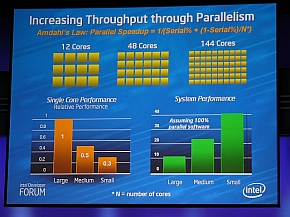

メニーコアを語るうえでもう1つのトピックが、コア数と単位コアあたりの性能でどうやってバランスをとるかだ。ダイのサイズが一定である以上、(製造プロセスルールが同じという条件下で)そこに搭載可能なトランジスタの数はほぼ一意に決まる。ならば、単位コアあたりの性能が“そこそこ”なコアの搭載数を増やすか、あるいは搭載するコアの数を抑えて単位コアあたりの性能を増やすかという2つの方向性を模索する必要が出てくる。

Intelがどちらの方向を目指しているのかは、その比較グラフを見れば一目瞭然だろう。例えば12コアに分割されたCPUがあったとき、1コアあたりの性能を1とすれば、48コア分割では1コアあたりの性能は0.5となる。だがCPU全体でみたとき、もしシステムの並列動作度を100%とすれば、その性能はコアの数だけ増加し、トータルでは12コア分割のCPUと比較して約2倍のパフォーマンスとなる。この傾向は、コアを分割すればするほど顕著となる。

では、コアを分割すればするだけパフォーマンスの上昇が望めるかというと、そういうわけにもいかない。1つは、現状のアプリケーションのほとんどが並列動作を前提としていない点だ。そのために、並列動作における効率が100%に達することはおそらくない。とくにデスクトップPCやノートPCなどの個人用途の場合、クアッドコアでさえ手持ち無沙汰という状態だろう。今後メニーコアのメリットを生かすためには、まずアプリケーションの並列動作を可能にする大きなパラダイムシフトが要求されることになる。

これと同じ理由で、あまりにコアを分割して単位コアあたりの性能を落としてしまうと、既存のアプリケーションがまともに使えなくなるという弊害が出てくる。例えば、サンマイクロシステムズが発表した超並列型プロセッサ「UltraSPARC T1」(開発コード名:Niagara)の後継である「UltraSPARC T2」(開発コード名:Niagara 2)では、コアの数を従来の8個のままで単位コアあたりの性能を向上させる方向で改良を進めている。このような形で進化したのは、コアの性能を落としすぎると動作可能なアプリケーションの種類が限定される、という難点があったからだといわれている。目指す方向としては、現状のコア性能を維持しつつ、コア数を増やしていく感じになるだろう。

メニーコア・プロセッサはいつ登場する?

80コアのCPUが、現状の製造プロセスルールと現状のCPUと同程度のダイサイズで実現できたのは、コアの構造を単純化したためである。もしIA-32コアをメニーコア化する場合、現状のコアの性能を維持するのであれば、コアのトランジスタ数が大きく変動することはない。今後、製造プロセスルールの微細化で単位面積あたりに搭載可能なトランジスタ数が増加するまで、コア数を大きく増やすことは難しい。32ナノメートルプロセスルールが登場する2009年、あるいはその次の22ナノプロセスルールが登場する2011年以降まで待たなければならないだろう。それまでは4コアや8コア、12コアといったレベルでコア数が推移することになると考えられる。そのころにはさまざまな課題を克服して、システムあたりのコア数がパフォーマンスの目安となる時代になっているかもしれない。

関連記事

- 「Viiv」「情報家電」「データセンター」Intelが掲げる三題噺のオチどころ

- IDFで示されたモバイルを快適にする技術

- UMPCとモバイルWiMAXで「新しいモバイル」がやってくる

- 技術セッションで明らかにされた「Core2 Quad」の構造と性能

- クアッドコアは11月に登場、80コア搭載CPUのプロトタイプも公開──オッテリーニ氏基調講演

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- 画面を持たない約12gの超軽量ウェルネストラッカー「Google Fitbit Air」 1万6800円で5月26日に発売 (2026年05月07日)

- USB Type-Cの映像出力をワイヤレスでHDMI入力できる「エレコム ワイヤレス HDMI 送受信機セット DH-CW4K110EBK」がセールで1万2580円に (2026年05月08日)

- NAS向け低容量HDD枯渇に「Core Ultra 200S Plus」品薄も――大型連休明けのストレージとメモリ最新動向 (2026年05月09日)

- まるで工芸品な3kg超のアルミ塊! 官能的すぎる“磁気×メカニカル”なキーボード「Lofree Hyzen」を試す (2026年05月07日)

- VAIO事業が絶好調のノジマ、第4四半期の出荷台数は過去最高に 「AI PC」需要で次期も成長を見込む (2026年05月07日)

- 「SwitchBot スマートサーキュレーター(スタンド型)」を試す インテリアになじむ木目調、扇風機の代わりはなる? (2026年05月08日)

- Microsoftが4月度のWindows非セキュリティプレビューパッチを公開/PCI-SIGが次世代規格「PCI Express 8.0」のドラフト版を公開 (2026年05月10日)

- 16型で約1.2kg、USキーボード搭載! こだわり派のあなたに適した「LG gram Pro 16」が33%オフの19万9800円に (2026年05月08日)

- Microsoftが描く「定額+従量課金」のAI新時代と、無制限の“エッジAI”へと向かうWindowsのゆくえ (2026年05月08日)

- モジュール型ミニPC「Khadas Mind」をSurface風に変貌させる拡張ディスプレイ「Mind xPlay」レビュー (2026年05月06日)