45ナノメートル以降のプロセス技術をひもとく──マーク・ボーア氏基調講演:Intel Developers Forum 北京

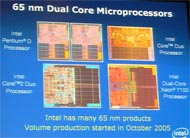

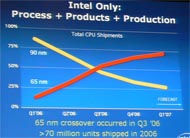

現行の65ナノメートルは最高の歩留まりを実現

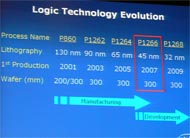

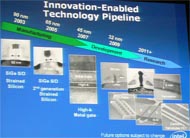

ボーア氏によると、Intelは研究・開発・量産の3ステップで2年おきにムーアの法則に従ってプロセスサイズを縮小し続けており、現在では65ナノメートルの製造、45ナノメートルの開発、32/22ナノメートルの研究が行われているという。同社のFabのほとんどが米国に集中しているが、IDFでは2010年に大連で稼働予定のFab 68を紹介し、さらにはアセンブリ/テスト拠点は成都、上海をはじめとする中国各都市や東南アジアを中心に展開するだけでなく、北京大学、精華大学、復旦大学など40以上の学術機関と共同研究を行っているとして、同社と中国との結びつきを強調した。

Intelの製造ステップは研究・開発・量産の3段階があり、それらが平行して行われている(写真=左)。主要なFabは北米に集まっているが、アセンブリ/テスト拠点はアジア地域にも見られる(写真=中央)。2007年内に登場予定の45ナノメートルの製造プロセスは開発が終わりつつあり、次世代の32ナノメートルも開発が進んでいる(写真=右)

Intelの製造ステップは研究・開発・量産の3段階があり、それらが平行して行われている(写真=左)。主要なFabは北米に集まっているが、アセンブリ/テスト拠点はアジア地域にも見られる(写真=中央)。2007年内に登場予定の45ナノメートルの製造プロセスは開発が終わりつつあり、次世代の32ナノメートルも開発が進んでいる(写真=右)続いてプロセス技術の解説に入り、すでに量産が行われている130/90/65ナノメートルプロセスのトランジスタと配線に採用されている素材や技術の説明が画像とともに紹介された。なかでも2005年10月に量産を開始した65ナノメートルは、同社最高の歩留まり(不良発生率が低い)を実現したという。

45ナノ/32ナノメートルの製造プロセスではさまざまな新技術を導入

一方、2007年内に登場が予定されている45ナノメートルでは、トランジスタや配線技術が変更される。トランジスタ数と集積率を約2倍にしたほか、トランジスタのオン/オフ切り替え時の消費電力を最大30%低減し、トランジスタ切り替えスピードを20%向上させ、ソース/ドレイン間のリーク電流を5分の1、ゲート部分のリーク電流を10分の1に抑えている。

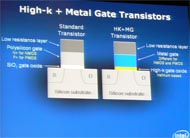

これらを実現するために新たに投入されたのが、Intelが2003年に世界に先駆けて動作に成功したHigh-k素材の「メタルゲートトランジスタ」だ。これはゲート部分に金属を用いることでソース/ドレイン間の電界効果を高め、リーク電流を低減する。一般的なトランジスタはSiO2酸化膜ゲート、ポリシリコンゲート、誘電層の3層構造となっているが、High-kメタルゲートトランジスタではハフニウム(Hafnium)ベースの酸化膜、メタルゲート、誘電層という構造になっている。

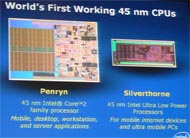

なお、45ナノメートルでは、Core 2ファミリーに属する「Penryn」とUMPC向けの超低消費電力CPU「Silerthorne」が製造され、2007年第2四半期より米オレゴン州のD1D、米アリゾナ州のFab 32、2008年第1四半期よりイスラエルのFab 28、2008年第2四半期より米ニューメキシコ州のFab 11Xで生産を開始する予定だ。

45ナノで製造される最初のCPUは、次世代のPenrynとUMPC向けのSilverthorne(写真=左:いずれも開発コード名)。一般的なトランジスタと45ナノメートルで採用されたメタルゲートトランジスタの比較図(写真=中央)。45ナノメートルのユニットは右の写真にある4カ所のFabで製造される

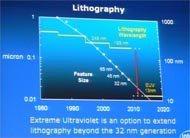

45ナノで製造される最初のCPUは、次世代のPenrynとUMPC向けのSilverthorne(写真=左:いずれも開発コード名)。一般的なトランジスタと45ナノメートルで採用されたメタルゲートトランジスタの比較図(写真=中央)。45ナノメートルのユニットは右の写真にある4カ所のFabで製造されるさらに、2009年に登場予定の32ナノメートルで採用される技術についても語られた。現在半導体の製造に使われている露光装置では、波長幅がプロセスルールよりも大きい193ナノメートルとなっているため、正確な露光が行えるのは45ナノメートルプロセスが限界だった。そこで32ナノメートルでは、対物レンズとシリコンウエハーの間に液体をはさむことで解像度を高める「液浸露光技術」を取り入れ、現在の露光装置が使えるように工夫された。

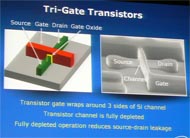

しかし、さらに微細化を推し進めるためは波長幅13ナノメートルの極端紫外線を用いたEUV露光システムの導入が検討されている。このほか、ソース/ドレインリーク電流が少ないトライゲートトランジスタや少ない電力でも高いパフォーマンスが得られるInSb(アンチモン化インジウム)Quantum Wellトランジスタなどの開発も行われているとのことだ。

次世代の32ナノまでは現在の露光装置による波長幅193ナノが利用され、より微細化した製造プロセスではEUV露光システムが導入される予定だ(写真=左)。トライゲートトランジスタの模式図(写真=中央)。製造プロセスのロードマップ(写真=右)

次世代の32ナノまでは現在の露光装置による波長幅193ナノが利用され、より微細化した製造プロセスではEUV露光システムが導入される予定だ(写真=左)。トライゲートトランジスタの模式図(写真=中央)。製造プロセスのロードマップ(写真=右)関連記事

UMPC向けプラットフォーム「Intel Ultra Mobile Platform 2007」を正式発表──チャンドラシーカ氏基調講演

UMPC向けプラットフォーム「Intel Ultra Mobile Platform 2007」を正式発表──チャンドラシーカ氏基調講演

2日間の日程で行われたIDF 2007 Beijingにおいて、最も話題を呼んだのがアナンド・チャンドラシーカ氏による新しいUMPCプラットフォームの発表だ。 “Intel Inside”を家電にも──エリック・キム氏基調講演

“Intel Inside”を家電にも──エリック・キム氏基調講演

家電向けのSoC「Intel CE 2110メディアプロセッサ」がついに登場した。“Intel Inside”がPC分野以外にも突き進む。 Intelにとっての「You」は中国……か

Intelにとっての「You」は中国……か

Intel CTOのジャスティン・ラトナー氏による基調講演では、中国とIntelの密接な関係を示すデモが数多く行われた。 ノートPCの普及とともにモバイルアーキテクチャも進化──IDFがいよいよスタート

ノートPCの普及とともにモバイルアーキテクチャも進化──IDFがいよいよスタート

IDF Beijing(北京)2007の開幕前夜となる16日、インテルのムーリー・エデン氏が現在のモバイル・プラットフォームを取り巻く状況と将来の展望について語った。 2007年はインテルが業界を力強く引っ張っていく

2007年はインテルが業界を力強く引っ張っていく

インテルは4月11日に定例の「インテルクライアント・レギュラー・アップデート」を行った。会場では“Robson”“Kedron”“Yorkfield”“Wolfdale”といったサンプルモジュールが披露された。 見えてきたPenrynとNehalemの「革新性」

見えてきたPenrynとNehalemの「革新性」

インテルが45ナノCPUとして予定している「Nehalem」は「Pentium Pro」以来の変革が施される。そのキーワード“組み合わせ”はCPUに何をもたらすのだろうか。 45ナノで知るIntelとAMDの“工場哲学”

45ナノで知るIntelとAMDの“工場哲学”

45ナノプロセスルールを採用したCPUは、インテルから2007年に、AMDから2008年に登場するといわれている。その“タイムラグ”に両社の開発思想を見る。 Intelが45ナノ「Penryn」ダイ画像を公開

Intelが45ナノ「Penryn」ダイ画像を公開

Intelは2007年に投入予定の45ナノプロセスルールプロセッサの試作と動作確認を発表。「Penryn」スペックの一部も明らかにした。![新約・見てわかる パソコン解体新書:Coreマイクロアーキテクチャ [前編]](https://image.itmedia.co.jp/pcuser/articles/0611/01/news005.gif) 新約・見てわかる パソコン解体新書:Coreマイクロアーキテクチャ [前編]

新約・見てわかる パソコン解体新書:Coreマイクロアーキテクチャ [前編]

オンライン版「見てわかるパソコン解体新書」の第2回目は、インテルのCoreマイクロアーキテクチャを取り上げます![新約・見てわかる パソコン解体新書:Coreマイクロアーキテクチャ に迫る[後編]](https://image.itmedia.co.jp/pcuser/articles/0701/24/news002.gif) 新約・見てわかる パソコン解体新書:Coreマイクロアーキテクチャ に迫る[後編]

新約・見てわかる パソコン解体新書:Coreマイクロアーキテクチャ に迫る[後編]

オンライン版「見てわかるパソコン解体新書」の第3回目は、インテルのCoreマイクロアーキテクチャに迫ります。 クアッドコアの最高峰「Core2 Extreme QX6800」の性能を知る

クアッドコアの最高峰「Core2 Extreme QX6800」の性能を知る

インテルは“Core 2 Extreme”の最新製品となるQX6800を発表した。Kentsfeildの開発コード名で知られるCore 2 Extreme QX6700の後継で、動作クロックが2.93GHzに引き上げられたことが特徴だ。 中国のCPUとインテルのFabとの微妙な関係

中国のCPUとインテルのFabとの微妙な関係

中国が独自に開発したCPU「龍芯」が製品化され、搭載PCがリリースされた。その龍芯と先日発表されたインテルの“中国Fab”建設は決して無関係ではないのだ。- インテル、ノートPC向け新ブランド「Centrino Pro」発表――管理機能/セキュリティ機能を装備

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- 画面を持たない約12gの超軽量ウェルネストラッカー「Google Fitbit Air」 1万6800円で5月26日に発売 (2026年05月07日)

- USB Type-Cの映像出力をワイヤレスでHDMI入力できる「エレコム ワイヤレス HDMI 送受信機セット DH-CW4K110EBK」がセールで1万2580円に (2026年05月08日)

- NAS向け低容量HDD枯渇に「Core Ultra 200S Plus」品薄も――大型連休明けのストレージとメモリ最新動向 (2026年05月09日)

- まるで工芸品な3kg超のアルミ塊! 官能的すぎる“磁気×メカニカル”なキーボード「Lofree Hyzen」を試す (2026年05月07日)

- VAIO事業が絶好調のノジマ、第4四半期の出荷台数は過去最高に 「AI PC」需要で次期も成長を見込む (2026年05月07日)

- 「SwitchBot スマートサーキュレーター(スタンド型)」を試す インテリアになじむ木目調、扇風機の代わりはなる? (2026年05月08日)

- 16型で約1.2kg、USキーボード搭載! こだわり派のあなたに適した「LG gram Pro 16」が33%オフの19万9800円に (2026年05月08日)

- Microsoftが4月度のWindows非セキュリティプレビューパッチを公開/PCI-SIGが次世代規格「PCI Express 8.0」のドラフト版を公開 (2026年05月10日)

- Microsoftが描く「定額+従量課金」のAI新時代と、無制限の“エッジAI”へと向かうWindowsのゆくえ (2026年05月08日)

- モジュール型ミニPC「Khadas Mind」をSurface風に変貌させる拡張ディスプレイ「Mind xPlay」レビュー (2026年05月06日)