Intel次世代プロセッサでUltrabookやタブレットはどう変わる?:IDF Beijing 2013(2/2 ページ)

微細化を加速するモバイルSoCと、鍵を握る省電力技術

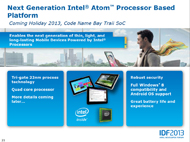

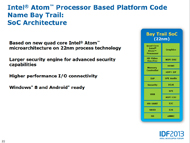

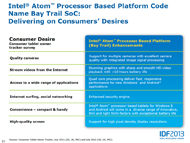

Intelは、22ナノメートルプロセス世代のSoCとして、スマートフォン向けの“Merryfield”(開発コード名)や“Bay Trail”の存在を明らかにしたが、その機能の詳細は公開されなかった。しかし、同社の技術展示では、

1、CPUアーキテクチャは現行のAtomプロセッサやCoreプロセッサとも異なるまったく新しいアーキテクチャとなる

2、クアッドコアモデルが用意され、現行世代の2倍以上のパフォーマンスを実現する

3、グラフィックスコアは、Ivy Bridge世代と同じIntel HDグラフィックスベースとなり、2〜3倍の性能アップが図られる

4、I/O機能が強化される

などが明らかにされた。

ここで疑問となるのが、現在、Imagination TechnologiesのPowerVR SGX540などを採用しているグラフィックス機能を、Intel HDグラフィックスに変更することで、消費電力が増大しないかということだ。

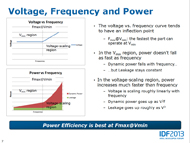

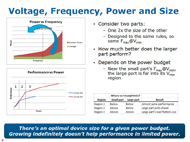

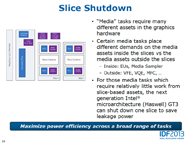

しかし、同社でシステムエンジニアを務めるジャッキー・ロマーノ氏は、「グラフィックスコアは、一定レベル以上に周波数を上げようとすると、急激に電圧が上がるポイントがある。このしきい値をベースに、演算ユニット数を増やすなどすれば、より効率的なグラフィックスコア設計が可能になる」と説明。さらに、同社が「スライス」と呼ぶグラフィックスコア構成する演算ユニットなどの各ブロックを積極的にアイドル状態にしたり、グラフィックス機能などは専用処理ユニットを搭載するなどすることで、大幅な省電力化が図れると説明する。

同様に、CPUコアについても「クアッドコア化を図る一方で、現在AtomプロセッサがサポートしているHyper Theadingは無効化され、より細かな単位でCPUコアの電力制御が施される見通しだ」と、同社に近いOEM関係者が語っており、大幅なアーキテクチャ強化が図られる見通しだ。

次世代グラフィックスの開発においては、タブレットやスマートフォンの熱設計にもあうよう省電力性の追究が求められる(写真=左)。グラフィックスコアの電圧と周波数の関係。一定以上の周波数に達すると、急激にグラフィックスコアが必要とする電圧が上がり、自ずと消費電力が上がってしまう(写真=中央)。グラフィックスコアのトランジスタ数(ここではサイズとされている)を増やし、コア数を増やしたほうが、少ないトランジスタ数でパフォーマンスを引き上げるより、消費電力あたりのパフォーマンスを高めやすい(写真=右)

次世代グラフィックスの開発においては、タブレットやスマートフォンの熱設計にもあうよう省電力性の追究が求められる(写真=左)。グラフィックスコアの電圧と周波数の関係。一定以上の周波数に達すると、急激にグラフィックスコアが必要とする電圧が上がり、自ずと消費電力が上がってしまう(写真=中央)。グラフィックスコアのトランジスタ数(ここではサイズとされている)を増やし、コア数を増やしたほうが、少ないトランジスタ数でパフォーマンスを引き上げるより、消費電力あたりのパフォーマンスを高めやすい(写真=右)

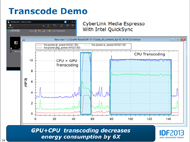

ビデオトランスコードのデモ。CPUとGPUを活用したビデオトランスコードのほうが、ピークの消費電力は高いが、処理時間が短いため、消費電力は低くなる。なお、消費電力は青い部分の面積で示されている部分だ(写真=左)。グラフィックスコアを構成するブロックを、積極的にアイドル状態にすることで、省電力化を図ることもできると説明(写真=右)

ビデオトランスコードのデモ。CPUとGPUを活用したビデオトランスコードのほうが、ピークの消費電力は高いが、処理時間が短いため、消費電力は低くなる。なお、消費電力は青い部分の面積で示されている部分だ(写真=左)。グラフィックスコアを構成するブロックを、積極的にアイドル状態にすることで、省電力化を図ることもできると説明(写真=右)さらにモバイルデバイスでは、メモリも省電力化における重要な要素となる。現在、高機能タブレットでは1080pを超える解像度をサポートする液晶ディスプレイを搭載する製品も多くなってきており、このまま高解像度液晶がスタンダードになっていけば、メモリ帯域に対する要求も大きくなる。

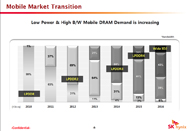

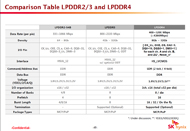

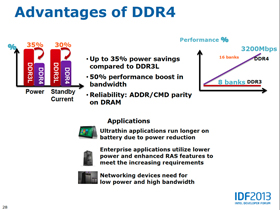

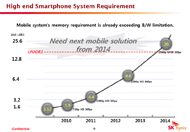

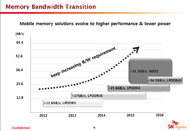

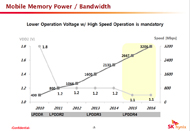

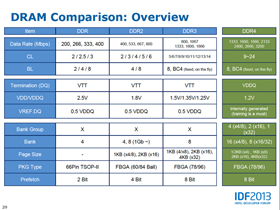

しかし、メモリをデュアルチャネル構成で搭載すると、それだけSoCやシステムの消費電力も大きくなり、より広帯域で低消費電力なメモリが必要とされる。このため、PC業界のみならず、モバイル機器業界でもDDR4への移行が真剣に検討されはじめており、2014年末〜2015年にはLPDDR3に変わるソリューションとしてLPDDR4が採用し始められるとみる。LPDDR4は、現在メモリの標準化団体であるJEDECで規格策定が進められているDDR4メモリの低電圧版で、1.1ボルト駆動で3200Mbps〜4266Mbpsの帯域を実現。4Kディスプレイ表示に必要な20Gbpsの帯域も1ワット以下の消費電力で実現できるという。

4Kディスプレイ表示には20Gbpsのメモリ帯域が必要とされるため、LPDDR3よりも高速なメモリが必要になる(写真=左)。次世代モバイル機器向けメモリのデータ帯域ロードマップ(写真=中央)。LPDDR4は2014末〜2015年には2667Mbpsの帯域を実現しつつ、駆動電圧は1.1ボルトに下がり、省電力化にも貢献する(写真=右)

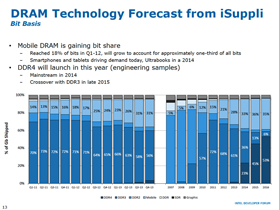

4Kディスプレイ表示には20Gbpsのメモリ帯域が必要とされるため、LPDDR3よりも高速なメモリが必要になる(写真=左)。次世代モバイル機器向けメモリのデータ帯域ロードマップ(写真=中央)。LPDDR4は2014末〜2015年には2667Mbpsの帯域を実現しつつ、駆動電圧は1.1ボルトに下がり、省電力化にも貢献する(写真=右)一方、Intelでメモリロードマップなどを見ている担当するジェフ・フィンドリー氏は、米調査会社iSupplyのデータを紹介しながら「DDR3メモリは1866MHzで頭打ちになっており、詳細な製品情報などは公開できないが、2014年にはDDR4への移行が開始されるとみられる」と語り、いよいよDDR4への移行が開始される見通しであることを明らかにした。

米iSupplyのDRAM技術の推移予測。2014年にはDDR4がメインストリーム市場に普及し始めると予測(写真=左)。DDR4の基本仕様。駆動電圧は1.2ボルトとなり、最大3200Mbpsのデータ帯域を実現する(写真=右)

米iSupplyのDRAM技術の推移予測。2014年にはDDR4がメインストリーム市場に普及し始めると予測(写真=左)。DDR4の基本仕様。駆動電圧は1.2ボルトとなり、最大3200Mbpsのデータ帯域を実現する(写真=右)関連キーワード

Intel | Haswell | Intel 8シリーズ | Bay Trail | Intel Z87 Express | Atom | Intel Developer Forum

関連記事

IDF Beijing 2013続報:第4世代CoreはスマホからPCをオーバークロック可能 (1/2)

IDF Beijing 2013続報:第4世代CoreはスマホからPCをオーバークロック可能 (1/2)

北京で開催中の「Intel Developer Forum」で、“Haswell”ことIntelの次期主力CPU「第4世代Coreプロセッサー」に関する情報が大幅にアップデートされた。OC機能拡張を中心に紹介。 Haswell最上位のグラフィックス性能をデモ:第4世代Coreプロセッサーは第2四半期に登場

Haswell最上位のグラフィックス性能をデモ:第4世代Coreプロセッサーは第2四半期に登場

Intelが“Haswell”こと「第4世代Coreプロセッサー」に関する情報をアップデート。CPUパッケージ上にエンベデッドDRAMを搭載するモデルの存在を明らかにした。 インテルとAMDとNVIDIAの次の一手は?:大解説! 省電力なCPUとSoCの最新事情を整理する

インテルとAMDとNVIDIAの次の一手は?:大解説! 省電力なCPUとSoCの最新事情を整理する

PCが大きく変わろうとしている。タブレット市場の急速な伸びがPC市場に影響を与え、インテルもAMDもNVIDIAもタブレットデバイスを視野に入れたCPUの強化を図っている。 「Haswell」より重要かもしれない「Lexington」

「Haswell」より重要かもしれない「Lexington」

2013年のIntelは、「Haswell」のリリースが最重要課題……、というのは間違いないが、それに劣らず、いや、それ以上に重要な課題を抱えているのかもしれない。 CeBIT 2013:MSIのブースで“わけの分からない”マザーボードを見つけた

CeBIT 2013:MSIのブースで“わけの分からない”マザーボードを見つけた

自作PCユーザー的には、Intel 8シリーズらしきチップセットを搭載したマザーボードが主役のCeBIT 2013で、MSIは最新ゲーミングモデルを展示した……、だけかと思ったら! 未発表なチップセットを載せたっぽいマザーボード図鑑──ASRock編

未発表なチップセットを載せたっぽいマザーボード図鑑──ASRock編

Intel 8シリーズ“らしき”チップセットを搭載したマザーボードは、見せたあとで「アレはちょっと」とベンダーも戸惑う微妙なブツらしいが、とにかく元気にいってみよう。 未発表なチップセットを載せたっぽいマザーボード図鑑──BIOSTAR編

未発表なチップセットを載せたっぽいマザーボード図鑑──BIOSTAR編

CeBIT 2013で自作PCユーザーが最も注目したいのがIntel 8シリーズ“らしき”チップセットを搭載したマザーボードだ。その概要をBIOSTARのブースでチェックした。 GIGABYTE、“Z87”マザーボードを公開

GIGABYTE、“Z87”マザーボードを公開

CeBIT 2013に合わせて、各ベンダーが開発中のマザーボードを公開している。ブースがないGIGABYTEもプライベートミーティングでラインアップを明らかにした。 Intel 8シリーズ“らしき”チップセット搭載マザーボード現る

Intel 8シリーズ“らしき”チップセット搭載マザーボード現る

CeBIT 2013が始まった。事前の“うわさ”通りに、PCパーツベンダーは、Intelの未発表チップセットと“思われる”型番を掲げるマザーボードを展示している。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- 32GBメモリが6万円切り、2TB SSDは3.3万円から 価格上昇が続くアキバで見つけた高コスパパーツ (2026年02月07日)

- スパコン「富岳」×モーションキャプチャで見えた金メダルへの「空気のつかみ方」 (2026年02月08日)

- アドビが「Animateの販売終了」を撤回/メモリ高騰を受けRaspberry Piの一部モデルが再値上げ (2026年02月08日)

- ロジクールの「MX MASTER 4」とマウスパッドのセットが1万9400円に (2026年02月06日)

- 宅内ネットワーク環境の10G化に適した「TP-Link DS108X」が13%オフの4万803円に (2026年02月06日)

- JIS配列の2つ折りキーボード「Ewin 折りたたみ Bluetooth キーボード」が32%オフの2699円に (2026年02月06日)

- ソニーとTCLの合弁が意味する「新しいソニー」の完成形――ソニーが“家電企業”の殻を脱いだ日 (2026年02月06日)

- 自宅のどこでも本格サウンドが楽しめる「Bose SoundLink Home Bluetooth Speaker」が3.3万→2.3万円に (2026年02月05日)

- Insta360初ドローン「Antigravity A1」実機レポ 360度カメラが生む“空中を自由に見渡す”没入感とは? (2026年02月06日)

- NECPCが11.1型プレミアムAndroidタブレット「LAVIE Tab EX」を発表 16型スタンダードノートPCや液晶一体型デスクトップPCも (2026年02月03日)