GPUの新時代を切り開く「Turing」アーキテクチャ徹底解説(2/2 ページ)

Turing GPUの命名規則

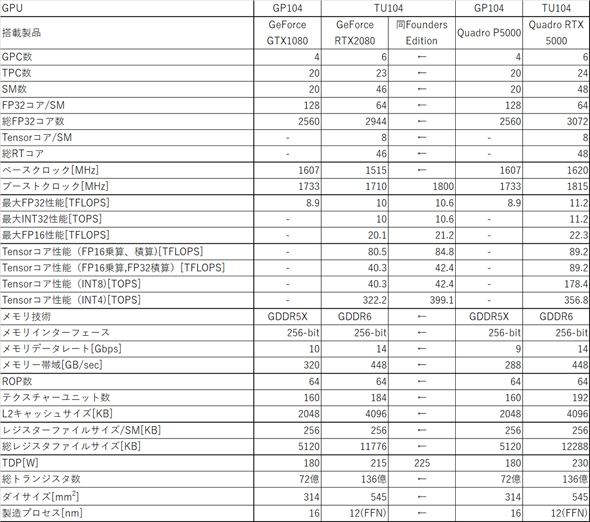

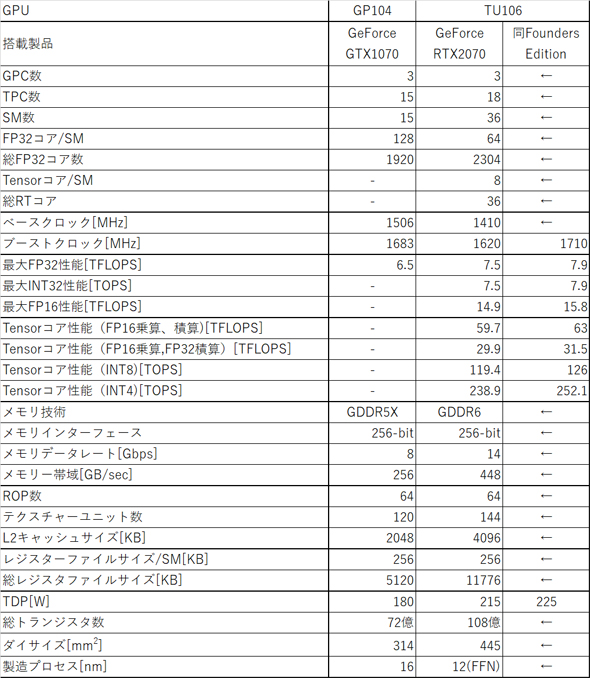

Turingアーキテクチャで作られたGPUデバイスには「TU102」「TU104」「TU106」の3つがある。TU102はQuadro RTX 6000、GeForce RTX 2080 Tiに、TU104はQuadro RTX 5000、GeForce RTX 2080に、TU106はGeForce RTX 2070に搭載されている(それぞれファウンダーズエディションを含む)。

NVIDIAのGPUチップには、アルファベット2文字と数字3桁の番号が付けられている。先頭の2文字は、アーキテクチャを表し、例えば、前世代のVoltaアーキテクチャでは「GV」、Pascalでは「GP」となっていた。このルールだと、Turingも「GT」になりそうだが、「GT」はTeslaアーキテクチャで既に使われているため「TU」となったようだ。

次の数字3桁は、バージョンと用途を表す。この数字は科学技術演算向けのGPUでは100など、下2桁が「00」となり、グラフィックス向けでは、「102」以降の数字が使われる。このため、「TU102」は、Turing世代のグラフィックス向けGPUチップであると判断できる。

また、これまでの慣習からすると、102はグラフィックス向けの最上位チップとなり、以下簡略化されたものが104、106という番号になる。基本的なアーキテクチャというか、SMの構造は同じだが、SMの数が違う。SMはグラフィックス処理を並列化して行っているため、SM数が多いほど高性能になる。なお、実際には、それぞれのGPUをGPUボード製品にする場合に、搭載メモリや動作クロックなどの違いがあり、さらにバリエーションが増えている。

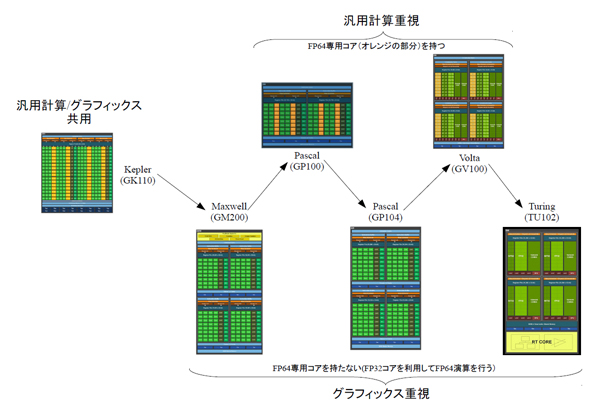

NVIDIAのGPUアーキテクチャは、Maxwell世代から科学技術演算を目的としたチップとグラフィックスボード向けのチップに分かれている。科学技術演算向けはTeslaシリーズなどに使われ、 グラフィックスボード向けのチップは、GeForceシリーズなどに利用される。両者は、同じアーキテクチャながら、SMの構造などに違いがある。

NVIDIAのGPUは、Maxwell世代から汎用計算向けとグラフィックス向けの2系統に分かれた。Maxwellはグラフィックス向けのみだったが、Pascal世代では汎用計算向け、グラフィックス向けの両方のGPUが開発された。TU102は、グラフィックス向けのGPUと考えられる

NVIDIAのGPUは、Maxwell世代から汎用計算向けとグラフィックス向けの2系統に分かれた。Maxwellはグラフィックス向けのみだったが、Pascal世代では汎用計算向け、グラフィックス向けの両方のGPUが開発された。TU102は、グラフィックス向けのGPUと考えられる最も大きな違いは、倍精度浮動小数点(Double precision floating number。DP)のための演算コアを内蔵しているかどうかだ。科学技術演算では、DP演算は必須で、これを高速化するために独立したコアを持つ。しかし、グラフィックス処理では、DP演算は不要であるため、これを装備しない。しかし、汎用計算を行う場合、SP演算用のコアを利用してDP演算を行わせることができ、ソフトウェア的な互換姓は保たれている。

しかし、DP演算の速度はあまり速くならず、SP演算の1/32程度になってしまう。これに対して科学技術計算向けのGPUでは、DP演算の速度は、SP演算の1/3〜1/2程度にとどまる。

なお、NVIDIAでは、SP、DPをFP32、FP64と表記することが多い。これは、浮動小数点を表現するビット数にちなみ、Floating Point 32bit、同64bitという意味だ。また、「半精度浮動小数点」(Half precision floating number)をFP16と表記する。

その他、整数(Integer number)演算も32bit〜4bitをINT32〜INT4として表記する。NVIDIAが公開する資料などでは、このような表記が行われることがあるので注意されたい。以後、本記事でも、NVIDIAの表記に合わせFP32、FP64という表記を使う。

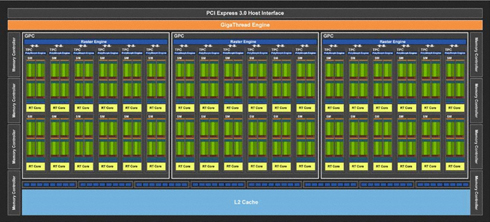

こうした背景があるため、NVIDIAは、TuringをPascalと比較している。Voltaは、グラフィックス向けのバージョンとなるGV102などが予想されてはいるものの、現時点では、まだ発表が行われておらず、汎用計算向けのGV100のみが公開されている状態だ。また、Pascalも最初に発表された汎用計算向けのGP100とグラフィックス向けのGP102では、内部構造が大きく違い、むしろ、GP102のSMは、MaxwellのSMによく似ている。

まずは、NVIDIAのGPUの特徴であるSMを見ることにする。同じグラフィックス系アーキテクチャとなるPascalのSMと比較すると大きく違っている。

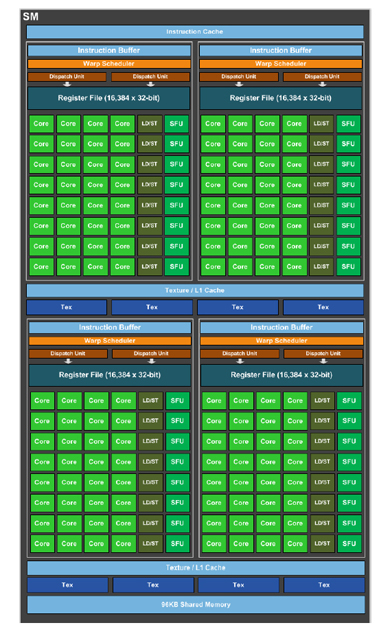

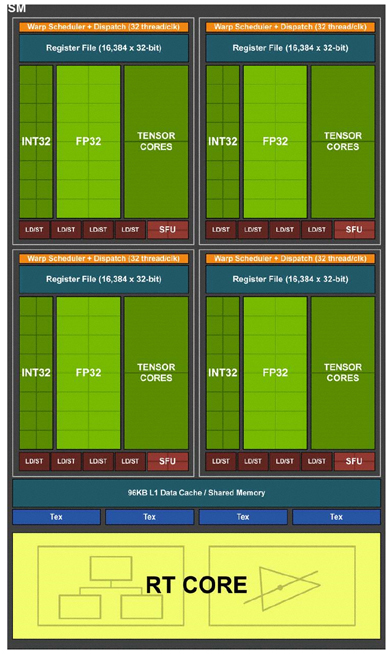

TU102のSM。下がレイトレーシング用のRTコア。4つのWARPスケジューラーがあり、それぞれにFP32、INT32、Tensorコアがある。LDSTは、データアクセス用の「Load/Storeユニット」、SFUは、三角関数などを計算する「Special Function Unit」である

TU102のSM。下がレイトレーシング用のRTコア。4つのWARPスケジューラーがあり、それぞれにFP32、INT32、Tensorコアがある。LDSTは、データアクセス用の「Load/Storeユニット」、SFUは、三角関数などを計算する「Special Function Unit」であるむしろ、TuringのSMは、構造的には、VoltaのSMに似ている。しかし、大きな違いとして倍精度演算コアを持たない。

Volta GV100のSM。こちらは、汎用計算向けなので倍精度浮動小数点演算用のFP64ユニットがある。しかし、INT32、FP32コアが分かれ、Tensorコアがある、WARPスケジューラーの下にはDispatchユニットが1つしかないなど、TU102のSMとよく似ている

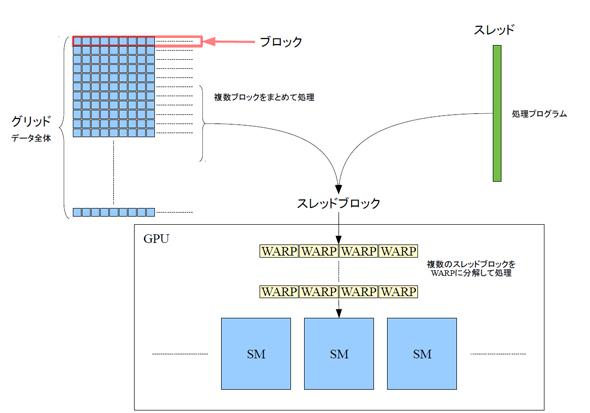

Volta GV100のSM。こちらは、汎用計算向けなので倍精度浮動小数点演算用のFP64ユニットがある。しかし、INT32、FP32コアが分かれ、Tensorコアがある、WARPスケジューラーの下にはDispatchユニットが1つしかないなど、TU102のSMとよく似ているSMは、最大1024個のデータ(これをブロックという)を複数同時に処理することができる(処理できるブロックの数はアーキテクチャにより違いがある)。それぞれを処理するプログラムは「スレッド」とよばれ、ブロックを処理するスレッドを「スレッド・ブロック」という。つまり、同じプログラムを多数のデータに対して適用するわけだ。

NVIDIA GPUは、データ全体(グリッドと呼ばれる)を分割したブロックを複数同時に1つのスレッドプログラムで処理する。ブロックに含まれるデータの数だけプログラムが同時に実行されるが、GPU内部では、これを32スレッドのWARPに分割して実行する。SMが多ければ、同時に処理できるスレッドブロックの数が多くなり、結果的に処理性能が向上する

NVIDIA GPUは、データ全体(グリッドと呼ばれる)を分割したブロックを複数同時に1つのスレッドプログラムで処理する。ブロックに含まれるデータの数だけプログラムが同時に実行されるが、GPU内部では、これを32スレッドのWARPに分割して実行する。SMが多ければ、同時に処理できるスレッドブロックの数が多くなり、結果的に処理性能が向上するただし、SMは、スレッドブロックを32スレッドをひとまとまりとした「WARP」という単位に分解して実行していく。このとき、WARPを実行するのが「WARP」スケジューラーであり、WARPスケジューラーの下でディスパッチャーが演算コアに命令を発効する。アーキテクチャにより、SMが持つWARPスケジューラーの数やそれぞれのWARPスケジューラーが持つディスパッチャーの数が違う。しかし、ソフトウェア上は、こうした違いはみえないようになっている。

Turing SMのWARPスケジューラーは4つで、個々のWARPスケジューラーが持つディスパッチャーは1つしかない。Pascal(GP102)の場合、WARPスケジューラーは4つだが、ディスパッチャーはそれぞれに2つあり、同一スレッドの2つの命令を最大2つ処理させることが可能だ。

こうした違いは、SM内部の演算コアの数に関係がある。GP102では、各WARPスケジューラーに対して、32個のCUDAコア(FP32またはINT32の演算を行える)があるため、32スレッドからなるWARPのFP32またはINT32の命令を1サイクルで行うことが可能だ。これに対してTuringのSMでは、WARPスケジューラーに対して、FP32コアが16、INT32コアが16となっており、32スレッドのWARP内のFP32、INT32命令は2サイクルに分けて処理される。

ただし、PascalのCUDAコアは、一度には、FP32かINT32演算かのどちらかしか実行できないのに対して、Turingでは、FP32コアとINT32コアは並行して動作できる。さらにGPU全体としてみると、TU102は72個とGP102の30個と2倍以上のSMを持つ。このため、SM単体の処理性能がほとんど変わらなくても、TU102は、GP102よりも高い性能を出すことができる。

もう1つ、TuringのSMには、4×4のFP16データの内積計算が行えるTensorコアがあり、これを使うことで、Pascalでは複数命令で行っていた演算を1命令で処理できるようになっている。Tensorコアは、最大130.5TFLOPSで内積計算を行えるため、これを使うことで演算処理が高速化される。特に画像処理のような行列演算では、内積計算は多用される演算だ。

TuringのTensorコアは、改良が行われている。VoltaのTensorコアは演算対象が16bitのFP16のみだったが、Turingでは、2つのINT8(8bit×2)または4つのINT4(4bit×4)として行列演算を行う機能がある。こうした短い整数データは、ディープラーニングの推論処理などに使われる。

また、GP102とTU102では、動作クロック周波数に違いがあり、通常時のクロック周波数は、TU102のほうが低い(1455MHzと1506MHz)が、ブースト時のクロックは、TU102のほうが高い(1770MHzと1645MHz)。このため、FP32演算で比較すると、TU102が最大16.3TFLOPSであるのに対してGP102は12.6TFLOPSとなっている。

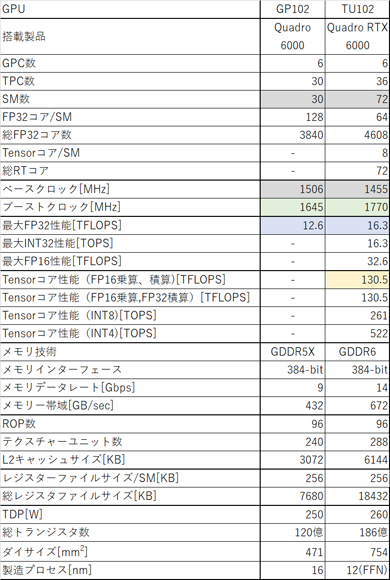

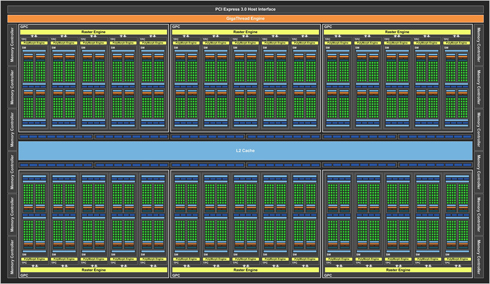

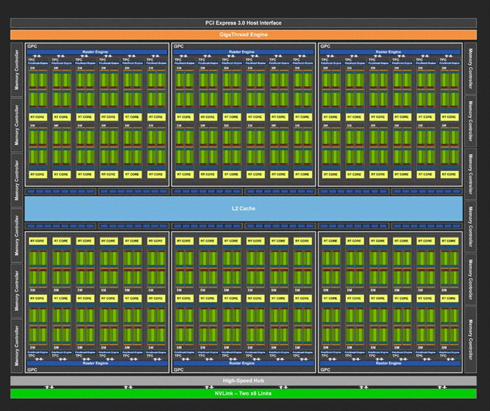

次にGPU全体を見てみよう。TU102は下のような構造を持つ。

TU102は、6つのGPC(Graphics Processing Cluaster)からなり、内部に12個のSMを持ちGPU全体では72個のSMを持つ。GPCはグラフィックス処理時にはラスター単位で処理を行う

TU102は、6つのGPC(Graphics Processing Cluaster)からなり、内部に12個のSMを持ちGPU全体では72個のSMを持つ。GPCはグラフィックス処理時にはラスター単位で処理を行うNVIDIA GPUは、SMを複数組みあわせたGPC(Graphics Processing Claster)から構成されている。グラフィックスを扱う場合に、このGPCがラスター単位で処理を行う。TU102には、6つのGPCがあり、それぞれに12個のSMがあり、GPU全体では、72個のSMがある。

これに対して、GP102の場合、6つのGPCのそれぞれに5つのSMがあり、GPU内部には30個のSMがある。さらに、TU102には、合計で12個のメモリコントローラーがあるのに対して、GP102には8つのメモリコンローラーしかない。その他、L2キャッシュのサイズにも違いがある。

もう1つは、TU102にはVoltaと同じくNVLinkが搭載されていることだ。PascalのGP100にもNVLinkはあったが、グラフィックス系のGP102/104ではNVLinkが省略されていた。

多数のSMを搭載できたのは、TU102が12nmプロセスで製造されているからだ。これに対してGP102は、16nmの製造だった。しかし、ダイサイズは、TU102が754平方mmと、GP102の471平方mmよりも大きくなっている。トランジスタ数で比較すると、GP102が120億トランジスタであるのに対して、TU102は、186億のトランジスタから構成されている。

TuringアーキテクチャのGPUには、TU102の他、TU104とTU106がある。それぞれSMは同一で、TU104はGPC数はTU102と同じく6だがGPC内のSM数が8個に減らされている。TU106はGPCの構造は同一だが、3つだけになっている。それぞれのスペックとPascal世代との比較を下の表に示す。

Turingアーキテクチャは、レイトレーシングという新たな技術をPCにもたらし、よりリアルなアニメーションなどを可能にした。ラスターグラフィックスのみだったGPUの新時代を開いたといってもいいだろう。

ニュース解説番組「NEWS TV」で記事をピックアップ

ITmedia NEWS編集部がYouTubeでお届けするライブ番組「ITmedia NEWS TV」で、この記事を取り上げています。ぜひ視聴・チャンネル登録をお願いします。

関連記事

NVIDIAが新アーキテクチャの「GeForce RTX」シリーズを発表 価格は499ドルから

NVIDIAが新アーキテクチャの「GeForce RTX」シリーズを発表 価格は499ドルから

NVIDIAがTuringアーキテクチャを採用する新GPU「GeForce RTX」シリーズを発表した。今回発表されたラインアップは3モデルで、価格は499ドル〜999ドル。 NVIDIAが第8世代GPUアーキテクチャ「Turing」を発表 Pascal世代の6倍のスピードで現実世界をシミュレート

NVIDIAが第8世代GPUアーキテクチャ「Turing」を発表 Pascal世代の6倍のスピードで現実世界をシミュレート

NVIDIAはレイトレーシング用の「RTコア」とAI用の「Tensorコア」を搭載する「NVIDIA Turing GPU」アーキテクチャを発表した。Turingベースの製品は2018年第4四半期出荷予定。 NVIDIAが過去最高の四半期売上高32億1000万ドル AIコンピューティング需要が追い風

NVIDIAが過去最高の四半期売上高32億1000万ドル AIコンピューティング需要が追い風

NVIDIAは、2018年四半期の業績を発表。前年同期比66%増の32億1000万ドルの売り上げを達成した。 NVIDIA、次世代VR HMD向けのオープンな新業界規格「VirtualLink」 USB Type-Cケーブル1本で接続が可能

NVIDIA、次世代VR HMD向けのオープンな新業界規格「VirtualLink」 USB Type-Cケーブル1本で接続が可能

NVIDIAが参画する業界コンソーシアムが、VRヘッドセット向けの業界規格「VirtualLink」の発表を行った。 宇宙人が見つからないのは仮想通貨マイニングのせい?

宇宙人が見つからないのは仮想通貨マイニングのせい?

仮想通貨マイニングの需要増によるGPU不足は思わぬところにも影響を及ぼしています。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- キーボード「FILCO」ブランドのダイヤテックが閉業 4月22日付で (2026年04月24日)

- サイボウズの社名由来 “坊主”に込められた意味が深すぎる (2016年07月29日)

- 発表時の批判は裏返る? スペック据え置きでも“買い”と言える、極上の普段着スマホ「Pixel 10a」を触ってみた (2026年04月27日)

- 次期「DaVinci Resolve 21」で写真編集が可能に/Google Cloudが第8世代TPUを発表 (2026年04月26日)

- 大型連休前のアキバは新CPUラッシュ! AMD「Ryzen 9 9950X3D2」とIntel「Core Ultra 5 250K Plus/KF Plus」の気になる在庫状況 (2026年04月25日)

- マザーボードは「細部まで白」が今の主流? 高コスパ水冷など見逃せない最新自作PCパーツ事情 (2026年04月27日)

- 持ち運びを極めた超軽量キーボード「ロジクール KEYS TO GO 2」が17%オフの9980円に (2026年04月23日)

- エレコム、士郎正宗デザインマウス「M.A.P.P.」復刻モデルの予約販売を4月6日に開始 (2026年03月25日)

- Windows 11の使い勝手はどう変わる? 「Copilot」名称外しやInsider Program再編に見るMicrosoftの本気度 (2026年04月24日)

- 部屋の雰囲気を一瞬で変えられる「SwitchBot RGBIC フロアライト」が15%オフの7633円に (2026年04月24日)