2種類のコアで「省電力」と「高パフォーマンス」を両立――Intelが「Alder Lake」の概要を公開 「Sapphire Rapids」にも新情報(3/3 ページ)

» 2021年08月19日 23時30分 公開

[井上翔,ITmedia]

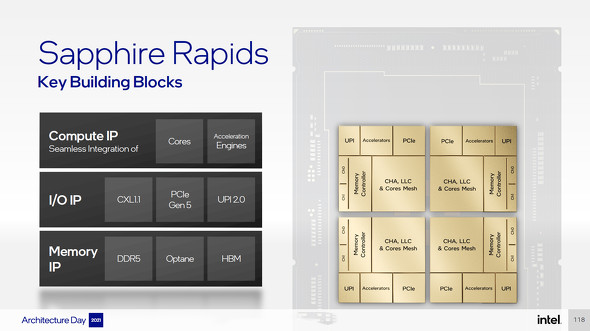

タイル設計でスケーラビリティーを高めたSapphire Rapids

既に「次世代Xeonスケーラブルプロセッサ」として情報の小出しが行われているSapphire Rapidsについても、プロセッサの構造に関する情報が明らかとなった。

Sapphire Rapidsは、先述のハイパフォーマンスコアを主体とするCPUだ。設計自体はAlder Lakeと同じ考え方で、用途に合わせて必要なタイルを組み合わせるようになった。これにより、従来のXeonプロセッサよりもスケーラビリティーが高まっている。

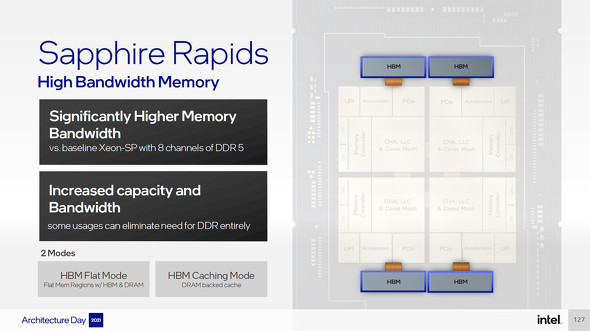

以前の記事でも触れた通り、Sapphire RapidsにはHBM(広帯域メモリ)を備えるモデル(SKU)が登場する予定となっている。

Alder Lakeと同様に、Sapphire RapidsもDDR5メモリをサポートしているが、HBMへのアクセス帯域幅は8チャネル構成のDDR5メモリと比べて「とても広い」。用途によってはDDRメモリが“不要”になる可能性もあるという。

関連記事

Intelが一般向け高性能グラフィックス製品ブランド「Arc」を立ち上げ 2022年第1四半期に製品投入

Intelが一般向け高性能グラフィックス製品ブランド「Arc」を立ち上げ 2022年第1四半期に製品投入

Intelが、コンシューマー向けの高性能グラフィックス製品ブランド「Intel Arc」を立ち上げる。ブランドの初製品は、2022年第1四半期に登場する予定だ。 2025年までに「1.8nm相当」に――Intelが半導体生産のロードマップを説明

2025年までに「1.8nm相当」に――Intelが半導体生産のロードマップを説明

Intelが半導体生産のロードマップを説明するイベントを開催した。2022年には7nmプロセスの製品が、2024年には新技術を取り入れた製品が登場する見通しだ。 Intelが「次世代Xeonプロセッサ(Sapphire Rapids)」をチラ見せ 広帯域メモリ内蔵バージョンを用意

Intelが「次世代Xeonプロセッサ(Sapphire Rapids)」をチラ見せ 広帯域メモリ内蔵バージョンを用意

スーパーコンピューターの世界的なイベント「ISC 2021」に合わせて、IntelがHPC(ハイパフォーマンスコンピューティング)に関する取り組みを発表した。その中で、次世代のXeonスケーラブルプロセッサ(開発コード名:Sapphire Rapids)にHBM(広帯域メモリ)を内蔵するバージョンが用意されることが明らかとなった。 Intelが次世代のクライアントPC向けCPU「Alder Lake」を2021年に投入

Intelが次世代のクライアントPC向けCPU「Alder Lake」を2021年に投入

Intelは8月13日(現地時間)、オンラインイベント「Intel Architecture Day 2020」を開催し、次世代のクライアント向け製品「Alder Lake」について発表した。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

SpecialPR

SpecialPR

アクセストップ10

2026年04月08日 更新

- 「ANAオリジナル タフなビジネスリュック」を試す 収納力もバツグンで鳥肌が立つほどにカッコいい (2026年04月07日)

- レノボが「ThinkPad」2026年モデルを一挙発表! 12年ぶりの構造刷新やUSB Type-Cの自力交換対応でメンテナンス性も向上 (2026年04月07日)

- 2台のMac StudioをThunderbolt 5で連結! 計128GBメモリ環境と分散推論「exo」でLLMを爆速化してみた (2026年04月08日)

- GoogleのAシリーズ最新作「Pixel 10a」は7万9900円から カメラの出っ張りが消えて新色も追加 (2026年04月07日)

- FCCLがこだわりのキーボード「FMV Keyboard X」をクラファン形式で販売 約2.3万円から (2026年04月07日)

- ANAがビジネスユースに特化した耐久性重視のビジネスバッグ3製品を発売 (2025年11月14日)

- Blu-ray難民を救う? アイ・オーとVerbatim、ユーザーの不安を払拭する製品供給の継続を発表 (2026年04月08日)

- 「Google Pixel 10a」に日本限定カラー登場! ヘラルボニーとのコラボで多様性を表現する特別な「Isai Blue」(異彩青) (2026年04月07日)

- 待望の「Core Ultra 7 270K Plus」は静かな船出――アキバでは激安ピラーレスケースなど“高コスパ”パーツに熱視線 (2026年04月06日)

- Googleが最新オープンAIモデル「Gemma 4」を公開 (2026年04月06日)

最新トピックスPR