「Radeon」の開発方針は? なぜ「超ハイエンドGPU」で勝負をしない? 「競合」との関係は? AMDのキーマンに聞く(3/5 ページ)

CPUでもGPUでも「チップレット」 しかし“使い方”が異なる

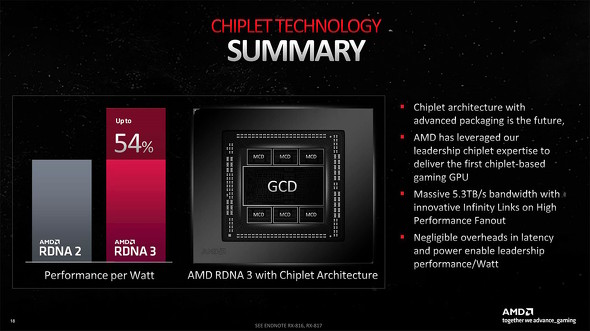

Radeon RX 6900XT/6900 XTXで使われているRDNA 3アーキテクチャに基づくGPUチップ「NAVI31」では、GPUチップとしては初めて「チップレット」と呼ばれるアーキテクチャを採用した。

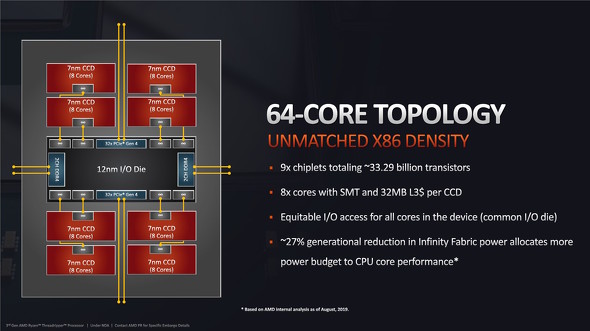

チップレットは構成回路を幾つかのダイに分割し、必要な機能のダイを組み合わせて1枚のチップを構成する考え方で、AMDはZen 2アーキテクチャ以降のCPU(Ryzen 3000シリーズ/Ryzen 4000Gシリーズなど)から採用した。Zen 2以降のCPUでは、最大8コアを備える「CPUダイ(CCX:Core Complex)」と、CPUダイ同士の連結も担う「I/O(入出力)ダイ」を用意し、必要な性能に応じて連結するCPUダイの数を変更するという手法で多コアCPUを低コストで製造することに成功した。

例えば通常のデスクトップ/ノートPC向けRyzenは最大2基(=16コア)、超ハイエンドのRyzen Threadripperシリーズなら最大8基(=64コア)、EPYCシリーズなら最大12基(=96コア)……といった感じである。

Zen 2以降のCPUアーキテクチャでは、中央にI/Oダイを配し、スペックに応じて必要な数のCPUダイ(CCX:Core Complex/CPUコアとL3キャッシュのパッケージ)を連結するという方法で多コアCPUを低コストで製造できるようになっている

Zen 2以降のCPUアーキテクチャでは、中央にI/Oダイを配し、スペックに応じて必要な数のCPUダイ(CCX:Core Complex/CPUコアとL3キャッシュのパッケージ)を連結するという方法で多コアCPUを低コストで製造できるようになっているRDNA 3アーキテクチャの場合は、中心に大きめの「GPUコア(GCD:Grapics Core Die)」を配し、その周辺部に「メモリ&キャッシュコントローラー(MCD)」を置いている。

「RDNA 3アーキテクチャでチップレットが採用される」と判明した際、大方の予想では「Zen 2以降と同じように、GPUコアを必要に応じて増減できる設計では?」とされていた。しかし、少なくともNavi31が登場した段階においてGPUコアを増減できる設計を取る可能性は否定されている。

より高性能なGPUとするために、GPUコアをチップレットで増減できるようにする――有効な手だてだと思えるのだが、なぜそれを見送ったのか。ワン氏に尋ねると、こう返ってきた。

ワン氏 チップレットアーキテクチャは、製造コストを削減しつつ高性能なプロセッサを実現させるために用いることで“真価”を発揮できます。

ご存じの通り、現在のハイエンドGPUコアには1万基以上の演算コア(浮動小数点演算器)が内包されています。これはCPUコアの1000倍以上の数です。この状態でGPUダイ同士をインターコネクト接続(連結)しようとすると、それだけで接続点が膨大になって、確実な電気信号の伝達を担保できません。なので、現時点ではCPUダイと同じノリでGPUダイを連結することは工数はもちろんコスト的にも困難です。やってできないことはないでしょうが……。

そうするくらいなら、現時点では大規模なGPU(コア)を作ってしまった方が効率が良く、コストも抑えられます。ゆえに、現世代(RDNA 3アーキテクチャ)では、「マルチGPUダイ」の実現は見送ることにしました。

バーグマン氏はこう付け足す。

バーグマン氏 半導体ビジネスでは、常に「性能」と「製造コスト」のトレードオフを見極めなければなりません。この分野(マルチGPUダイ)への挑戦については、まだまだ続くし、将来に期待していただければと思います。

関連記事

費用対効果に優れ、動画に強みあり――「Radeon RX 7900 XT」「Radeon RX 7900 XTX」は真に“強い”GPUなのか?

費用対効果に優れ、動画に強みあり――「Radeon RX 7900 XT」「Radeon RX 7900 XTX」は真に“強い”GPUなのか?

AMDの新型GPU「Radeon RX 7900 XT」「Radeon RX 7900 XTX」を搭載するグラフィックスカードが12月16日19時に発売される。それに先駆けて、両GPUを搭載するAMD自社開発グラフィックスカードを使って“実力”をチェックしていこう。 よく見るといろいろと違う? AMD純正の「Radeon RX 7900 XT」「Radeon RX 7900 XTX」搭載グラボを写真でチェック!

よく見るといろいろと違う? AMD純正の「Radeon RX 7900 XT」「Radeon RX 7900 XTX」搭載グラボを写真でチェック!

12月13日(米国時間)、AMDの新型GPU「Radeon RX 7900 XT」「Radeon RX 7900 XTX」を搭載するグラフィックスカードの販売が解禁される。AMDが自社設計したグラフィックスカードを先行レビューできる機会を得たので、まずはその外観を紹介する。 AMDが新GPU「Radeon RX 7000シリーズ」を正式発表 米国では12月13日発売(899ドルから)

AMDが新GPU「Radeon RX 7000シリーズ」を正式発表 米国では12月13日発売(899ドルから)

AMDが新型GPU「Radeon RX 7000シリーズ」を正式に発表した。まずはハイエンド向け製品を2種類投入することになるが、GPUとしては初めて「チップレット設計」を取り入れた他、ハードウェアベースのAV1エンコーダー/デコーダーを搭載するなどゲーム配信を意識した機能強化も図られている。 3090 Tiを華麗に抜き去る「GeForce RTX 4090」の驚異的な性能をチェック!

3090 Tiを華麗に抜き去る「GeForce RTX 4090」の驚異的な性能をチェック!

間もなく「GeForce RTX 4090」を搭載するグラフィックスカードの販売が解禁される。購入するかどうか迷っている人もいると思うので、NVIDIA純正の「GeForce RTX 4090 Founders Edition」を使って、その異次元の性能をチェックした結果をご紹介する。 AMD、「Zen」ベースの次世代プロセッサ「Ryzen」を発表

AMD、「Zen」ベースの次世代プロセッサ「Ryzen」を発表

米AMDは、「Zen」コアアーキテクチャをベースとしたデスクトップ向け次世代プロセッサの発表を行った。

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- キーボード「FILCO」ブランドのダイヤテックが閉業 4月22日付で (2026年04月24日)

- 大型連休前のアキバは新CPUラッシュ! AMD「Ryzen 9 9950X3D2」とIntel「Core Ultra 5 250K Plus/KF Plus」の気になる在庫状況 (2026年04月25日)

- 持ち運びを極めた超軽量キーボード「ロジクール KEYS TO GO 2」が17%オフの9980円に (2026年04月23日)

- ACアダプター不要の外付けHDD「Seagate One Touch Desktop External Hard Drive」を試す 超大容量で配線スッキリ (2026年04月24日)

- 次期「DaVinci Resolve 21」で写真編集が可能に/Google Cloudが第8世代TPUを発表 (2026年04月26日)

- Windows 11の使い勝手はどう変わる? 「Copilot」名称外しやInsider Program再編に見るMicrosoftの本気度 (2026年04月24日)

- 強力なドッキングステーション「Anker PowerExpand Elite 13-in-1 Thunderbolt 3 Dock」が28%オフの2万6490円に (2026年04月23日)

- 部屋の雰囲気を一瞬で変えられる「SwitchBot RGBIC フロアライト」が15%オフの7633円に (2026年04月24日)

- Microsoftの「12インチSurface Pro」「13インチSurface Laptop」が一部販路で値上げ 直販では4万6200円増しに (2026年04月23日)

- Microsoftの新日本語IME「Copilot Keyboard」が正式版に “お前を消す方法”で有名なキャラ「カイル」も追加 (2026年04月23日)