Intelが研究する、最適の電源制御ができる次世代チップとは:IDF Fall 2005

Intelの上級フェローのジャスティン・ラトナー氏は、先週開かれたIntel Developers Forum Fall 2005でユーザー認識プラットフォームの研究成果を披露した。これは動作している環境に応じて変化する適応型アプリケーションを前進させ、ユーザーの様子を観察しながら適切な処理を行う事を目指したものだ。

ラトナー氏は映画「禁断の惑星」に登場するロボット・ロビーを例に挙げながら「ロビーは人間の様子を観察し、常に友人であろうと行動した。ユーザーを認識し、最後は自らを犠牲にしてまで主人を守る行動に出た。これはロビーがユーザー認識を行い、自分の主人を守るという基本的なプログラムが作動したからと考えられる」と話した。

しかしロビーの機能はユーザー認識だけにとどまらない。自己の状態を把握し、自己治癒する能力も備えていたのだ。映画の中では、ロビーが動作するためのオイルを自分自身で交換するシーンが挿入されている。これはIBMをはじめとしてエンタープライズ向けアプリケーションが目指すオートノミックコンピューティングの世界に通じるものだろう。

複雑なハードウェア構成でパフォーマンスと柔軟性を引き出しているデータセンターなどでトラブルが発生した場合、問題点を見つけ、最適な状態で素早く再構成するには自己認識機能を持つトラブル解決の自動化機能が不可欠だ。

自動的に最適な電源制御を行うチップ

ラトナー氏によると、こうした自己の動作を認識し、自動的に最適化するアプローチを、Intelはハードウェア側からも研究開発している。そのうちの1つが、CMOSに実装した新しい電源チップだ。この電源技術が実用化されるようになれば、システム全体の電力を抑えられるだけでなく、将来、マルチコア時代の問題を解決するブレークスルーとなるかもしれない。

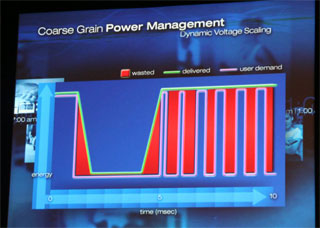

現在でもPC向けプロセッサは動作状況に応じて細かな電源管理を行っている。しかし、その切り替え速度はせいぜいミリ秒オーダーで、激しく変化する負荷状況や動作状況に応じて動作電圧が変化するわけではない。これはチップセットやグラフィックスなども同じことだ。このため、細かい時間単位で見ると、まだまだ削減できる電力はある。

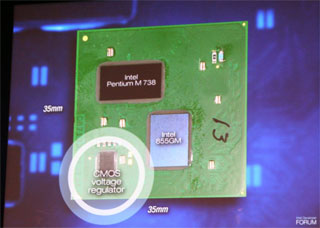

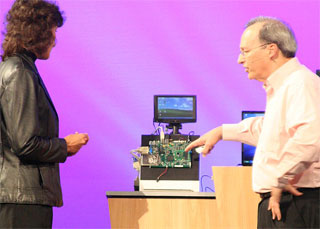

そこでIntelはCMOSチップ上に電圧レギュレーターを作った上で、Pentium M738とi855GM、それにCMOS電圧レギュレーターを、35ミリ角からなるひとつのフリップチップに実装した。通常、マザーボード上にある電解コンデンサやコイル、パワートランジスタはどこにもない。僅かなチップ部品が載っているだけであり、マザーボードのサイズを極小化し、コストダウンも図ることができるだろう。

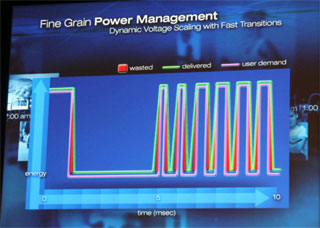

しかし、効果はそれだけではない。Intelが開発したCMOS電源レギュレーターを用い、上記のように各チップとの電源配線を短くすると、ナノ秒オーダーで電圧供給を変化させることができる。これにより各チップの電源管理機能と連動し、細かく動作電圧を変化させることで電力の無駄を最小限に抑えることが可能になる。加えてIR損失も最小化できるため、上記のPentium Mを用いたシステムでは85%以上の電源効率を実現し、通常の設計に比べて最大1時間ものバッテリー駆動時間延長が確認できるという。

ラトナー氏は「これは今すぐに製品として発表できるチップではない」と断った上で「しかし、今後数年にわたってノートPCに順次採用されていくだろう。電源をCMOS化し、それを標準化したソケットにはめ込むだけで使えるようにする」と話した。

さらにIntelは、これをオンチップで埋め込んでいくことも考えているようだ。

高効率の電源制御は次世代CPUに必須

Intelはデュアルコア、マルチコア、そしてメニーコアへとプロセッサを進めていくビジョンを明らかにしているが、現在のところコアごとに独立した電源制御までは行っていない。このため、たとえばデュアルコアプロセッサで片方のコアがSleepしている場合でも、動作電圧は動作中のコアに依存する。しかし、CMOS電源レギュレーターならば、ダイ上に実装された機能ブロックごとに異なる電源設計とすることも可能になる。

メニーコアの時代になると、Intelはx86コアだけでなく、特定の処理用途に特化したコアをいくつか用意し、それを高速なシリアル転送技術を用いたファブリック構成のI/Oで接続することになると見られる。コアの数が増えれば、各コア間の処理負荷にも大きな隔たりが出てくるわけで、それを1系統の電源でまかなうのは効率が悪い。

しかしCMOS電源レギュレーターをオンチップに実装すれば、もっと細かな機能ブロックごとの制御も可能になってくる。さらに同様の機能がチップセットやグラフィックスコアにも入ってくれば、電力の無駄は極限まで下げることが可能だ。

果たしていつごろ実際にそうなるのかというと、それほど遠い話でもないだろう。なぜならこの問題を解決しなければ、Intel自身がプロセッサの進化を前へと進めることができないためだ。Intelの研究開発成果に関する基調講演は、以前はパット・ゲルシンガー氏が行っていたが、そのときには遠い未来の話が多かった。しかしラトナー氏の話は、それよりももっと近い未来を示している事が多い。

2007〜2008年にかけて、こうしたビジョンの実現について、今度は具体的な製品として示せるようになるのではないだろうか。

関連記事

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- 8K/30fpsで撮影できる「Insta360 X4」は想像以上のデキ 気になる発熱と録画可能時間を検証してみたら (2024年04月26日)

- AI PC時代の製品選び 展示会「第33回 Japan IT Week 春」で目にしたもの AI活用やDX化を推進したい企業は要注目! (2024年04月25日)

- Microsoftが「MS-DOS 4.0」をオープンソース化 IBMの協力で (2024年04月26日)

- Micronが232層QLC NAND採用の「Micron 2500 SSD」のサンプル出荷を開始 コスパと性能の両立を重視 (2024年04月26日)

- ワコムが有機ELペンタブレットをついに投入! 「Wacom Movink 13」は約420gの軽量モデルだ (2024年04月24日)

- わずか237gとスマホ並みに軽いモバイルディスプレイ! ユニークの10.5型「UQ-PM10FHDNT-GL」を試す (2024年04月25日)

- エレコム、10GbEポートを備えたWi-Fi 7対応無線LANルーター (2024年04月25日)

- プロセスノードに加えて新技術も売り込む! Intelが半導体の「受託生産」で使う“武器”【後編】 (2024年04月26日)

- あなたのPCのWindows 10/11の「ライセンス」はどうなっている? 調べる方法をチェック! (2023年10月20日)

- QualcommがPC向けSoC「Snapdragon X Plus」を発表 CPUコアを削減しつつも圧倒的なAI処理性能は維持 搭載PCは2024年中盤に登場予定 (2024年04月25日)