Intel、Broadwell世代の「Core M」概要を公開:14ナノプロセスルールで性能改善(2/2 ページ)

» 2014年08月12日 12時00分 公開

[長浜和也,ITmedia]

第2世代トライゲートの導入でパッケージサイズをさらに削減

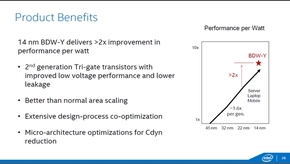

製造技術ではプロセスルールの微細化と第2世代のトライゲートトランジスタの導入でパッケージの底面積がHaswell世代の半分に、高さも30%削減となったほか、電力効率が改善した。また、Turbo Boost Technologyも拡張して消費電力と熱管理の最適化が進んだ。このことで、ワット当たりの処理性能は2倍に向上し、アイドル状態の消費電力は60%も向上したという。

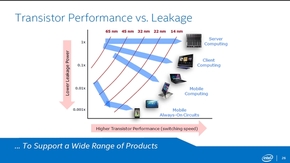

22ナノメートルプロセスルールから14ナノメートルプロセスルールへの移行でワット当たりの性能は2倍に向上する(写真=左)。プロセスルールの縮小とリーク電流の関係。軽量薄型のノートPCに搭載するCPUで、リーク電流の削減が大きく改善する(写真=右)

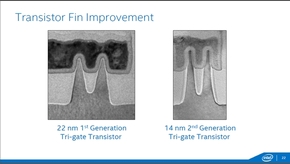

22ナノメートルプロセスルールから14ナノメートルプロセスルールへの移行でワット当たりの性能は2倍に向上する(写真=左)。プロセスルールの縮小とリーク電流の関係。軽量薄型のノートPCに搭載するCPUで、リーク電流の削減が大きく改善する(写真=右)22ナノメートルプロセスルールから14ナノメートルプロセスルールへの移行でパッケージサイズが削減した理由としては、トランジスタのフィン間隔(60ナノメートルから42ナノメートル)やゲート間隔(90ナノメートルから70ナノメートル)、インターコネクト間隔(80ナノメートルから52ナノメートル)と縮小したことが貢献したとIntelは説明している。

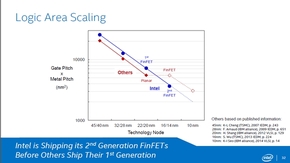

トライゲートトランジスタのフィン間隔を第1世代と第2世代で比較する(写真=左)。プロセスルールの縮小に伴うパッケージサイズの推移。競合は14ナノメートルプロセスルールを導入してもパッケージサイズを縮小できないとインテルは主張する(写真=右)

トライゲートトランジスタのフィン間隔を第1世代と第2世代で比較する(写真=左)。プロセスルールの縮小に伴うパッケージサイズの推移。競合は14ナノメートルプロセスルールを導入してもパッケージサイズを縮小できないとインテルは主張する(写真=右)関連記事

大解説! 次期CPUに対応する新世代“冷却”事情

大解説! 次期CPUに対応する新世代“冷却”事情

“Devil's Canyon”“Broadwell”では、従来の冷却機構が対応できないという。次期CPUに向けたクーラーユニット、PCケース、電源ユニットの動きを解説する。 大復習! Haswell RefreshからDevil's Canyon、Intel 9シリーズチップセットを整理する

大復習! Haswell RefreshからDevil's Canyon、Intel 9シリーズチップセットを整理する

“新しい”第4世代Coreプロセッサー・ファミリーとチップセットは、これまでと何が違うのか? 期待の“アンロック”なCPUとともにおさらいしておこう

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

SpecialPR

SpecialPR

アクセストップ10

2026年03月30日 更新

- 高騰続くPCパーツ市場に変化? DDR5メモリの一部値下がりと依然厳しいストレージ事情 (2026年03月28日)

- 間もなく始まる「Amazon 新生活セール Final」――買い忘れのないように今からチェック! (2026年03月28日)

- MSがWindowsのAI統合戦略を転換、パフォーマンスと信頼性向上に注力/Armが自社設計のCPU「Arm AGI CPU」を発表 (2026年03月29日)

- SNSの死後削除ニーズは5割! コロナ禍で変化した「おひとりさま信託」の実態 (2026年03月29日)

- “パワードスーツ”はもうSFの道具じゃなかった 高尾山でコンシューマー向け外骨格「Hypershell X Pro」を試す (2026年03月27日)

- 10G光回線をフル活用できる「ASUS ROG STRIX GS-BE7200X」が21%オフの2万7818円に (2026年03月27日)

- 「PS5 Pro」は13万7980円に値上げ SIEが4月2日からの価格改定を発表 「日本語専用モデル」は据え置き (2026年03月28日)

- UGREENのポータブルゲーミングPC向けドッキングステーションが33%オフの4424円に (2026年03月27日)

- AMDが最新プロセッサ「Ryzen 9 9950X3D2」を発表 4月22日発売 (2026年03月27日)

- 初音ミクデザインのマウスパッド「ASUS TUF GAMING P1 初音ミクモデル」が21%オフの2848円に (2026年03月27日)

最新トピックスPR