PCI Express 6.0の仕様策定が完了 転送速度は16レーンで最大毎秒256GBに

PCI-SIGは1月11日(米国東部標準時間)、PCI Expressの次世代規格「PCI Express 6.0」の仕様策定が完了したと発表した。2019年5月に仕様が固まった「PCI Express 5.0」の後継となる。

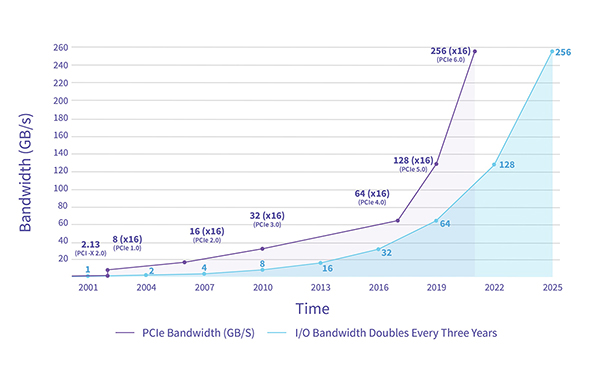

PCI Express 6.0では、データ転送速度を1レーン当たり64GT/s(Giga-Transfer per Second)まで引き上げた。これはPCI Express 5.0(32GT/s)の2倍に当たる。グラフィックスカードの接続で一般的な「×16」構成の場合、最大で毎秒256GBに達する。そして、これまでのPCI Expressと同様に、完全な後方互換性も維持している。

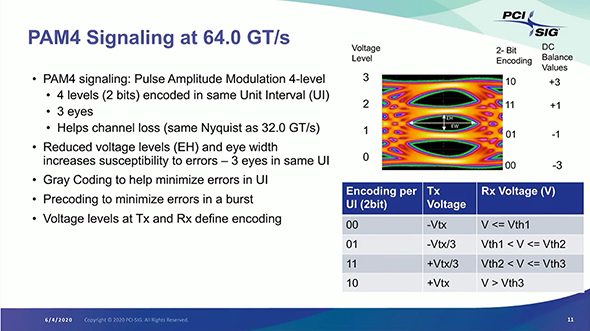

前世代の2倍の性能を達成するために、変調方式を一新した。従来は信号電圧の高低に1bitの0か1を割り当てるNRZ(Non Return to Zero:非ゼロ復帰)方式を採用していたが、今回は信号電圧を4段階とし、それぞれに2bitのデータを割り当てるPAM4(Pulse Amplitude Modulation 4:4値パルス振幅変調)方式を採用した。

これで、サンプリング周波数を上げることなく、データ転送速度を2倍に引き上げることが可能になった。また、エンコードにはFlit(Flow Control Unit)と呼ぶ方式を使っている。

しかし、PAM4では4段階の信号電圧の違いを識別しにくいため、エラーが起こりやすい。そこで、エラーが発生することを見越して誤り訂正符号をデータに付け加えて送信するFEC(Forward Error Correct:前方誤り訂正)を採用した。

この方式なら、エラーが発生したとしても再送を求めることなく、誤り訂正符号からデータを復元すれば良いので、データ転送速度を維持しやすい。さらに、データ転送時のエラーを検出するCRC(Cyclic Redundancy Check:巡回冗長検査)も利用する。

関連記事

Intelがハイエンドデスクトップ向け「第12世代Coreプロセッサ(Alder Lake)」を発表 11月4日から順次出荷開始

Intelがハイエンドデスクトップ向け「第12世代Coreプロセッサ(Alder Lake)」を発表 11月4日から順次出荷開始

Intelが「Alder Lake」という開発コード名のもと開発を進めてきた新型CPUの製品版が、いよいよ登場する。第1弾はアンロック(オーバークロック)対応のハイエンドデスクトップPC向け製品で、一般的なデスクトップPCやノートPC向けの製品は2022年前半に発表される予定だ。 Intelが「次世代Xeonプロセッサ(Sapphire Rapids)」をチラ見せ 広帯域メモリ内蔵バージョンを用意

Intelが「次世代Xeonプロセッサ(Sapphire Rapids)」をチラ見せ 広帯域メモリ内蔵バージョンを用意

スーパーコンピューターの世界的なイベント「ISC 2021」に合わせて、IntelがHPC(ハイパフォーマンスコンピューティング)に関する取り組みを発表した。その中で、次世代のXeonスケーラブルプロセッサ(開発コード名:Sapphire Rapids)にHBM(広帯域メモリ)を内蔵するバージョンが用意されることが明らかとなった。 5nmプロセスの“Zen 4”「Ryzen 7000シリーズ」を2022年後半にリリース 「Ryzen 7 5800X3D」は今春に

5nmプロセスの“Zen 4”「Ryzen 7000シリーズ」を2022年後半にリリース 「Ryzen 7 5800X3D」は今春に

AMDが、現行のZen 3アーキテクチャCPUのL3キャッシュを大幅増量した新CPUを発売する。8コア16スレッド構成ながら、既存の12コア24スレッド製品と同等か上回るゲーミング性能を発揮するという。さらに“次世代”のCPUも、2022年後半に登場する見通しだという。 毎秒10GB超えのPCIe 5.0対応SSDコントローラーを台湾Phison Electronicsが出展

毎秒10GB超えのPCIe 5.0対応SSDコントローラーを台湾Phison Electronicsが出展

台湾Phison Electronicsは1月3日、CES 2022にPCI Express 5.0に対応したSSDコントローラーを出展すると発表した。 ASRockがIntel Z690チップセット+DDR5/DDR4対応マザーボードを発表

ASRockがIntel Z690チップセット+DDR5/DDR4対応マザーボードを発表

ASRockが、Intelから発表されたばかりの第12世代Coreプロセッサ対応のマザーボードを複数投入する。販売日は今後発表の予定だ。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- キーボード「FILCO」ブランドのダイヤテックが閉業 4月22日付で (2026年04月24日)

- 次期「DaVinci Resolve 21」で写真編集が可能に/Google Cloudが第8世代TPUを発表 (2026年04月26日)

- 大型連休前のアキバは新CPUラッシュ! AMD「Ryzen 9 9950X3D2」とIntel「Core Ultra 5 250K Plus/KF Plus」の気になる在庫状況 (2026年04月25日)

- 持ち運びを極めた超軽量キーボード「ロジクール KEYS TO GO 2」が17%オフの9980円に (2026年04月23日)

- ACアダプター不要の外付けHDD「Seagate One Touch Desktop External Hard Drive」を試す 超大容量で配線スッキリ (2026年04月24日)

- Windows 11の使い勝手はどう変わる? 「Copilot」名称外しやInsider Program再編に見るMicrosoftの本気度 (2026年04月24日)

- 「Apple AirPods 4」が20%オフの2万3798円に (2026年04月24日)

- 2026年版Surfaceはどうなる? 正面衝突を避けるMicrosoft、10万円切り「MacBook Neo」対抗への秘策はあるか (2026年04月21日)

- 部屋の雰囲気を一瞬で変えられる「SwitchBot RGBIC フロアライト」が15%オフの7633円に (2026年04月24日)

- 強力なドッキングステーション「Anker PowerExpand Elite 13-in-1 Thunderbolt 3 Dock」が28%オフの2万6490円に (2026年04月23日)