「Meteor Lake」はCPUコアが3種類!? Intelが次世代CPUの詳細を発表(前編):正式発表は12月14日(米国太平洋時間)(2/3 ページ)

Meteor Lakeの「タイルアーキテクチャ」はどこがスゴい?

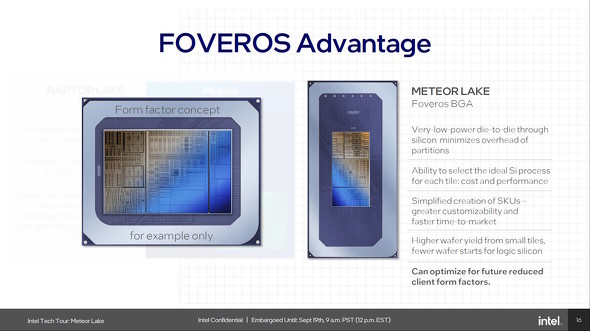

Meteor Lakeにおけるタイルアーキテクチャは、Foverosによって実現したもの。では、具体的に従来のチップレット技術と何が違うのだろうか。もう少し詳しく解説してみよう。

Meteor Lakeでは、主に微細な配線のみ施した「ベースダイ」の上に、機能別に形成されたタイル(チップレット)を載せている。このタイルたちは、ベースダイに対して「マイクロバンプ接合」を行ったり、要所要所ではベースダイを貫通する形で「TSV(Through-Silicon Via)配線」を行ったりしている。

従来のチップレット技術はパッケージ基板を介してチップレット同士を配線していたが、タイルアーキテクチャではベースダイを介してチップレットを接合させている。当然なのことながら構造は複雑となるが、見方を変えるとチップレットとの接合密度を高められる。ゆえに、ベースダイを介して接合されるチップレット間のデータ伝送速度(帯域)を格段に上げられるのだ。

Intelでは各タイルを「機能名+Tile」のような名称で呼んでおり、Meteor Lakeでは以下のタイルをベースダイに集約することで1基のSoCを構成している。

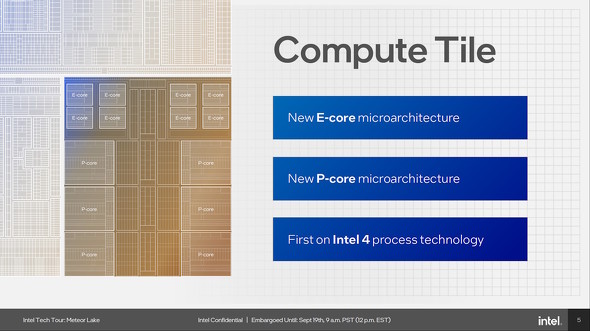

- Compute Tile(コンピュートタイル):CPUダイに相当

- Graphics Tile(グラフィックスタイル):GPUダイに相当

- I/O Tile(入出力タイル):各種入出力インタフェースを搭載

- SoC Tile(SoCタイル):その他高機能部位を統合

タイルアーキテクチャで注目すべきなのは、各タイルのプロセスルール(微細度)は異なっても構わないという点だ。事実、Meteor Lakeの各タイルは、プロセスルールが以下の通り結構バラバラだったりする。

- ベースダイ:22nmプロセス

- Compute Tile:Intel 4(7nmプロセス)

- Graphics Tile:TSMC N5(5nmプロセス)

- I/O Tile:TSMC N6(6nmプロセス)

- SoC Tile:同上

チップレット技術では先行しているAMDも、CPUダイとI/Oダイのプロセスルールは異なっていたので、このアプローチ自体は「できて当たり前」なのかもしれない。しかし複数のプロセスルールが混在しているタイルをベースダイに“直接”接合させる技術は間違いなく高度で、驚かされる。

Compute Tileは、初めての「Intel 4」プロセス採用製品でもある。一見すると第12世代/第13世代Coreプロセッサ(開発コード名:Alder Lake/Raptor Lake)のCPUダイと同じように見える

Compute Tileは、初めての「Intel 4」プロセス採用製品でもある。一見すると第12世代/第13世代Coreプロセッサ(開発コード名:Alder Lake/Raptor Lake)のCPUダイと同じように見えるMeteor Lakeは4タイル構成だが、これらのタイルを別のものに入れ替えたり、あるいはベースタイルをより大規模なものに変更した上で、より多くのタイルを載っけたりすることで、CPUの「上位モデル」「下位モデル」の設計を比較的容易に行えることが、タイルアーキテクチャやFoverosの優位性――Intelはこう主張する。

このスライドの右側のパッケージは、実際にMeteor Lakeで使われるもの。左側は「フォームファクターのコンセプト」ということで、ベースタイルを大きくして、より多くのタイルを載っけた「上位SoC」のイメージとなる

このスライドの右側のパッケージは、実際にMeteor Lakeで使われるもの。左側は「フォームファクターのコンセプト」ということで、ベースタイルを大きくして、より多くのタイルを載っけた「上位SoC」のイメージとなる次は、Meteor Lakeの中でも特に注目したい部位「Compute Tile」と「SoC Tile」について詳しく紹介する。

関連記事

Intelが次世代CPU「Meteor Lake」の概要をチラ見せ 全モデルに「AIエンジン」を搭載

Intelが次世代CPU「Meteor Lake」の概要をチラ見せ 全モデルに「AIエンジン」を搭載

Intelが「Meteor Lake(メテオレイク)」というコード名で開発を進めているCPUの概要情報を公開した。同社初の7nmプロセスCPUは、全モデルにCPUコアとは別体の「AIエンジン」を搭載するという。 Intelが次世代のクライアントPC向けCPU「Alder Lake」を2021年に投入

Intelが次世代のクライアントPC向けCPU「Alder Lake」を2021年に投入

Intelは8月13日(現地時間)、オンラインイベント「Intel Architecture Day 2020」を開催し、次世代のクライアント向け製品「Alder Lake」について発表した。 ついに! ようやく? 「Intel Maxシリーズ」2023年1月から出荷 HBM付き「Xeon Max」と高密度実装GPU「Intel GPU Max」

ついに! ようやく? 「Intel Maxシリーズ」2023年1月から出荷 HBM付き「Xeon Max」と高密度実装GPU「Intel GPU Max」

Intelが、HPC(ハイパフォーマンスコンピューティング)と機械学習ベースのAI(人工知能)用のCPU/GPUの統一ブランドとして「Intel Max」を立ち上げる。その第1弾製品はSappire Rapidsと呼ばれていたCPU「Xeon Maxプロセッサ」と、Ponte Vecchioと呼ばれていた「Intel Data Center GPU Max」である。 イスラエルのIntelハイファラボで見た“ちょっと未来”のPC像

イスラエルのIntelハイファラボで見た“ちょっと未来”のPC像

Intelはイスラエルに一大拠点を構えている。先日、報道関係者向けにその現状を伝えるツアーが開催されたが、今回は「Intel 8088」や「MMX Pentium」などを生み出したハイファにあるIDC(Israel Development Center)において実際に研究/開発された技術のデモンストレーションの様子をお伝えする。 最大6GHz駆動を実現! Intelが第13世代Coreに至る道のりをイスラエルで公開

最大6GHz駆動を実現! Intelが第13世代Coreに至る道のりをイスラエルで公開

Intelが“世界中の”メディアを集めてイスラエルの研究開発拠点「Israel Development Center(IDC)」の見学ツアーを開催した。その基調講演において、IDCが開発してきたCPUの歴史と、間もなく登場がうわさされる第13世代Coreプロセッサ(Raptor Lake)の近況が解説された。

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- 発表時の批判は裏返る? スペック据え置きでも“買い”と言える、極上の普段着スマホ「Pixel 10a」を触ってみた (2026年04月27日)

- サイボウズの社名由来 “坊主”に込められた意味が深すぎる (2016年07月29日)

- キーボード「FILCO」ブランドのダイヤテックが閉業 4月22日付で (2026年04月24日)

- マザーボードは「細部まで白」が今の主流? 高コスパ水冷など見逃せない最新自作PCパーツ事情 (2026年04月27日)

- 大型連休前のアキバは新CPUラッシュ! AMD「Ryzen 9 9950X3D2」とIntel「Core Ultra 5 250K Plus/KF Plus」の気になる在庫状況 (2026年04月25日)

- Windows 11の不満解消へ Microsoftの最優先プロジェクト「Windows K2」とは何か (2026年04月28日)

- 次期「DaVinci Resolve 21」で写真編集が可能に/Google Cloudが第8世代TPUを発表 (2026年04月26日)

- エレコム、士郎正宗デザインマウス「M.A.P.P.」復刻モデルの予約販売を4月6日に開始 (2026年03月25日)

- 15.6型モバイルディスプレイ「ASUS ZenScreen MB169CK-J」が21%オフの1万7172円に (2026年04月27日)

- エレコム、「士郎正宗 復刻マウス」発売日を延期 5月下旬の予定に (2026年04月27日)