乽Meteor Lake乿偼CPU僐傾偑3庬椶!?丂Intel偑師悽戙CPU偺徻嵶傪敪昞乮慜曇乯丗惓幃敪昞偼12寧14擔乮暷崙懢暯梞帪娫乯乮1/3 儁乕僕乯

丂Intel偼9寧19擔乮暷崙懢暯梞壞帪娫乯丄12寧14擔乮摨乯偵惓幃敪昞偝傟傞梊掕偺儌僶僀儖岦偗師悽戙CPU乽Core Ultra僾儘僙僢僒乿乮奐敪僐乕僪柤丗Meteor Lake乯偺傾乕僉僥僋僠儍偺徻嵶傪敪昞偟偨丅

丂杮CPU偼丄摨幮帺恎偑乽偙偙40擭娫偱嵟傕戝偒側傾乕僉僥僋僠儍僔僼僩傪峴偭偨乿偲岞尵偟偰偄傞丅偦傟傎偳偵乬帺怣偨偭傉傝乭側惢昳偺傛偆偩丅

丂偦偺帺恎偺棤晅偗偼丄柉惗岦偗CPU偺惢憿媄弍偵偍偗傞乽弶嵦梡乿偺媄弍偑悢懡偔惙傝崬傑傟偨偙偲偵偁傞丅昅幰偼敪昞偵愭嬱偗偰媄弍愢柧夛偵嶲壛偟偨偑丄偦偺撪梕偼旕忢偵嫽枴怺偔丄偲偰傕乬擹偄乭傕偺偩偭偨丅

丂偦偙偱崱夞丄慜屻曇偺2夞偵暘偗偰Meteor Lake偺摿挜傪夝愢偡傞偙偲偵偟偨丅偙偺婰帠乮慜曇乯偱偼丄撉幰偺奆偝傫偑堦斣娭怱傪婑偣偰偄傞偱偁傠偆Meteor Lake偵傑偮傢傞乽惢憿媄弍乿偲乽CPU僐傾乿傪拞怱偵夝愢偟偰偄偒偨偄丅

Meteor Lake傪壓巟偊偡傞惢憿媄弍乽Foveros乿偲偼丠

丂Meteor Lake偼丄儐乕僓乕偺庤尦偵撏偔惢昳偲側偭偨嵺偵偼乽CPU乿偲偐乽僾儘僙僢僒乿偲屇偽傟偨傝偡傞偙偲偺側傞偩傠偆偑丄惢昳僇僥僑儕乕偲偟偰偼丄CPU傪娷傓暋悢偺婡擻傪摑崌偟偨乽SoC乮System on a Chip乯乿偲屇偽傟傞敿摫懱惢昳偲側傞丅

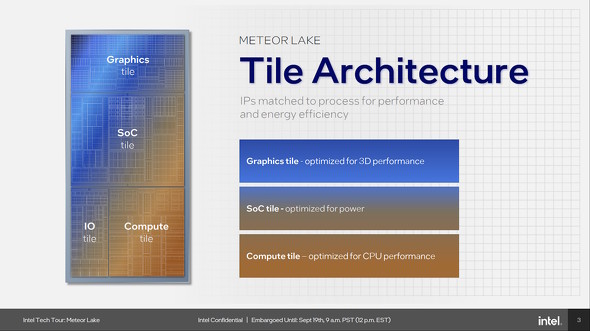

丂偦偺嵟戝偺摿挜偼丄Intel偺SoC偲偟偰偼弶傔偰乽僞僀儖傾乕僉僥僋僠儍乿傪嵦梡偟偨偙偲偵偁傞丅僞僀儖傾乕僉僥僋僠儍偲偼丄SoC乮CPU乯傪扨堦偺僟僀乮儌僲僔儕僢僋僟僀乯偲偟偰宍惉偡傞偺偱偼側偔丄婡擻偛偲偵暘偐傟偨乽婡擻僽儘僢僋乿偲屇偽傟傞僟僀傪暋悢慻傒崌傢偣偰1偮偺乽僷僢働乕僕乿傪嶌傝丄偦傟傪1偮偺SoC偲偟偰宍惉偡傞庤朄偩丅

丂婡擻僽儘僢僋偼丄彫偝側僠僢僾傪堄枴偡傞乽僠僢僾儗僢僩乿偲傕屇偽傟傞丅偦偺偙偲傕偁傝丄僞僀儖傾乕僉僥僋僠儍偼堦斒揑偵乽僠僢僾儗僢僩媄弍乮傾乕僉僥僋僠儍乯乿偲愢柧偝傟傞偙偲偑懡偄丅

婰幰愢柧夛偱巊傢傟偨僗儔僀僪偺1偮丅嵍懁偵偁傞偙傑偛傑偲偟偨傕偺偼Meteor Lake偺僷僢働乕僕偺奣棯恾偱丄戝偒偔暘偗傞偲4偮偺僞僀儖乮僠僢僾儗僢僩乯傪慻傒崌傢偣偰嶌傜傟偰偄傞偙偲偑暘偐傞乮徻偟偔偼屻弎乯

婰幰愢柧夛偱巊傢傟偨僗儔僀僪偺1偮丅嵍懁偵偁傞偙傑偛傑偲偟偨傕偺偼Meteor Lake偺僷僢働乕僕偺奣棯恾偱丄戝偒偔暘偗傞偲4偮偺僞僀儖乮僠僢僾儗僢僩乯傪慻傒崌傢偣偰嶌傜傟偰偄傞偙偲偑暘偐傞乮徻偟偔偼屻弎乯丂僠僢僾儗僢僩媄弍偵傛傞CPU乮SoC乯偺奐敪偼丄嫞崌偺AMD偑乽Zen 2傾乕僉僥僋僠儍乿偱婛偵幚尰偟偰偄傞丅Zen 2傾乕僉僥僋僠儍偲偄偊偽丄2019擭壞偵搊応偟偨僨僗僋僩僢僾岦偗偺乽Ryzen 3000僔儕乕僘乿偑弶弌側偺偱丄Intel偼僠僢僾儗僢僩媄弍傪乽4擭抶傟乿偱嵦梡偟偨偲傕偄偊傞丅

丂偟偐偟丄Meteor Lake偵偍偗傞僞僀儖傾乕僉僥僋僠儍傪嵶偐偔尒偰偄偔偲丄Intel偼AMD偺僠僢僾儗僢僩傛傝傕乬愭恑搙乭偺崅偄偙偲偵庢傝慻傫偱偄傞偙偲偑暘偐傞丅

Meteor Lake偺僞僀儖傾乕僉僥僋僠儍傪壓巟偊偡傞乽Foveros乿偲偄偆媄弍傪夝愢偡傞僥傿儉丒僂傿儖僜儞巵乮僨僓僀儞僄儞僕僯傾儕儞僌僌儖乕僾 僶僀僗僾儗僕僨儞僩寭SoC僨僓僀儞扴摉僛僱儔儖儅僱乕僕儍乯

Meteor Lake偺僞僀儖傾乕僉僥僋僠儍傪壓巟偊偡傞乽Foveros乿偲偄偆媄弍傪夝愢偡傞僥傿儉丒僂傿儖僜儞巵乮僨僓僀儞僄儞僕僯傾儕儞僌僌儖乕僾 僶僀僗僾儗僕僨儞僩寭SoC僨僓僀儞扴摉僛僱儔儖儅僱乕僕儍乯丂彮偟傗傗偙偟偄偺偩偑丄Meteor Lake偵偍偗傞僞僀儖傾乕僉僥僋僠儍偼丄乽Foveros乮僼僅儀儘僗乯乿偲屇偽傟傞僟僀娫愊憌攝慄媄弍偵傛偭偰幚尰偟偰偄傞丅

丂Foveros帺懱偼慡偔怴偟偄媄弍偱偼側偄丅柉惗昳岦偗偲偟偰偼丄2020擭偵搊応偟偨僞僽儗僢僩PC乛2in PC岦偗Core僾儘僙僢僒乮奐敪僐乕僪柤丗Lakefield乯偱弶嵦梡偝傟偰偄傞丅

丂偟偐偟丄偙偺Lakefield偼丄儗僲儃偺弶戙乽ThinkPad X1 Fold乿側偳丄婔偮偐偺僞僽儗僢僩PC偱嵦梡偼偝傟偨傕偺偺丄嵦梡帠椺偼旕忢偵彮側偄丅偦偺偣偄偐丄検嶻奐巒偐傜1擭屻偺2021擭偵偼惗嶻廔椆偑崘抦偝傟偰偟傑偭偨丅Core僾儘僙僢僒僼傽儈儕乕偺拞偱傕丄旕忢偵抁柦側晹椶偵擖傞惢昳偩偭偨偲傕偄偊傞丅

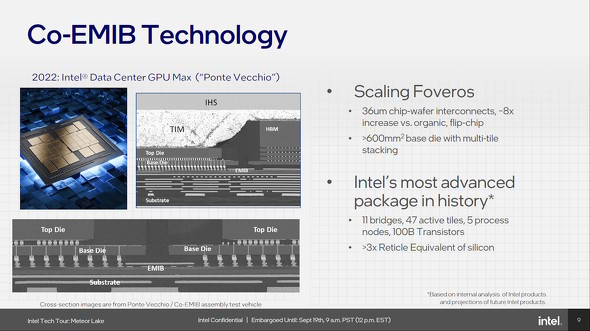

丂堦搙偼徚偊偨偲巚傢傟偨Foveros偩偑丄Intel偼乽Intel Data Center GPU乿乮奐敪僐乕僪柤丗Ponte Vecchio乯偵偍偄偰嵞傃嵦梡偟丄検嶻幚愌傪愊傒廳偹偰偒偨丅

丂Ponte Vecchio偱偺幚愌傪捠偟偰丄Intel偼Meteor Lake偱傕Foveros傪乬巊偊傞乭偲敾抐偟偨偺偩傠偆丅

丂偱偼丄Meteor Lake偺僞僀儖傾乕僉僥僋僠儍偼丄廬棃偺僠僢僾儗僢僩媄弍偲壗偑堘偆偺偩傠偆偐丅

娭楢婰帠

Intel偑師悽戙CPU乽Meteor Lake乿偺奣梫傪僠儔尒偣丂慡儌僨儖偵乽AI僄儞僕儞乿傪搵嵹

Intel偑師悽戙CPU乽Meteor Lake乿偺奣梫傪僠儔尒偣丂慡儌僨儖偵乽AI僄儞僕儞乿傪搵嵹

Intel偑乽Meteor Lake乮儊僥僆儗僀僋乯乿偲偄偆僐乕僪柤偱奐敪傪恑傔偰偄傞CPU偺奣梫忣曬傪岞奐偟偨丅摨幮弶偺7nm僾儘僙僗CPU偼丄慡儌僨儖偵CPU僐傾偲偼暿懱偺乽AI僄儞僕儞乿傪搵嵹偡傞偲偄偆丅 Intel偑師悽戙偺僋儔僀傾儞僩PC岦偗CPU乽Alder Lake乿傪2021擭偵搳擖

Intel偑師悽戙偺僋儔僀傾儞僩PC岦偗CPU乽Alder Lake乿傪2021擭偵搳擖

Intel偼8寧13擔乮尰抧帪娫乯丄僆儞儔僀儞僀儀儞僩乽Intel Architecture Day 2020乿傪奐嵜偟丄師悽戙偺僋儔僀傾儞僩岦偗惢昳乽Alder Lake乿偵偮偄偰敪昞偟偨丅 偮偄偵両丂傛偆傗偔丠丂乽Intel Max僔儕乕僘乿2023擭1寧偐傜弌壸丂HBM晅偒乽Xeon Max乿偲崅枾搙幚憰GPU乽Intel GPU Max乿

偮偄偵両丂傛偆傗偔丠丂乽Intel Max僔儕乕僘乿2023擭1寧偐傜弌壸丂HBM晅偒乽Xeon Max乿偲崅枾搙幚憰GPU乽Intel GPU Max乿

Intel偑丄HPC乮僴僀僷僼僅乕儅儞僗僐儞僺儏乕僥傿儞僌乯偲婡夿妛廗儀乕僗偺AI乮恖岺抦擻乯梡偺CPU乛GPU偺摑堦僽儔儞僪偲偟偰乽Intel Max乿傪棫偪忋偘傞丅偦偺戞1抏惢昳偼Sappire Rapids偲屇偽傟偰偄偨CPU乽Xeon Max僾儘僙僢僒乿偲丄Ponte Vecchio偲屇偽傟偰偄偨乽Intel Data Center GPU Max乿偱偁傞丅 僀僗儔僄儖偺Intel僴僀僼傽儔儃偱尒偨乬偪傚偭偲枹棃乭偺PC憸

僀僗儔僄儖偺Intel僴僀僼傽儔儃偱尒偨乬偪傚偭偲枹棃乭偺PC憸

Intel偼僀僗儔僄儖偵堦戝嫆揰傪峔偊偰偄傞丅愭擔丄曬摴娭學幰岦偗偵偦偺尰忬傪揱偊傞僣傾乕偑奐嵜偝傟偨偑丄崱夞偼乽Intel 8088乿傗乽MMX Pentium乿側偳傪惗傒弌偟偨僴僀僼傽偵偁傞IDC乮Israel Development Center乯偵偍偄偰幚嵺偵尋媶乛奐敪偝傟偨媄弍偺僨儌儞僗僩儗乕僔儑儞偺條巕傪偍揱偊偡傞丅 嵟戝6GHz嬱摦傪幚尰両丂Intel偑戞13悽戙Core偵帄傞摴偺傝傪僀僗儔僄儖偱岞奐

嵟戝6GHz嬱摦傪幚尰両丂Intel偑戞13悽戙Core偵帄傞摴偺傝傪僀僗儔僄儖偱岞奐

Intel偑乬悽奅拞偺乭儊僨傿傾傪廤傔偰僀僗儔僄儖偺尋媶奐敪嫆揰乽Israel Development Center乮IDC乯乿偺尒妛僣傾乕傪奐嵜偟偨丅偦偺婎挷島墘偵偍偄偰丄IDC偑奐敪偟偰偒偨CPU偺楌巎偲丄娫傕側偔搊応偑偆傢偝偝傟傞戞13悽戙Core僾儘僙僢僒乮Raptor Lake乯偺嬤嫷偑夝愢偝傟偨丅

Copyright © ITmedia, Inc. All Rights Reserved.

傾僋僙僗僩僢僾10

- 僉乕儃乕僪乽FILCO乿僽儔儞僪偺僟僀儎僥僢僋偑暵嬈丂4寧22擔晅偱 乮2026擭04寧24擔乯

- 戝宆楢媥慜偺傾僉僶偼怴CPU儔僢僔儏両丂AMD乽Ryzen 9 9950X3D2乿偲Intel乽Core Ultra 5 250K Plus乛KF Plus乿偺婥偵側傞嵼屔忬嫷 乮2026擭04寧25擔乯

- 帩偪塣傃傪嬌傔偨挻寉検僉乕儃乕僪乽儘僕僋乕儖 KEYS TO GO 2乿偑17亾僆僼偺9980墌偵 乮2026擭04寧23擔乯

- AC傾僟僾僞乕晄梫偺奜晅偗HDD乽Seagate One Touch Desktop External Hard Drive乿傪帋偡丂挻戝梕検偱攝慄僗僢僉儕 乮2026擭04寧24擔乯

- Windows 11偺巊偄彑庤偼偳偆曄傢傞丠丂乽Copilot乿柤徧奜偟傗Insider Program嵞曇偵尒傞Microsoft偺杮婥搙 乮2026擭04寧24擔乯

- 嫮椡側僪僢僉儞僌僗僥乕僔儑儞乽Anker PowerExpand Elite 13-in-1 Thunderbolt 3 Dock乿偑28亾僆僼偺2枩6490墌偵 乮2026擭04寧23擔乯

- Microsoft偺乽12僀儞僠Surface Pro乿乽13僀儞僠Surface Laptop乿偑堦晹斕楬偱抣忋偘丂捈斕偱偼4枩6200墌憹偟偵 乮2026擭04寧23擔乯

- 晹壆偺暤埻婥傪堦弖偱曄偊傜傟傞乽SwitchBot RGBIC 僼儘傾儔僀僩乿偑15亾僆僼偺7633墌偵 乮2026擭04寧24擔乯

- Microsoft偺怴擔杮岅IME乽Copilot Keyboard乿偑惓幃斉偵丂乬偍慜傪徚偡曽朄乭偱桳柤側僉儍儔乽僇僀儖乿傕捛壛 乮2026擭04寧23擔乯

- 乽Apple AirPods 4乿偑20亾僆僼偺2枩3798墌偵 乮2026擭04寧24擔乯