「第5世代Xeonスケーラブルプロセッサ」はどう変わったのか? その秘密を技術解説する(3/4 ページ)

第5世代Xeon SPは第4世代からどう変わった?

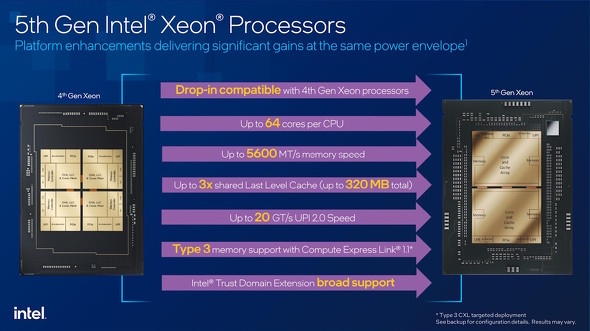

先述の通り、第5世代Xeon SPと先代とのアーキテクチャ面での大きな差分は、XCCパッケージのダイ構成が変わったことと、より低消費電力を求めるニーズに応えるべくEE LCCパッケージが追加されたことの2点となる。ここからは、先代との差分をもう少し細かく見ていこう。

CPUコア:L3キャッシュを大きく増量

第5世代Xeon SPのCPUコアは「Raptor Coveマイクロアーキテクチャ」を採用している。Raptor Coveは、第13世代Coreプロセッサ(開発コード名:Raptor Lake)の高性能コア(Pコア)と同じデザインだ。もっといえば、第12世代Coreプロセッサ(開発コード名:Alder Lake)のPコアで使われている「Golden Coveマイクロアーキテクチャ」の最大稼働クロックを500MHz(0.5GHz)程度引き上げ、CPU命令のプリフェッチを改善した、事実上の「マイナーチェンジ版」ともいえる。

第5世代Xeon SPでは、CPUコア1基あたり2MBのL2キャッシュが搭載されている。これは第4世代Xeon SP向けGolden Coveと同様なので、改良点とはいえない。注目すべきはLLCことL3キャッシュの容量である。モデルにもよるが先代の最大約3倍に増量されている。

最大コア数モデル(≒最上位モデル)同士で比較してみると、第4世代の60コアモデル「Xeon Platinum 8490H」のL3キャッシュは112.5MBだったのに対して、第5世代Xeon SPの64コアモデル「Xeon Platinum 8592+」のL3キャッシュは320MBと、増加率は約2.84倍だ。他のモデルも、同クラスの製品で新旧比較すると、おおむねこの率でL3キャッシュの容量が増えた。

近年、プロセスノードが微細化しても、キャッシュメモリ用のSRAMの微細化は停滞傾向にあるので、「キャッシュの増量に掛かる製造コスト増」と「得られる性能向上率」のバランスは決して芳しくはないはずだ。しかし、「Xeon SPは性能最重要視のサーバ用CPUだから」ということで、こうした設計方針をとったのであろう。

なお、LLCの容量拡大はキャッシュのヒット率向上につながり、ひいてはメインメモリへのアクセスの隠蔽(いんぺい)効率の向上にも結び付く。このことはIPC(クロックあたりの命令実行率)の向上にはつながらないが、低下の抑止(≒IPCの維持)には有効なので、パフォーマンス面で得られる恩恵は大きい。

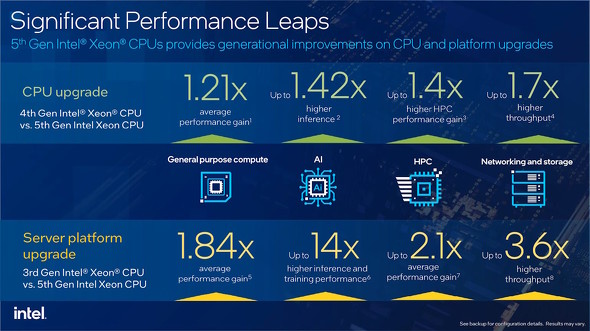

Intelの調べによると、先代の同ランクモデルとの性能比較では、21%以上の性能向上が確認できたという。

第3世/第4世代Xeon SPと比較した場合の性能向上率をまとめたスライド。第3世代からの性能向上が大きいのはもちろんだが、わずか1世代前の第4世代と比べても性能がそこそこ向上していることに注目したい

第3世/第4世代Xeon SPと比較した場合の性能向上率をまとめたスライド。第3世代からの性能向上が大きいのはもちろんだが、わずか1世代前の第4世代と比べても性能がそこそこ向上していることに注目したいメモリ:より高速なモジュールをサポート

この他、第5世代Xeon SPではサポート可能なDDR5メモリのスピードが全体的に向上した。第4世代は最大で4800MHz(DDR5-4800)までのサポートだったが、第5世代では最大で5600MHz(DDR5-5600)までサポートする。

また、マルチプロセッサ(マルチソケット)運用時の実効性能に大きく影響する、プロセッサ間インターコネクト「UPI(Ultra Path Interconnect) 2.0」の伝送速度も先代毎秒16GTから毎秒20GTへと高められた。

ブロックダイヤグラム(構造図)を見る限り、第5世代Xeon SP(XCCパッケージ)のUPIコントローラ数は4基のままで、UPIのリンク数の増加についても言及がなかった。先代のと同じくリンクが24レーン分あると仮定した場合、マルチプロセッサの相互接続帯域は「毎秒20GTs×24÷8=毎秒240GB」になると思われる。

その他:消費電力やセキュリティーを改善

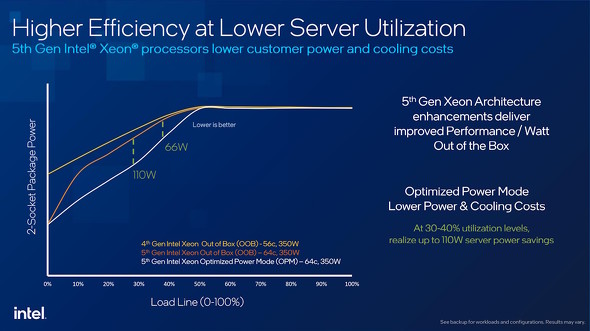

第5世代Xeon SPでは、消費電力(電力効率)についても改良が見られる。

第4世代と比べると、平常動作モードともいえる「性能優先モード」では、CPU負荷率が30〜40%の場合においてわずかだが消費電力が低下する。Intelによると、これを「消費電力優先モード(Optimized Power Mode)」に切り替えると、同じ条件で66〜110W程度のさらなる消費電力低減が見込めるとのことだ。

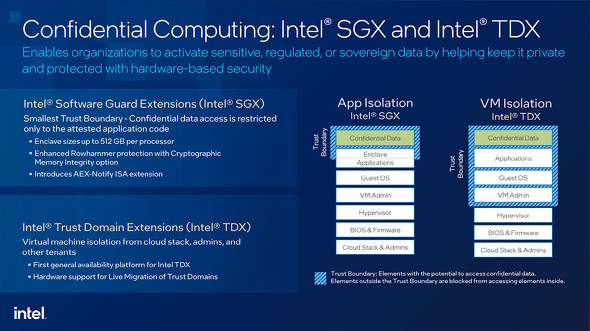

第5世代Xeon SPは、セキュリティ機能も強化された。

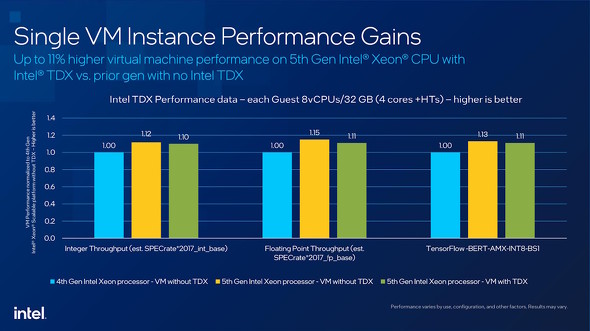

第4世代Xeon SPでは特定モデルのみ対応していた「Intel TDX(Trust Domain Extensions)」を、第5世代では全モデルでサポートする。

第4世代以降のXeon SPでは、アプリごとのメモリ空間の隔離/保護を「Intel SGX(Software Guard Extensions)」が担ってきた。SGXと比べると、TDXを使えば隔離/保護単位を仮想マシン(VM)まで広げられる上、隔離/保護機能を利用した際のパフォーマンスの低下が抑えられるという。

Intel TDXを活用したときと、活用しないときのパフォーマンス比較。TDXを使うとわずかにパフォーマンスが落ち込むものの、比較対象である第4世代Xeon SPのTDX非対応モデルより高いことが分かる

Intel TDXを活用したときと、活用しないときのパフォーマンス比較。TDXを使うとわずかにパフォーマンスが落ち込むものの、比較対象である第4世代Xeon SPのTDX非対応モデルより高いことが分かるCXL 1.1バス:Type 3デバイスの接続も可能に

一般ユーザー向けのPCでは当面の間関係ないだろうが、サーバ/データセンター向けコンピューターシステムでは「CXL(Compute Express Link)」というバス規格に関する話題が増えてきた。

CXLはPCI Express 5.0をベースに、CPUやメモリ、各種周辺機器においてより高速にデータのやりとりができるようにした規格だ。実用ベースでは「CXL 1.1」が普及しているが、現時点ではPCI Express 6.0も想定した「CXL 3.0」の策定作業も進んでいる。

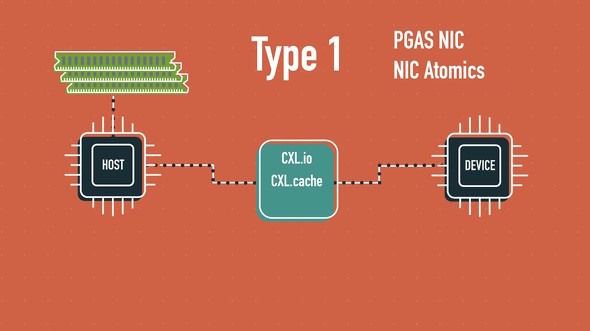

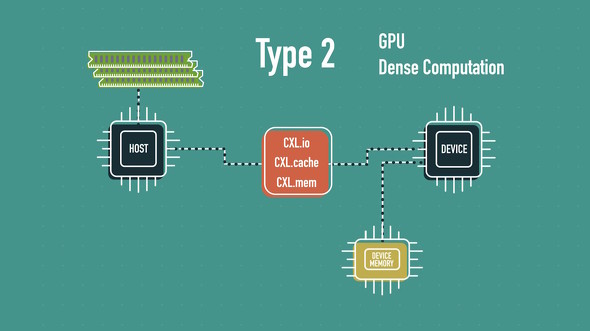

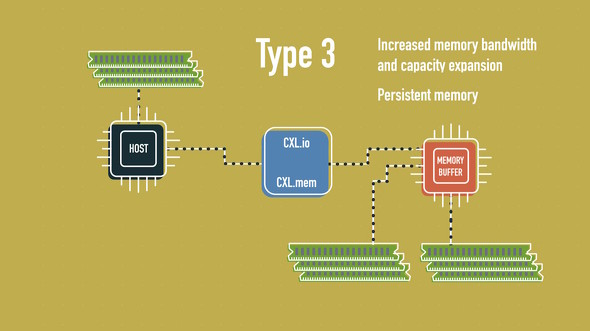

CXL 1.1では、デバイスを大きく「Type 1」「Type 2」「Type 3」の3種類に分けて定義している。

Type 1は「CPU管理下のメモリ空間にアクセスできるが、自身はCPUと共有するメモリ空間を持たないデバイス」だ。CPUとメモリ空間は共有しないものの、キャッシュメモリの内容の一貫性は担保できるようになっている。対応デバイスの具体例としては、サーバに搭載される「スマートネットワークカード」が挙げられる。

Type 2は「CPUとデバイスがそれぞれにメモリ空間を持ち、CPUからもデバイスのメモリ空間にアクセスできるデバイス」だ。Type 1と同様にキャッシュメモリの内容の一貫性は確保されるが、逆方向(デバイスからCPUのメモリ空間)へのアクセスはサポートされない。サーバ向けGPUは、このタイプのデバイスの代表格となる。

そしてType 3は「CPUからのアクセスを許容するメモリ空間だけを備えるデバイス」である。「何のこっちゃ?」と思うかもしれないが、分かりやすくいえば補助記憶デバイスのために用意されたデバイスタイプとも言い換えられる。メインメモリとストレージデバイスの“間”に差し込んで使う「メモリ拡張デバイス(Memory Expansion Device)」が、本タイプの代表的なデバイスだ。このような性質から、Type 3デバイスは「CXLメモリ」と呼ばれることもある。

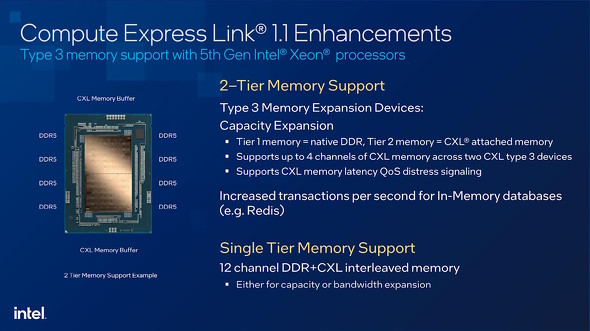

前置きが長くなったが、第5世代Xeon SPはCXL 1.1 Type 1/Type 2デバイスの接続に加えて、CXL 1.1 Type 3デバイス(=CXLメモリ)の接続にも対応した。

第5世代Xeon SPでは、CXLメモリに対して2つの接続モードが用意されている。

【2-Tier Memory Support】

「2-Tier Memory Support」モードでは、CPU直結のDDR5メモリ(最大8チャンネル)を高速な「Tier 1メモリ」、CXL 1.1バス(最大4チャンネル)に接続したCXLメモリを中低速の「Tier 2メモリ」として定義して使える。

リアルタイム性(≒高速なレスポンス)が求められるアプリやデータはTier 1メモリに、そうでもないアプリやデータはTier 2メモリに配置することで、よりメモリをより効率的に利用できる。

【Single Tier Memory Support】

先に説明した2-Tier Memory Supportモードとは異なり、「Single Tier Memory Support」モードではDDR5メモリとCXL 1.1バスに接続したCXLメモリを“対等に”取り扱う。このモードを使うと、CPU視点では「最大12チャンネルのメモリ」が存在するように見える。

性質上、このモードではメモリのアクセススピードが遅い方(≒CXLメモリ)に合わせられる。そのため、「メモリのアクセススピードが命」という用途ではパフォーマンスが低下してしまうが、逆に「メモリの容量こそが重要」という用途ではパフォーマンスが向上する。

どちらのモードが有利となるかは、サーバで動かすアプリやサービスによる。CXLメモリを併用する場合は、稼働環境を精査した上でモードを選ぶとよいだろう。

2023年9月に開催された「Intel Innovation 2023」では、幾つかのストレージメーカーがCXLメモリを発表/展示していた。大容量のデータを取り扱うAIの学習プロセスに有用ということで、AIサーバへの採用が期待されている(左からMicron、SK hynix、キオクシアのCXLメモリ)

2023年9月に開催された「Intel Innovation 2023」では、幾つかのストレージメーカーがCXLメモリを発表/展示していた。大容量のデータを取り扱うAIの学習プロセスに有用ということで、AIサーバへの採用が期待されている(左からMicron、SK hynix、キオクシアのCXLメモリ)第5世代Xeon SPでは、AI(人工知能)処理やHPC(ハイパフォーマンスコンピューティング)における演算処理を高速化するための工夫も盛り込まれている。

関連記事

「第5世代Xeonスケーラブルプロセッサ」正式発表 第4世代と同一プラットフォームでパフォーマンスを大きく向上

「第5世代Xeonスケーラブルプロセッサ」正式発表 第4世代と同一プラットフォームでパフォーマンスを大きく向上

Intelが、サーバ/データセンター向けCPUの新世代をリリースする。従来世代と同じフォームファクターながら、複数の改良によって性能を大きく改善している。【更新】 Intelが「第5世代Xeonスケーラブルプロセッサ(Emerald Rapids)」を12月14日に発表 先の新製品のスケジュールも順調

Intelが「第5世代Xeonスケーラブルプロセッサ(Emerald Rapids)」を12月14日に発表 先の新製品のスケジュールも順調

Intelが2023年後半に発売するしていた「第5世代Xeonスケーラブルプロセッサ」を12月14日(米国太平洋時間)に正式発表することを明らかにした。現行の第4世代製品を改良してより処理効率を高めたもので、CPUソケットの互換性もある。 Intelが「第4世代Xeonスケーラブルプロセッサ」を正式発表 後から機能を拡張できる「Intel On Demand」対応モデルも

Intelが「第4世代Xeonスケーラブルプロセッサ」を正式発表 後から機能を拡張できる「Intel On Demand」対応モデルも

Intelが、データセンター(サーバ)/HPC向けCPU「Xeonスケーラブルプロセッサ」の第4世代製品を正式に発表した。先行リリースされたHBM2付きの「Xeon CPU Max」と合わせて、一部モデルを除き後から機能を追加できる「Intel On Demand」にも対応する。 インテル、日本で「Core Ultraプロセッサ」を正式発表 AI処理を高速化

インテル、日本で「Core Ultraプロセッサ」を正式発表 AI処理を高速化

インテルが新しいモバイル向けCPU 「Core Ultraプロセッサ」(開発コード名:Meteor Lake)を日本で正式に発表した。 第5世代は2023年第4四半期、Eコアオンリーの「Sierra Forest」は2024年上期に出荷――Intelが「Xeonスケーラブル」の最新状況を報告

第5世代は2023年第4四半期、Eコアオンリーの「Sierra Forest」は2024年上期に出荷――Intelが「Xeonスケーラブル」の最新状況を報告

Intelが投資家向けのセミナーにおいて、データセンター向けCPU(Xeonスケーラブルプロセッサ)の最新ロードマップを公開した。Emerald Rapidsは「第5世代Xeonスケーラブルプロセッサ」として2023年第4四半期に一般出荷が始まる予定で、新たに加わるEコアのみの「Sierra Forest」も2024年上期には一般出荷できる見通しだという。

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- 3COINSの“1100円ポーチ”が優秀 自立型と保護型、収納力や使い勝手を比較してみた (2026年04月13日)

- 驚きの静音性とロングバッテリー! 14型有機EL搭載のCopilot+ PC「Zenbook 14 UM3406GA」レビュー (2026年04月14日)

- レノボ、学習利用にも適したSnapdragon 8s Gen4搭載13型Androidタブレット (2026年04月14日)

- 2画面を縦に並べて省スペースで使える「InnoView デュアルモバイルディスプレイ」が34%オフの2万8212円に (2026年04月14日)

- M4 Mac mini本体に装着できる「UGREENのドッキングステーション」が31%オフの9599円に (2026年04月14日)

- Tensor G4搭載の廉価版は”買い”か? 「Pixel 10a」の実機に触れて分かった、価格(7万9900円〜)以上の魅力 (2026年04月13日)

- 「コンセント足りない」後悔を防げる? パナソニックが自動算出ツールを公開 (2026年04月14日)

- サンワ、USB Type-C接続に対応した14型WUXGAモバイル液晶ディスプレイ (2026年04月13日)

- その名はnull4(テトラヌル)――大阪・関西万博の「null2」の次世代パビリオンが2027年の横浜園芸博に“転生” 落合陽一氏が語る狙いとは? (2026年04月14日)

- エプソン、PCレスでのスキャンに対応したネットワーク対応A3ドキュメントスキャナー3製品 (2026年04月13日)