「第5世代Xeonスケーラブルプロセッサ」正式発表 第4世代と同一プラットフォームでパフォーマンスを大きく向上

Intelは12月14日、サーバ/データセンター向けCPU「第5世代Xeonスケーラブルプロセッサ」(開発コード名:Emerald Rapids)を正式に発表した。搭載製品は、パートナー企業を通して2024年第1四半期(2024年1〜3月)から順次発売される予定だ。

【更新:11時50分】一部、差し込むべき画像が誤っていたため差し替えました

第5世代Xeonスケーラブルプロセッサの概要

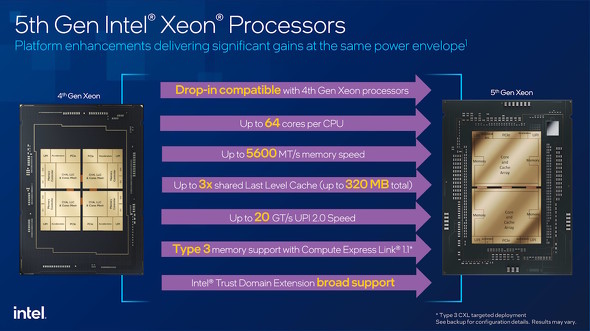

第5世代Xeonスケーラブルプロセッサは、現行の第4世代Xeonスケーラブルプロセッサ(開発コード名:Sapphire Rapids)の改良版という位置付けで、CPUソケットにも互換性があるため「マザーボードを流用してアップグレード可能」だ(UEFIの更新が必要な場合がある)。

主な改良ポイントは以下の通りだ。

- CPUコアの増量(最大60基→64基)

- メインメモリへのアクセス速度の向上(DDR5-4000〜4800→DDR5-4400〜5600)

- L3キャッシュの増量(先代比で最大3倍に)

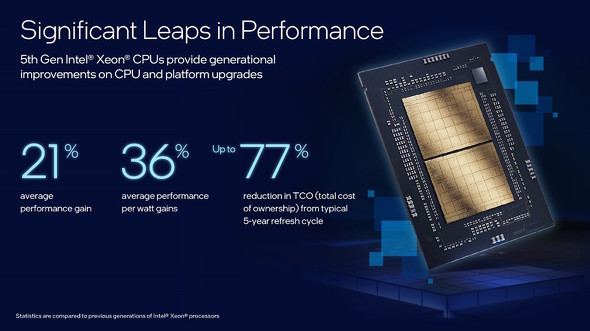

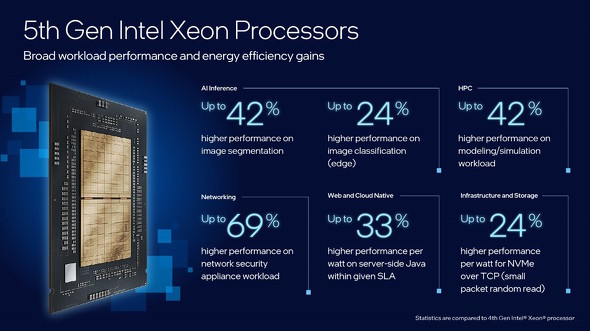

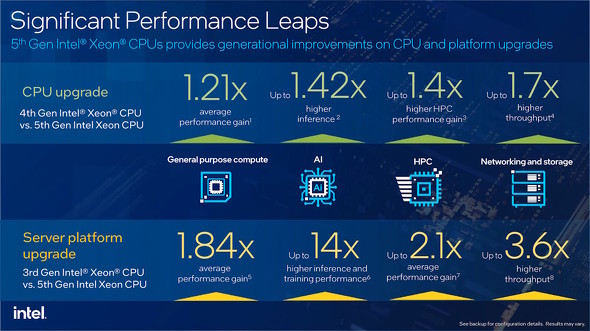

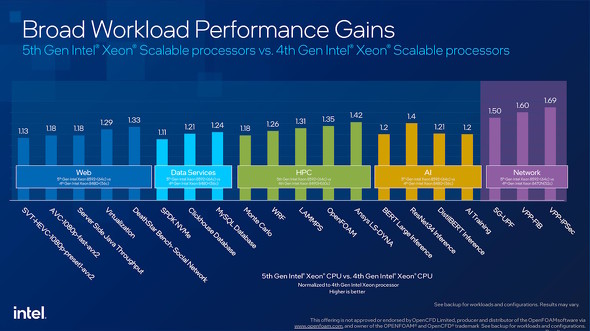

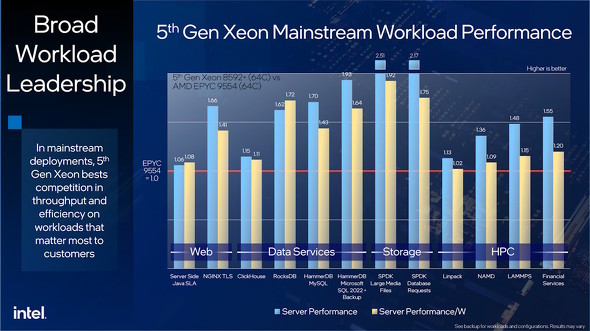

Intelによると、先代の同等プロセッサと比べると平均21%の性能向上を果たし、消費電力当たりの性能(いわゆる「ワッパ」)が平均36%向上したという。また、5年間隔でのシステム更新を考慮に入れると、最大77%のTCO(総所有コスト)の削減も期待できるとのことだ。

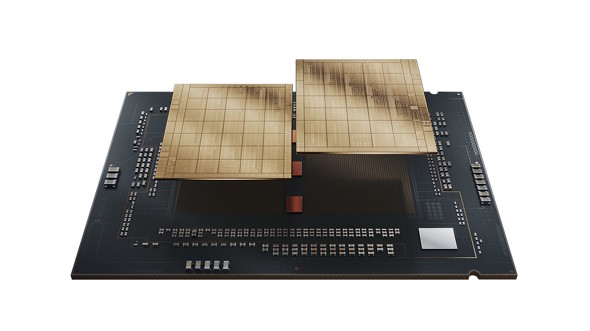

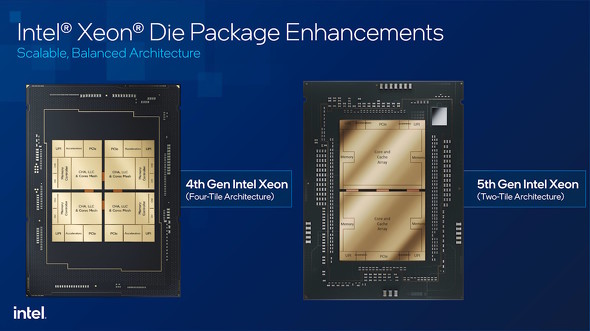

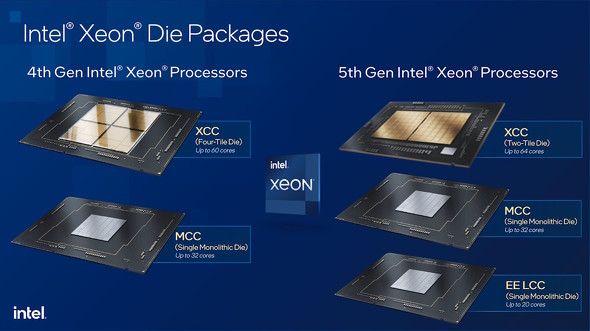

先代と同様に、第5世代もCPU「タイル構造」によってスケーラビリティー(必要な能力に応じた拡張性)を確保している。ただし、性能とのバランスを重視する観点からタイルの基数が最大4から最大2に“削減”されている。

第4世代ではタイルが最大4基構成だったが、第5世代ではスケーラビリティーと性能とのバランスを取る観点から最大2基構成となっている。なお、シングルタイル(モノシリックダイ)構成には、メインストリームのMCC(Medium Core Count)パッケージ加えて、コア数の少ないモデル向けに「LCC(Low Core Count)パッケージ」も復活している

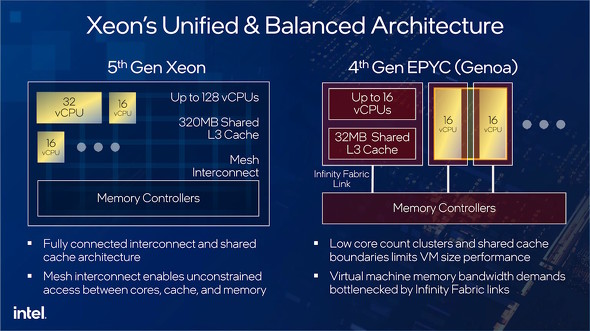

第4世代ではタイルが最大4基構成だったが、第5世代ではスケーラビリティーと性能とのバランスを取る観点から最大2基構成となっている。なお、シングルタイル(モノシリックダイ)構成には、メインストリームのMCC(Medium Core Count)パッケージ加えて、コア数の少ないモデル向けに「LCC(Low Core Count)パッケージ」も復活している競合となるAMDのスケーラブルCPU「第4世代EPYC」(特にGenoa)と比べた場合、アーキテクチャの違いから、特にCPUコアを分割して「vCPU(仮想CPU)」として運用する際の効率とパフォーマンスに大きな違いが出るという。

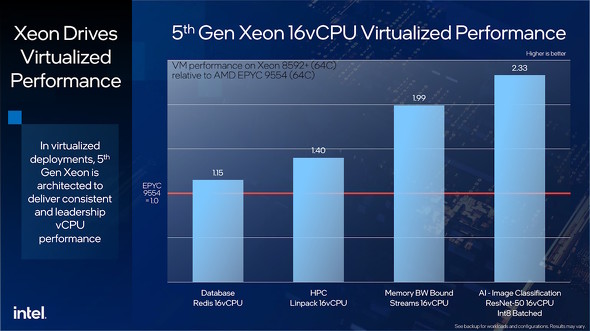

具体的には、第4世代EPYCではvCPUの最大コア数がCCX(Core Complex)の物理コア数に依存するのに対して、第5世代Xeonでは「vCPUの最大コア数=物理コア数」となるので、ワークロードに応じてvCPUのコア数を柔軟に変えられる。全コアが大容量のL3キャッシュを共有できることもメリットだという。

EPYC 9554とXeon 8592+(いずれも64コア128スレッド)で同じ16コアのvCPUを備える仮想マシン(VM)を構築し、4つのワークロードを実行した際のパフォーマンスを比較。いずれもEPYC 9554を上回ったという

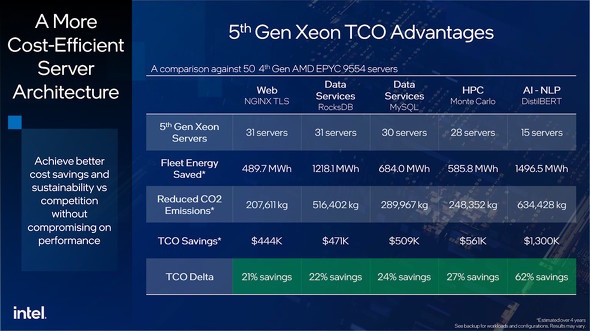

EPYC 9554とXeon 8592+(いずれも64コア128スレッド)で同じ16コアのvCPUを備える仮想マシン(VM)を構築し、4つのワークロードを実行した際のパフォーマンスを比較。いずれもEPYC 9554を上回ったという EPYC 9554を搭載するサーバを50台するのと“同等”のパフォーマンスを発揮するために必要な、Xeon 8592+を搭載するサーバの台数や消費電力の比較。TCO面でも第5世代Xeonの方が有利だというアピールである

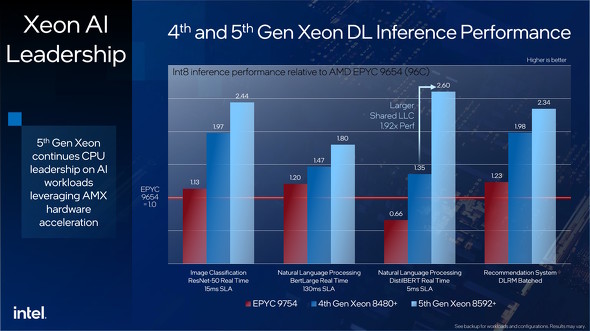

EPYC 9554を搭載するサーバを50台するのと“同等”のパフォーマンスを発揮するために必要な、Xeon 8592+を搭載するサーバの台数や消費電力の比較。TCO面でも第5世代Xeonの方が有利だというアピールである こちらは、DL(深層学習)のパフォーマンスをEPYC 9654(96コア192スレッド)、EPYC 9754(128コア256スレッド)、Xeon 8480+(56コア112スレッド)、Xeon 8592+(64コア128スレッド)で比較している。EPYC勢がCPUコアが多い割にパフォーマンス面で奮わないのは、アーキテクチャの違いが大きく影響しているものと思われる。一方、Xeon同士の比較では、L3キャッシュを増量した第5世代(Xeon 8592+)のパフォーマンスアップが目立つ

こちらは、DL(深層学習)のパフォーマンスをEPYC 9654(96コア192スレッド)、EPYC 9754(128コア256スレッド)、Xeon 8480+(56コア112スレッド)、Xeon 8592+(64コア128スレッド)で比較している。EPYC勢がCPUコアが多い割にパフォーマンス面で奮わないのは、アーキテクチャの違いが大きく影響しているものと思われる。一方、Xeon同士の比較では、L3キャッシュを増量した第5世代(Xeon 8592+)のパフォーマンスアップが目立つラインアップ

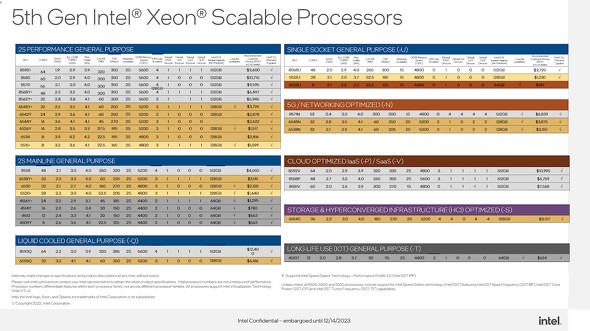

第5世代Xeonスケーラブルプロセッサのラインアップは以下の通りとなる。なお、特記がない限り、全モデルがデュアルCPU構成にも対応する。

- 汎用(はんよう)

- パフォーマンス重視:11種類

- メインストリーム:8種類

- 液冷対応:2種類

- シングルCPU専用(デュアルCPU非対応):3種類

- 携帯電話基地局/ネットワーク機器向け:3種類(1モデルはシングルCPU専用)

- クラウドサービス(IaaS/SaaS)最適化:3種類(1モデルはシングルCPU専用)

- ストレージ/HCI向けモデル:1種類

- 長寿命(IoT向け):1種類

関連記事

Intelが「第5世代Xeonスケーラブルプロセッサ(Emerald Rapids)」を12月14日に発表 先の新製品のスケジュールも順調

Intelが「第5世代Xeonスケーラブルプロセッサ(Emerald Rapids)」を12月14日に発表 先の新製品のスケジュールも順調

Intelが2023年後半に発売するしていた「第5世代Xeonスケーラブルプロセッサ」を12月14日(米国太平洋時間)に正式発表することを明らかにした。現行の第4世代製品を改良してより処理効率を高めたもので、CPUソケットの互換性もある。 全ユーザーにAI PCを届ける――IntelのゲルシンガーCEOの新たな野望 今後10年で15倍に成長する「シリコノミー」とは?

全ユーザーにAI PCを届ける――IntelのゲルシンガーCEOの新たな野望 今後10年で15倍に成長する「シリコノミー」とは?

Intelの開発者/技術者向けイベント「Intel Innovation」が、米国で開催された。その基調講演では、パット・ゲルシンガーCEOが登壇し、今後のIntelが目指す姿を語った。中でも注目すべきキーワードは「Siliconomy(シリコノミー)」である。 Intelが「第4世代Xeonスケーラブルプロセッサ」を正式発表 後から機能を拡張できる「Intel On Demand」対応モデルも

Intelが「第4世代Xeonスケーラブルプロセッサ」を正式発表 後から機能を拡張できる「Intel On Demand」対応モデルも

Intelが、データセンター(サーバ)/HPC向けCPU「Xeonスケーラブルプロセッサ」の第4世代製品を正式に発表した。先行リリースされたHBM2付きの「Xeon CPU Max」と合わせて、一部モデルを除き後から機能を追加できる「Intel On Demand」にも対応する。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- キーボード「FILCO」ブランドのダイヤテックが閉業 4月22日付で (2026年04月24日)

- 次期「DaVinci Resolve 21」で写真編集が可能に/Google Cloudが第8世代TPUを発表 (2026年04月26日)

- 大型連休前のアキバは新CPUラッシュ! AMD「Ryzen 9 9950X3D2」とIntel「Core Ultra 5 250K Plus/KF Plus」の気になる在庫状況 (2026年04月25日)

- 持ち運びを極めた超軽量キーボード「ロジクール KEYS TO GO 2」が17%オフの9980円に (2026年04月23日)

- ACアダプター不要の外付けHDD「Seagate One Touch Desktop External Hard Drive」を試す 超大容量で配線スッキリ (2026年04月24日)

- Windows 11の使い勝手はどう変わる? 「Copilot」名称外しやInsider Program再編に見るMicrosoftの本気度 (2026年04月24日)

- 「Apple AirPods 4」が20%オフの2万3798円に (2026年04月24日)

- 2026年版Surfaceはどうなる? 正面衝突を避けるMicrosoft、10万円切り「MacBook Neo」対抗への秘策はあるか (2026年04月21日)

- 部屋の雰囲気を一瞬で変えられる「SwitchBot RGBIC フロアライト」が15%オフの7633円に (2026年04月24日)

- 強力なドッキングステーション「Anker PowerExpand Elite 13-in-1 Thunderbolt 3 Dock」が28%オフの2万6490円に (2026年04月23日)