「第5世代Xeonスケーラブルプロセッサ」はどう変わったのか? その秘密を技術解説する(1/4 ページ)

既報の通り、Intelは12月14日に「第5世代Xeon スケーラブルプロセッサ」(開発コード名:Emerald Rapids)を発表した。搭載製品は2024年1〜3月から順次発売される予定だ。

本稿では、本製品のアーキテクチャ面における注目ポイントや、先代からの強化点などを解説する。なお、本稿は2023年11月末に行われた「Intel Data Center Workshop 2023」の内容を元にしている。

そもそも「第5世代Xeonスケーラブルプロセッサ」ってどういうもの?

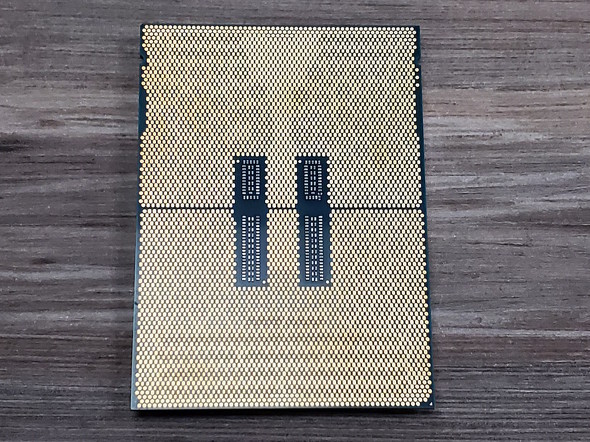

第5世代Xeonスケーラブルプロセッサ(以下「第5世代Xeon SP」)は、Intel 7(10nm相当)プロセスで生産されたサーバ/データセンター向けCPUだ。先代の「第4世代Xeonスケーラブルプロセッサ」(開発コード名:Sapphire Rapids)と同じ製造プロセスで、CPUソケットも同じ「FCLGA4677」なので、第5世代Xeon SPは「第4世代のマイナーチェンジモデル」ともいえる。

しかし、その中身を子細に見ていくと、大幅な物理設計改変が行われている。ある意味で“ビッグマイナーチェンジ”ともいえるため、見どころは多い。

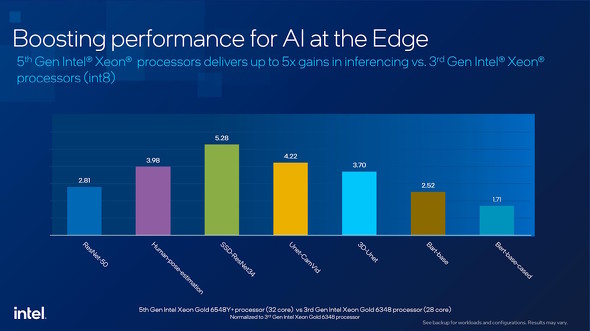

その概要説明では、先代からの移行はもちろん、第3世代製品(開発コード名:Ice Lake)からのプラットフォーム刷新を促す製品としてのアピールが強く感じられた。

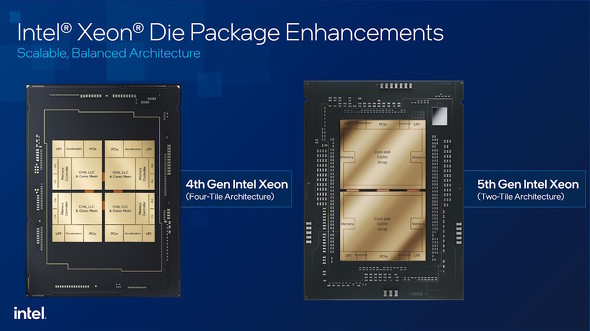

第4世代Xeon SPでは、最大4基のダイ(チップ)で最大60コア構成となる「XCC(Extreme Core Count)」と、1基のダイで最大32コア構成となる「MCC(Medium Core Count)」の2種類のパッケージが用意されていた。しかし、第5世代Xeon SPでは大きく変わっている。

まず上位モデル向けのXCCパッケージは、最大2ダイ/64コア構成に変更された。MCCはシングルダイ/最大32コア構成のミドルレンジモデル向けに継続される一方で、エントリークラスの製品向けにシングルダイ/最大20コア構成の「EE LCC(Energy Efficient Low Core Count)」という新たなパッケージが追加されている。

第4世代は最大4ダイ/60コア構成の「XCC」と、1コア/最大32コア構成の「MCC」の2パッケージが容易されていた。それに対して、第5世代ではXCCの構成が「最大2ダイ/64コア」に変更され、1ダイ/最大20個亜構成の「EE LCC」というパッケージが追加されている

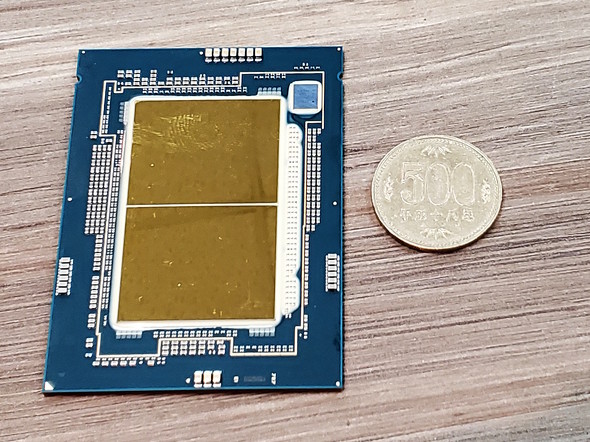

第4世代は最大4ダイ/60コア構成の「XCC」と、1コア/最大32コア構成の「MCC」の2パッケージが容易されていた。それに対して、第5世代ではXCCの構成が「最大2ダイ/64コア」に変更され、1ダイ/最大20個亜構成の「EE LCC」というパッケージが追加されている第4世代では最大60コア構成だったものが、第5世代では最大64コアになった――ボーッとしていると「あ、4コア増えたのね」という感想しか出てこないが、実は「4ダイで60コア(1ダイ当たり20コア)」から「2ダイで64コア(1ダイ当たり32コア)」と、結構大きな構造変更が行われている。この変更には、それなりの理由がある。

詳しくは後に示す図を見てほしいのだが、第4世代では4基のダイをリングバス的な内部バスで接続していたのに対して、第5世代では2基のダイの間を幅の広い内部バス(≒多チャンネル)で直結する構造になっている。これにより、反対側のダイが管轄するメモリ空間へのアクセス効率が劇的に改善した。

こういった共有メモリ型のマルチCPU構成における、CPUコア視点におけるメモリへのアクセスメカニズムを「NUMA(Non-uniform Memory Access:不均一なメモリアクセスの仕組み)」という。第5世代Xeon SPの上位モデルは、XCCの構成を変更することでNUMA性能の向上を実現したのだ。

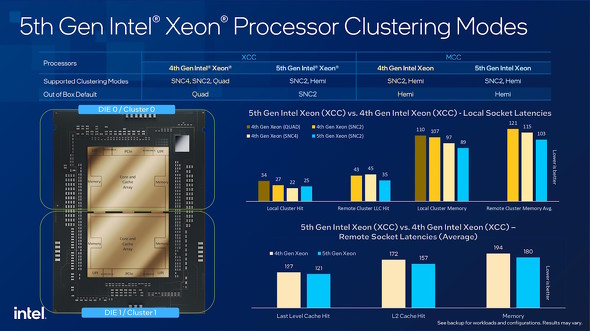

第4世代Xeon SP(XCCパッケージ)では、4基のダイからのNUMAをそれぞれ個別のノードとして司る「SNC4(Sub-NUMA Clustering 4)」や、2基を1ユニットとして2ノードとしてつかさどる「SNC2」、そしてノードを区別しない「Quad(Quadrant)」がサポートされていた。それに対して、2ダイ構成となった第5世代Xeon SP(XCCパッケージ)では、SNC2と「Hemi(Hemisphere)」がサポートされる。

「Hemiって何?」という人もいると思うので解説すると、Hemiは互いのダイのNUMAノードを半分ずつ共有管理する方式だ。SNC2でもHemiでも、メモリアクセス時の伝送経路に大差はないが、LLC(ラストレベルキャッシュ:第5世代Xeon SPの場合はL3キャッシュ)のカバー範囲が大きく変わる。どちらのモードが良いかはサーバの使い方によって変わるため、一概に優劣は付けられない。

なお第5世代Xeon SPは、先述の通りダイ間インターコネクト用の内部バス性能が増強された他、L3キャッシュも増量された。両者の相乗効果により、LLCのミス時とヒット時の両方でメモリアクセスの遅延が低減されている。

次ページでは、第5世代Xeon SPのラインアップについて見ていこう。

関連記事

「第5世代Xeonスケーラブルプロセッサ」正式発表 第4世代と同一プラットフォームでパフォーマンスを大きく向上

「第5世代Xeonスケーラブルプロセッサ」正式発表 第4世代と同一プラットフォームでパフォーマンスを大きく向上

Intelが、サーバ/データセンター向けCPUの新世代をリリースする。従来世代と同じフォームファクターながら、複数の改良によって性能を大きく改善している。【更新】 Intelが「第5世代Xeonスケーラブルプロセッサ(Emerald Rapids)」を12月14日に発表 先の新製品のスケジュールも順調

Intelが「第5世代Xeonスケーラブルプロセッサ(Emerald Rapids)」を12月14日に発表 先の新製品のスケジュールも順調

Intelが2023年後半に発売するしていた「第5世代Xeonスケーラブルプロセッサ」を12月14日(米国太平洋時間)に正式発表することを明らかにした。現行の第4世代製品を改良してより処理効率を高めたもので、CPUソケットの互換性もある。 Intelが「第4世代Xeonスケーラブルプロセッサ」を正式発表 後から機能を拡張できる「Intel On Demand」対応モデルも

Intelが「第4世代Xeonスケーラブルプロセッサ」を正式発表 後から機能を拡張できる「Intel On Demand」対応モデルも

Intelが、データセンター(サーバ)/HPC向けCPU「Xeonスケーラブルプロセッサ」の第4世代製品を正式に発表した。先行リリースされたHBM2付きの「Xeon CPU Max」と合わせて、一部モデルを除き後から機能を追加できる「Intel On Demand」にも対応する。 インテル、日本で「Core Ultraプロセッサ」を正式発表 AI処理を高速化

インテル、日本で「Core Ultraプロセッサ」を正式発表 AI処理を高速化

インテルが新しいモバイル向けCPU 「Core Ultraプロセッサ」(開発コード名:Meteor Lake)を日本で正式に発表した。 第5世代は2023年第4四半期、Eコアオンリーの「Sierra Forest」は2024年上期に出荷――Intelが「Xeonスケーラブル」の最新状況を報告

第5世代は2023年第4四半期、Eコアオンリーの「Sierra Forest」は2024年上期に出荷――Intelが「Xeonスケーラブル」の最新状況を報告

Intelが投資家向けのセミナーにおいて、データセンター向けCPU(Xeonスケーラブルプロセッサ)の最新ロードマップを公開した。Emerald Rapidsは「第5世代Xeonスケーラブルプロセッサ」として2023年第4四半期に一般出荷が始まる予定で、新たに加わるEコアのみの「Sierra Forest」も2024年上期には一般出荷できる見通しだという。

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- キーボード「FILCO」ブランドのダイヤテックが閉業 4月22日付で (2026年04月24日)

- 大型連休前のアキバは新CPUラッシュ! AMD「Ryzen 9 9950X3D2」とIntel「Core Ultra 5 250K Plus/KF Plus」の気になる在庫状況 (2026年04月25日)

- 持ち運びを極めた超軽量キーボード「ロジクール KEYS TO GO 2」が17%オフの9980円に (2026年04月23日)

- ACアダプター不要の外付けHDD「Seagate One Touch Desktop External Hard Drive」を試す 超大容量で配線スッキリ (2026年04月24日)

- Windows 11の使い勝手はどう変わる? 「Copilot」名称外しやInsider Program再編に見るMicrosoftの本気度 (2026年04月24日)

- 強力なドッキングステーション「Anker PowerExpand Elite 13-in-1 Thunderbolt 3 Dock」が28%オフの2万6490円に (2026年04月23日)

- Microsoftの「12インチSurface Pro」「13インチSurface Laptop」が一部販路で値上げ 直販では4万6200円増しに (2026年04月23日)

- 部屋の雰囲気を一瞬で変えられる「SwitchBot RGBIC フロアライト」が15%オフの7633円に (2026年04月24日)

- Microsoftの新日本語IME「Copilot Keyboard」が正式版に “お前を消す方法”で有名なキャラ「カイル」も追加 (2026年04月23日)

- AIによる生産性向上と創造性の発揮は一致しない──異例のキャリアを築く“いとうまい子”が語る、AI時代に人間が最後まで鍛えるべき“唯一の能力”とは? (2026年04月24日)