プロセスノードに加えて新技術も売り込む! Intelが半導体の「受託生産」で使う“武器”【後編】(4/5 ページ)

オングストローム世代のプロセスで使われる新技術

このオングストローム世代のIntelプロセスでは、「2つの新技術」が採用されることがアピールされている。

RibbonFET(GAAFET/GAAトランジスタ)

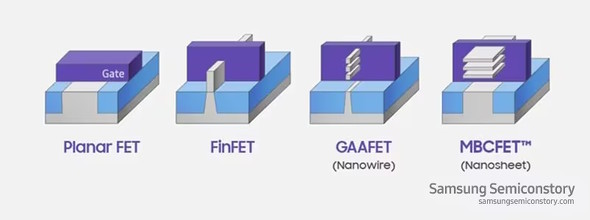

1つは「GAAFET(Gate All Around Fin field Effect Transistor)(GAAトランジスタ)」だ。Intelではこれを「RibbonFET」と呼んでいる。

トランジスタは、ゲートへの電力制御において、ソースとドレインの間(≒チャネル)の通電を制御する素子だ。この手の話では、チャネルは「水流」、ゲートは「水門」に例えられるが、基本的にトランジスタはゲート〜チャネル間の接触面積が大きい方がリーク(漏えい)電流を少なく抑えられるため、性能と電力効率の面で優秀とされる。

しかし、プロセスの微細化を進めていくに従って接触面積がどんどん少なくなっている。この流れの中で「どうやって接触面積を稼ぐのか?」という新たな技術的課題が発生し、それに対する技術開発が行われた。

その結果、「三次元(3D)トランジスタ」の異名で知られる「FinFET」が誕生した。その新世代版として開発されたのが「GAAFET」である。

Intel 20A/18Aでは、このGAAFET(RibbonFET)が利用できるようになる。

サムスン半導体(Samsung Semiconductor)が公開しているFETの系譜図。図内の「Planar FET」は普通のトランジスタ(二次元トランジスタ)で、FinFETは3Dトランジスタとも呼ばれる。GAAFETは改良型FinFETで、IntelではRibbonFETと呼ばれる。MBCFETはサムスン電子が独自に改良したGAAFETで、GAAFETにおける“ひげ”のような部分を“きしめん”のように広げることで設置面積を広げている

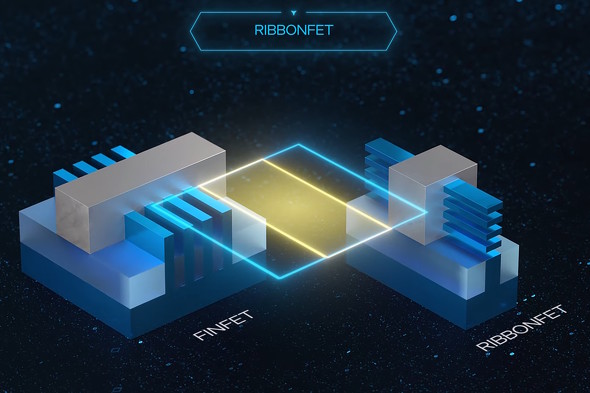

サムスン半導体(Samsung Semiconductor)が公開しているFETの系譜図。図内の「Planar FET」は普通のトランジスタ(二次元トランジスタ)で、FinFETは3Dトランジスタとも呼ばれる。GAAFETは改良型FinFETで、IntelではRibbonFETと呼ばれる。MBCFETはサムスン電子が独自に改良したGAAFETで、GAAFETにおける“ひげ”のような部分を“きしめん”のように広げることで設置面積を広げているFinFETと比較した際のRibbonFETのメリットは、前述したように一段進んだ低電力で駆動できることにある。構造的に素子自体の占有面積も相対的に小さくできるので、同じサイズのチップで同じプロセスノードであれば、FinFETよりもたくさんのロジックを詰め込めることもメリットだ。

左が「3Dトランジスタ」と呼ばれてきたFinFET、右がGAAFETとも呼ばれるRibbonFETの模式図。中央の平たい図版は、青い枠がFinFETの占有面積で、黄色い枠がRibbonFETの占有面積を示している。占有面積を半分以下にできるため、集積度をさらに向上できることになる

左が「3Dトランジスタ」と呼ばれてきたFinFET、右がGAAFETとも呼ばれるRibbonFETの模式図。中央の平たい図版は、青い枠がFinFETの占有面積で、黄色い枠がRibbonFETの占有面積を示している。占有面積を半分以下にできるため、集積度をさらに向上できることになるPowerVia

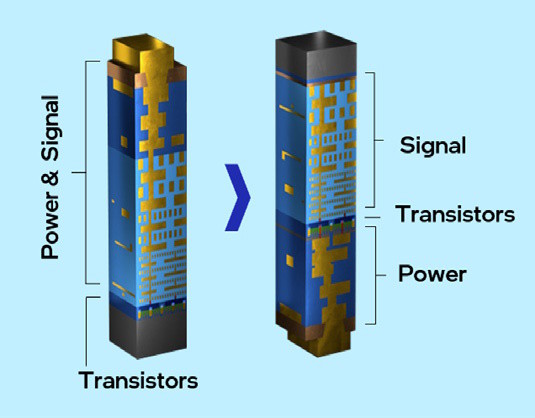

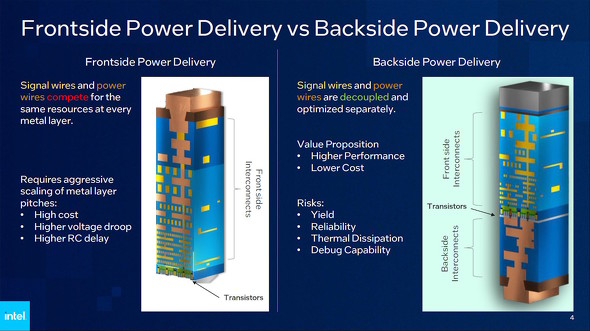

2つ目は「PowerVia」という、Intel独自の新しいトランジスタの構造技術だ。

従来のCPU(トランジスタ)の構造と比べると、PowerViaでは給電回路と信号回路をほぼ完全に分離してプロセッサを形成できる。そのため、対ノイズ性能が高まり、低電力化が実現しやすくなる上に、動作クロックも上げやすい。

加えて、太い給電回路と細い信号回路を分離できることから、信号回路の複雑化や搭載トランジスタの増量にも貢献する。

もう少し詳しく説明しよう。

上図の左側にある従来設計のCPUでは、微細トランジスタ群を積層するに当たり、電源配線をダイ(チップ)の表面(上層)から裏面(下層)に向かうように重ねている。

実際の製造工程では最下層の方から上に向かって積層していくのだが、この工法では電源の配線と信号線とが隣接/混在することになる。電磁気学的な観点からすれば、超高速な信号のやりとりを行う高性能CPUでは、信号線と電源配線が隣接/混在するのは極力避けることが望ましい。

余談だが、従来工法のCPUは、製品化の段階で上下(裏表)を逆転してパッケージ基板に実装する、いわゆる「フリップチップ実装」が行われる。

従来構造のCPUでは、微細化や高速化が進むほどに信号線と電源配線の隣接/混在がボトルネックになってしまう。ゆえに、信号線と電源配線を“分離”する手法が模索されてきた。図中の茶色の配線は給電回路を、そして黄色の配線はトランジスタや信号回路を表している

従来構造のCPUでは、微細化や高速化が進むほどに信号線と電源配線の隣接/混在がボトルネックになってしまう。ゆえに、信号線と電源配線を“分離”する手法が模索されてきた。図中の茶色の配線は給電回路を、そして黄色の配線はトランジスタや信号回路を表している対して、PowerViaは最初の積層時にトランジスタ層と信号配線層だけを積層し、そこでいったん作業を終了し、ウエハごとひっくり返して、今度は電源配線を積層していくという“二段構え”で製造される。結果、電源配線と信号配線はほぼ分離できる。

これによりCPUは高クロック化しやすくなる上、電気抵抗が減ることで消費電力も抑えられる……のだが、聞くからに製造工程は高度かつ面倒臭そうである。ゆえに、製造コストは相応にお高そうなイメージが漂う。

次世代ノードは「Intel 14A」

今回のイベントでは、Intel 18Aの次世代プロセス「Intel 14A」も紹介された。

Intel 14Aは、リソグラフィー技術面の新技術として「High-NA EUV技術」を実用化している。EUVは先述の通り極端紫外線のことで、High-NAは「High-Numerical Aperture」、日本語にすると「高開口数」のことだ。開口数は光学用語で、対物レンズの集光範囲の指標で、値が大きいほどたくさんの光が集められることを表す。

リソグラフィー工程は、光の波長も短ければ短いほどよく、その集光レンズが明るければ明るいほど効率が高まる。光源としてEUVを活用している以上、波長は固定されるので、EUVリソグラフィーの効率を高めるには、開口数を高めるのが一番手っ取り早い。

そこで生まれたのがHigh-NA EUV技術だ。これはオランダの半導体製造装置メーカーである。ASMLが生み出した技術で、Intelも同社のHigh-NA EUVリソグラフィー装置を導入している。

Intelは、Intel 14Aプロセスと、同プロセスを拡張した「Intel 14A-E」を2025年以降2027年までに実用化する計画だ。

最後に、Intel Foundry Direct Connect 2024を通してIntelが“言いたかったこと”をまとめる。

関連記事

そのあふれる自信はどこから? Intelが半導体「受託生産」の成功を確信する理由【中編】

そのあふれる自信はどこから? Intelが半導体「受託生産」の成功を確信する理由【中編】

Intelが、半導体の受託生産事業「Intel Foundry」を本格的にスタートした。受託生産事業者(ファウンドリー)としては新参者でありながら、同社は既に自信満々のようである。それはなぜなのか、ちょっと深掘りして考察していこうと思う。 2030年までに“世界第2位”を目指す! Intelが半導体の「受託生産」に乗り出す理由【前編】

2030年までに“世界第2位”を目指す! Intelが半導体の「受託生産」に乗り出す理由【前編】

Intelの半導体受託生産事業「Intel Foundry」が本格的に始動した。研究/開発から生産まで一貫して行う垂直統合体制だった同社が、ここに来て受託生産(ファウンドリー)事業に注力し始めたのはなぜなのだろうか。この記事では、その動機(モチベーション)について考察していきたい。 Intelがファウンドリ事業のイノベーション促進に向けて10億ドルの基金を設立 RISC-V団体にも加盟

Intelがファウンドリ事業のイノベーション促進に向けて10億ドルの基金を設立 RISC-V団体にも加盟

米Intelは、自社で運営するファウンドリ事業のイノベーション促進に向けて10億ドル(約1150億円)の基金を設立すると発表した。 IntelとMediaTekがファウンドリー事業でパートナーシップを締結 IntelがMediaTekのチップを製造

IntelとMediaTekがファウンドリー事業でパートナーシップを締結 IntelがMediaTekのチップを製造

IntelとMediaTekがファウンドリー事業でのパートナーシップ締結を発表した。2021年7月には、Qualcomm向けのプロセッサ製造を発表済みだ。 2025年までに「1.8nm相当」に――Intelが半導体生産のロードマップを説明

2025年までに「1.8nm相当」に――Intelが半導体生産のロードマップを説明

Intelが半導体生産のロードマップを説明するイベントを開催した。2022年には7nmプロセスの製品が、2024年には新技術を取り入れた製品が登場する見通しだ。

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- 発表時の批判は裏返る? スペック据え置きでも“買い”と言える、極上の普段着スマホ「Pixel 10a」を触ってみた (2026年04月27日)

- サイボウズの社名由来 “坊主”に込められた意味が深すぎる (2016年07月29日)

- キーボード「FILCO」ブランドのダイヤテックが閉業 4月22日付で (2026年04月24日)

- マザーボードは「細部まで白」が今の主流? 高コスパ水冷など見逃せない最新自作PCパーツ事情 (2026年04月27日)

- 大型連休前のアキバは新CPUラッシュ! AMD「Ryzen 9 9950X3D2」とIntel「Core Ultra 5 250K Plus/KF Plus」の気になる在庫状況 (2026年04月25日)

- 次期「DaVinci Resolve 21」で写真編集が可能に/Google Cloudが第8世代TPUを発表 (2026年04月26日)

- エレコム、士郎正宗デザインマウス「M.A.P.P.」復刻モデルの予約販売を4月6日に開始 (2026年03月25日)

- エレコム、「士郎正宗 復刻マウス」発売日を延期 5月下旬の予定に (2026年04月27日)

- 持ち運びを極めた超軽量キーボード「ロジクール KEYS TO GO 2」が17%オフの9980円に (2026年04月23日)

- 部屋の雰囲気を一瞬で変えられる「SwitchBot RGBIC フロアライト」が15%オフの7633円に (2026年04月24日)