Intelの新型CPU「Core Ultraプロセッサ(シリーズ3)」は何が変わった? Lunar Lakeからの進化をチェック!(3/3 ページ)

PCI Express 5.0バスは最大でも12レーン

Panther Lakeには3つのパッケージが存在するが、以下の表はそのスペック比較だ。

GPUコアやNPUコア、IPU、Wi-Fi/Thunderbolt関連の接続性については別記事で紹介するとして、ここではPCI Expressバスの仕様についてチェックしたい。

Panther Lakeは基本的に内蔵のGPUコアを活用することを前提とした設計で、独立GPU(いわゆるグラフィックスカード)の接続は優先されていない。そのこともあり、外部機器との接続に用意したPCI Expressバスの最大レーン数は以下の通り限られている。

- 8コアCPU+4コアGPU/16コアCPU+12コアGPUパッケージ

- PCI Express 4.0:8レーン

- PCI Express 5.0:4レーン

- 16コアCPU+4コアGPUパッケージ

- PCI Express 4.0:8レーン

- PCI Express 5.0:12レーン

PCI Express 4.0バスはSerial ATAインタフェース、あるいはThunderbolt 5(USB4 Version 2.0)コントローラーや追加のUSBコントローラーなどのために用意されたと考えれば良いだろう。8コアCPU+4コアGPUと16コアCPU+12コアGPUパッケージのPCI Express 5.0バスは、レーン数からSSD用と考えるのが自然だ。

今どきの外部GPUを搭載することを考えると、16コアCPU+4コアGPUパッケージのPCI Express 5.0バスはある程度都合がよい。ただし、外部GPUの多くが16レーン接続だということを考えると「12レーン」という数は中途半端で、そもそも外部GPUを12レーン接続するのは難しい。

この点についてIntelに質問したところ、「外部GPUとの接続はPCI Express 5.0バスのうち8レーンで行うことになるだろう」とのことだった。計算上、この接続スタイルではPCI Express 5.0バスが4レーン余るが、これはSSD用ということになるだろう。

Panther LakeベースのゲーミングPCが出てきた場合、GPUとの接続はPCI Express 5.0 x16のフルスペックではない点には留意したいところだ。

Panther Lakeの特徴的なキャッシュ/クラスター構造

下図は、Pコアと、後述するEコア/LP Eコアのキャッシュ/クラスター構造を図解したものとなる。

ラストレベルキャッシュ(LLC)となるL3キャッシュは、Core Ultra 200Vプロセッサでは12MBだったところ、Panther Lakeでは最大18MBと1.5倍に増量された。このL3キャッシュは、4基のPコアと8基のEコアで共有されるため、均等割すると1コア当たりの容量はCore Ultra 200Vプロセッサと変わらない。

L2キャッシュは、Pコアでは1基あたり3MB搭載されている(最大3MB×4コア=12MB)。一方、EコアのL2キャッシュは4基で4MBを共有することになる(最大4MB×2クラスター=8MB)。LP EコアのL2キャッシュも、4基で4MBを共有する。

と、ここまで見て「あれ?」と思った人もいるかもしれないが、Panther Lakeの特筆すべき特徴として、LP EコアはL3キャッシュとリンクしていないことが挙げられる。ただし、キャッシュのコヒーレンシー(整合性)は保たれるようになっているので、LP Eコアがメモリの内容を書き換えた場合も問題はない。整合性の確保は上図の「Coherency Agent」と呼ばれる部位が担う。

とはいえ、このような仕様としたがゆえにLP Eコアではメモリアクセス時にL2キャッシュでミスが生じた場合に、L3キャッシュをあてにできない。「なぜそういう構造にしたのか?」と疑問が生じる所だが、これはLP Eコアを「低負荷処理に特化したコア」と位置付けて、他のCPUコアから電力ドメインを分離して稼働させることを優先したためだ。

バックグラウンド処理やI/O処理は局所ループで回ることが多く、この場合はL2キャッシュがヒットする。また、メモリへの書き出し処理も入出力バッファーへのアクセスが中心となるので、L3キャッシュへのコヒーレンシー維持はあまり意味をなさない。このことも、LP EコアをL3キャッシュとリンクしない構造とした理由だろう。

なお、現行のCore Ultra 200VプロセッサもLP EコアはL3キャッシュとリンクしない構造なので、今回が初めてというわけではない。

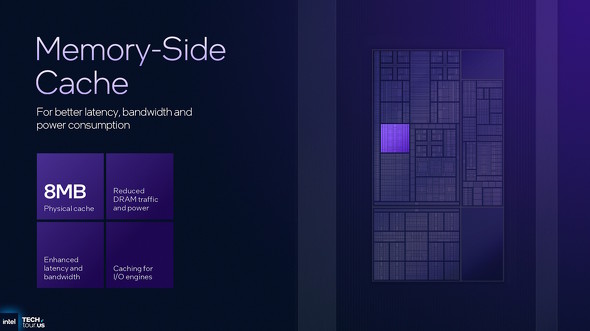

あらゆる処理系とつながる「Memory Side Cache」

一方で、LP Eコアは「Memory Side Cache(MSC)」には接続されている。

MSCはCore Ultra 200Vプロセッサにも搭載されていた、ユニークな汎用(はんよう)キャッシュメモリで、メインメモリに最も近い場所にある。容量は8MBと大きめで、全てのCPUコアはもちろん、GPUコア、NPUコア、メディアエンジン(ビデオプロセッサ)、ディスプレイエンジンにも接続されている。キャッシュとメモリのコヒーレンシーは、「Home Agent」がつかさどる。

MSCは事実上の「L4キャッシュ」に相当するのだが、IntelはL3キャッシュを「ラストレベルキャッシュ」と見なしている。このMSCはグラフィックス処理にも効果があり、特に反復した局所アクセスが集中する超解像処理系には効果が大きいはずだ

MSCは事実上の「L4キャッシュ」に相当するのだが、IntelはL3キャッシュを「ラストレベルキャッシュ」と見なしている。このMSCはグラフィックス処理にも効果があり、特に反復した局所アクセスが集中する超解像処理系には効果が大きいはずだ次回は、Panther LakeのCPUコア(Cougar Cove/Darkmont)について“深掘り”していく。

関連記事

Intelの「Core Ultraプロセッサ(シリーズ3)」は2025年末に一部出荷 2026年1月にはラインアップを拡充

Intelの「Core Ultraプロセッサ(シリーズ3)」は2025年末に一部出荷 2026年1月にはラインアップを拡充

Intelが、「Panther Lake」という開発コード名で開発を進めていたCPUを新しいCore Ultraプロセッサとして発売することになった。2025年内に大量生産を開始し、同年末に一部製品の出荷を開始する見通しだ。2026年1月には、より広範な製品を集荷するという。 Intelが次世代CPU「Panther Lake」を“チラ見せ” 製品は2026年初頭に発売予定

Intelが次世代CPU「Panther Lake」を“チラ見せ” 製品は2026年初頭に発売予定

Intelが「Core Ultraプロセッサ(シリーズ2)」の次に投入する予定のCPU「Panter Lake」のデモンストレーションを行った。量産は2025年後半から始まる予定で、搭載製品は2025年初頭に発売される見通しだ。 2025年までに「1.8nm相当」に――Intelが半導体生産のロードマップを説明

2025年までに「1.8nm相当」に――Intelが半導体生産のロードマップを説明

Intelが半導体生産のロードマップを説明するイベントを開催した。2022年には7nmプロセスの製品が、2024年には新技術を取り入れた製品が登場する見通しだ。 Intelが新プロセス「Intel 3」の詳細を発表 消費電力当たりの性能を最大18%向上

Intelが新プロセス「Intel 3」の詳細を発表 消費電力当たりの性能を最大18%向上

Intelが、VLSIシンポジウム2024に合わせて「Intel 3」の詳細を発表した。「Intel 4」の細かい部分を改良したプロセスだが、それが最大18%のパフォーマンス改善につながっているという。 「Core Ultraプロセッサ(シリーズ2)」は驚きの内蔵GPU性能に メモリ帯域が当初発表から“倍増”

「Core Ultraプロセッサ(シリーズ2)」は驚きの内蔵GPU性能に メモリ帯域が当初発表から“倍増”

IntelがLuna Lakeこと「Core Ultra 200Vプロセッサ」を発表した。Core Ultraプロセッサ(シリーズ2)のモバイル向けモデルという位置付けだが、どのような特徴があるのだろうか。ドイツ・ベルリンで開催された発表会で得られた情報をもとにまとめた。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- モジュール型ミニPC「Khadas Mind」をSurface風に変貌させる拡張ディスプレイ「Mind xPlay」レビュー (2026年05月06日)

- 思い出のビデオテープをPCなしでデジタル化できる「サンワダイレクト 400-MEDI034」が21%オフの2万5920円に (2026年04月30日)

- まるで工芸品な3kg超のアルミ塊! 官能的すぎる“磁気×メカニカル”なキーボード「Lofree Hyzen」を試す (2026年05月07日)

- VAIO事業が絶好調のノジマ、第4四半期の出荷台数は過去最高に 「AI PC」需要で次期も成長を見込む (2026年05月07日)

- 画面を持たない約12gの超軽量ウェルネストラッカー「Google Fitbit Air」 1万6800円で5月26日に発売 (2026年05月07日)

- ビジネスPCみたいな14型ボディーにRTX 5060とRyzen AIを詰め込んだ“本気”ゲーミングノートPC「ASUS TUF Gaming A14 (2026)」を試す (2026年05月06日)

- Macの容量不足をThunderbolt 5で解決! 80Gbps対応SSDケース「D1 SSD Pro」で爆速ローカルLLM環境を作る (2026年05月07日)

- デスク充電環境刷新のチャンス! 最大240Wの高出力「Anker Prime Charging Station (8-in-1, 240W)」が25%オフの1万4990円に (2026年05月06日)

- バッテリー残量を%表示できる「Ewin 折りたたみ式Bluetoothキーボード」が10%オフの6632円に (2026年05月06日)

- 「生成AIの出力は直しにくい」をどう克服? Canvaが仕掛ける“編集できる画像生成AI”の衝撃 (2026年05月05日)