Intelの新型CPU「Core Ultraプロセッサ(シリーズ3)」は何が変わった? Lunar Lakeからの進化をチェック!(2/3 ページ)

ダイのサイズは非公開だが推測してみる

近年、IntelはCPUのダイサイズやトランジスタ数を非公開としている。

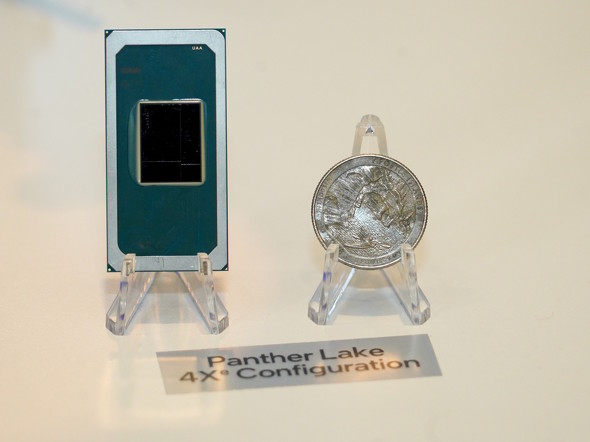

しかし、今回のイベントでは「16コアCPU+12コアGPU」「8コアCPU+4コアGPU」のパッケージの実物が展示されており、これについては撮影も可能だった。比較用に25セント硬貨と一緒に写した上で、ダイのサイズをAIに推測してもらった。AIはこういう時に便利である。

すると、16コアCPU+12コアGPUパッケージのダイ全体の概算面積は289mm2、8コアCPU+4コアGPUパッケージのダイ全体の概算面積は218mm2だという。Core Ultra 200Vプロセッサのオンパッケージメモリを除くダイ全体の面積は実測で220mm2だったという情報がある。そうすると、この概算値はPanther Lakeのダイとほぼ同じということになる。

ダイのサイズはTDP(熱設計電力)と無関係ではないので、今回AIが写真から算出した概算値には、それなりの信ぴょう性がありそうだ。

製造の要「Intel 18A」プロセスと「Foveros-S 2.5D」パッケージ

Panther Lakeは、クライアントPC向けの量産品CPUとしては初めて1.8nm相当の自社プロセス「Intel 18A」で生産される。ただし、実際のところは18Aプロセスで製造されるダイはCPUコア(Compute Tile)のみとなる。先述の通り、Panther Lakeでは8コアと16コアの2種類のCompute Tileがあるので、18Aプロセスでは2種類のタイルが製造されることになる。

一方、GPU Tileは4コア版は自社の3nm相当プロセスとなる「Intel 3」で、12コア版はTSMCの3nmプロセス「N3E」で製造される。I/O回りをつかさどる「Platform Controller Tile」については、TSMCの6nmプロセス「N6」で作られる。

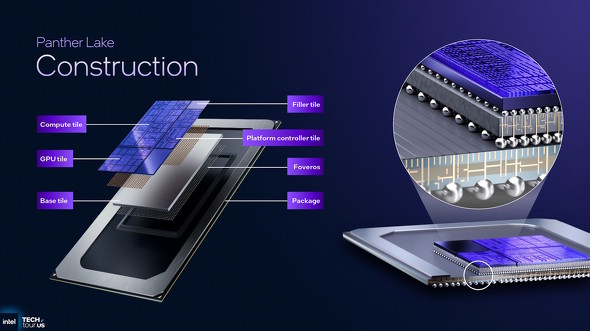

これら複数かつ異なる工場/プロセスで作られたタイルを1チップ化する工程では、Intelが誇るパッケージング技術「Foveros-S 2.5D」が採用されている。

Foverosには幾つかの種類があるが、Panther Lakeの製造に活用されるFoveros-S 2.5Dは、下図にあるように、トランジスタやロジックを一切持たない、配線のみを形成した「Base Tile」(≒パッシブベースタイル)の上に、各種ダイを集約実装する方式となる。

Foveros-Sの「-S」は、「シリコンインターポーザー」を意味している。もう少し具体的にいうと、パッシブベースタイルのことを指している。なぜ「3D」ではなくあえて「2.5D」と呼ぶのかというと、これは各ダイの集約実装をダイ同士を直付けするのではなく、“平面”たるBase Dieを介してマイクロバンプとTSV(Through Silicon Via)でつなぐ方式だからだ。

上の図版で金色のマイクロバンプは「F2F(Face to Face)マイクロバンプ」とも呼ばれるもので、ピッチは36μmだとされる。銀色の方は「C4(Controlled Collapsed Chip Connection)バンプ」と呼ばれ、ピッチは100μm級となる。

Intel 18Aプロセスでは「RibbonFET」(GAAトランジスタ)や「PowerVia」といった新技術も採用されているが、その詳細は別記事で紹介したい。

各タイルの接続方法にも特徴が

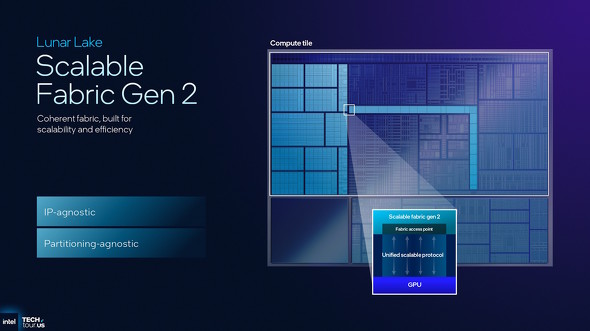

Panther Lakeでは、Foveros-S 2.5Dによって積み上げた各タイルを「Scalable Fabric Gen 2(SFG2)」で束ねるような構造となっていることも特徴だ。

SFG2は、単なるダイ同士のインターコネクト規格ではなく、CPU/GPU/NPU/PCH(チップセット)といった種類の異なるロジック同士の物理的な接続を、同じプロトコル(SFG2プロトコル)でやりとりできることが最大の特徴だ。

つまり、SFG2はダイ同士の物理接続を一本化した上で、種類の異なる信号/データを送り合えるように論理層を多層化したファブリック層(チップ内接続ネットワーク)ということになる。異なる種類のプロセッサ同士におけるキャッシュコヒーレンシーの維持設定も行えるなど、中身はかなり高度なものだ。

昨今、IntelとNVIDIAの協業計画が注目を集めたばかりだが、SFG2は、まさに異なるメーカーのプロセッサをIntelプロセッサに組み込む上で“要”となる技術といえる。思想としては、先行して実用化されているAMDの「Infinty Fabric」とよく似たものだともいえる。

SFG2自体はCore Ultra 200Vプロセッサでも採用されているが、Compute Tile上に設けた接続ポイント「Fabric Access Point(FAP)」においてGPU Tileを始めとする他のタイル(ダイ)を接続する方式を取っていた

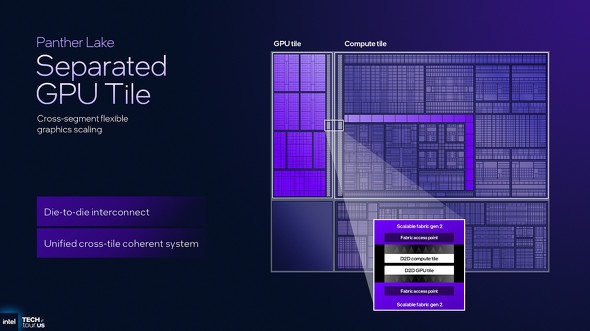

SFG2自体はCore Ultra 200Vプロセッサでも採用されているが、Compute Tile上に設けた接続ポイント「Fabric Access Point(FAP)」においてGPU Tileを始めとする他のタイル(ダイ)を接続する方式を取っていた Panther LakeのSFG2でも、接続ポイントとしてFAPを用いるのは変わりないのだが、各ダイが要所にあるFAPさえ接続すればダイをまたいだ相互接続を行ったことになる。この新たなスタイルこそが、Foveros-S 2.5Dによって実現できたものだと考えていいだろう

Panther LakeのSFG2でも、接続ポイントとしてFAPを用いるのは変わりないのだが、各ダイが要所にあるFAPさえ接続すればダイをまたいだ相互接続を行ったことになる。この新たなスタイルこそが、Foveros-S 2.5Dによって実現できたものだと考えていいだろう関連記事

Intelの「Core Ultraプロセッサ(シリーズ3)」は2025年末に一部出荷 2026年1月にはラインアップを拡充

Intelの「Core Ultraプロセッサ(シリーズ3)」は2025年末に一部出荷 2026年1月にはラインアップを拡充

Intelが、「Panther Lake」という開発コード名で開発を進めていたCPUを新しいCore Ultraプロセッサとして発売することになった。2025年内に大量生産を開始し、同年末に一部製品の出荷を開始する見通しだ。2026年1月には、より広範な製品を集荷するという。 Intelが次世代CPU「Panther Lake」を“チラ見せ” 製品は2026年初頭に発売予定

Intelが次世代CPU「Panther Lake」を“チラ見せ” 製品は2026年初頭に発売予定

Intelが「Core Ultraプロセッサ(シリーズ2)」の次に投入する予定のCPU「Panter Lake」のデモンストレーションを行った。量産は2025年後半から始まる予定で、搭載製品は2025年初頭に発売される見通しだ。 2025年までに「1.8nm相当」に――Intelが半導体生産のロードマップを説明

2025年までに「1.8nm相当」に――Intelが半導体生産のロードマップを説明

Intelが半導体生産のロードマップを説明するイベントを開催した。2022年には7nmプロセスの製品が、2024年には新技術を取り入れた製品が登場する見通しだ。 Intelが新プロセス「Intel 3」の詳細を発表 消費電力当たりの性能を最大18%向上

Intelが新プロセス「Intel 3」の詳細を発表 消費電力当たりの性能を最大18%向上

Intelが、VLSIシンポジウム2024に合わせて「Intel 3」の詳細を発表した。「Intel 4」の細かい部分を改良したプロセスだが、それが最大18%のパフォーマンス改善につながっているという。 「Core Ultraプロセッサ(シリーズ2)」は驚きの内蔵GPU性能に メモリ帯域が当初発表から“倍増”

「Core Ultraプロセッサ(シリーズ2)」は驚きの内蔵GPU性能に メモリ帯域が当初発表から“倍増”

IntelがLuna Lakeこと「Core Ultra 200Vプロセッサ」を発表した。Core Ultraプロセッサ(シリーズ2)のモバイル向けモデルという位置付けだが、どのような特徴があるのだろうか。ドイツ・ベルリンで開催された発表会で得られた情報をもとにまとめた。

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- モジュール型ミニPC「Khadas Mind」をSurface風に変貌させる拡張ディスプレイ「Mind xPlay」レビュー (2026年05月06日)

- 思い出のビデオテープをPCなしでデジタル化できる「サンワダイレクト 400-MEDI034」が21%オフの2万5920円に (2026年04月30日)

- まるで工芸品な3kg超のアルミ塊! 官能的すぎる“磁気×メカニカル”なキーボード「Lofree Hyzen」を試す (2026年05月07日)

- VAIO事業が絶好調のノジマ、第4四半期の出荷台数は過去最高に 「AI PC」需要で次期も成長を見込む (2026年05月07日)

- 画面を持たない約12gの超軽量ウェルネストラッカー「Google Fitbit Air」 1万6800円で5月26日に発売 (2026年05月07日)

- ビジネスPCみたいな14型ボディーにRTX 5060とRyzen AIを詰め込んだ“本気”ゲーミングノートPC「ASUS TUF Gaming A14 (2026)」を試す (2026年05月06日)

- Macの容量不足をThunderbolt 5で解決! 80Gbps対応SSDケース「D1 SSD Pro」で爆速ローカルLLM環境を作る (2026年05月07日)

- デスク充電環境刷新のチャンス! 最大240Wの高出力「Anker Prime Charging Station (8-in-1, 240W)」が25%オフの1万4990円に (2026年05月06日)

- バッテリー残量を%表示できる「Ewin 折りたたみ式Bluetoothキーボード」が10%オフの6632円に (2026年05月06日)

- 「生成AIの出力は直しにくい」をどう克服? Canvaが仕掛ける“編集できる画像生成AI”の衝撃 (2026年05月05日)