Intelの「Core Ultraプロセッサ(シリーズ3)」は2025年末に一部出荷 2026年1月にはラインアップを拡充:開発コード名は「Panther Lake」

Intelは10月9日(米国太平洋夏時間)、「Panther Lake」というコード名で開発を進めてきたモバイル向け新型CPU「Core Ultraプロセッサ(シリーズ3)」の大量生産を2025年内に開始することを発表した。一部製品は2025年末までに出荷を開始する予定で、2026年1月にはより広範な製品を出荷する見通しだ。

Core Ultraプロセッサ(シリーズ3)の概要

Core Ultraプロセッサ(シリーズ3)は現行のCore Ultra 200Vプロセッサ(開発コード名:Lunar Lake)並みの電力効率性と、Core Ultra 200H/Uプロセッサ(開発コード名:Arrow Lake)並みのスケーラビリティーを確保したことが特徴で、CPUコアは自社の「Intel 18A」プロセスで製造される。

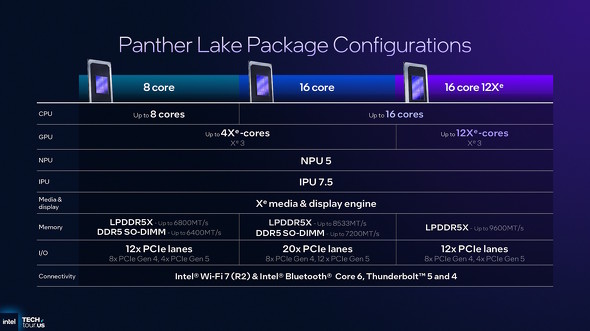

スケーラビリティーの面では、求められる性能や価格帯に応じて以下の3種類のパッケージ(チップ)が用意される。

- 8コア(Pコア4基+LP Eコア4基)

- 16コア(Pコア4基+Eコア8基+LP Eコア4基)

- 16コア 12Xe(16コアモデルのGPUコアを強化したもの)

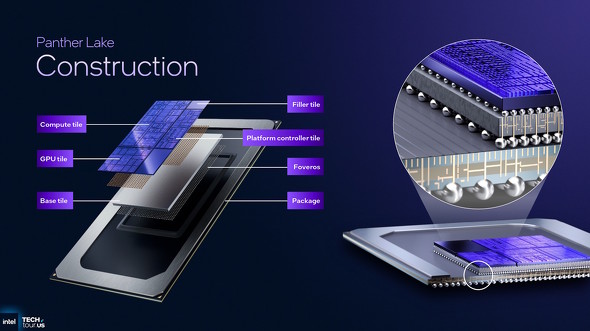

いずれのパッケージもタイル(チップレット)構造は維持しており、CPUコアやNPUコアなどを統合した「Computeタイル」、GPUコアを備える「GPUタイル」と、入出力回りを担う「Platform Controllerタイル」の3つを組み合わせて作られる。ComputeタイルとGPUタイルは自社プロセスで製造されるが(※1)、Platform Controllerタイルは他社に製造を委託する。

(※1)16コア 12Xe仕様については、GPUタイルも他社に製造を委託

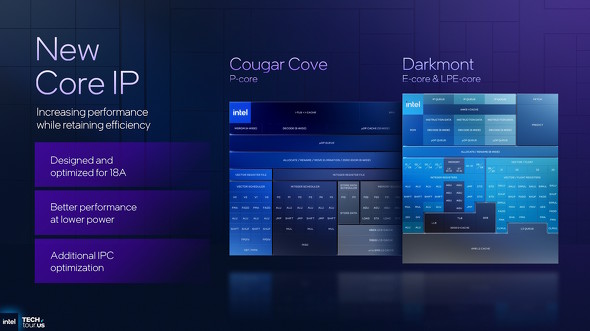

CPUコアは「Cougar Cove」と「Darkmont」の2種類

Core Ultraプロセッサ(シリーズ3)のCPUコアのうち、パフォーマンスコア(Pコア)は「Cougar Cove」、高効率コア(Eコア)と低消費電力コア(LP Eコア)は「Darkmont」というアーキテクチャで作られている。いずれもIntel 18Aプロセスに最適化した設計で、低消費電力時におけるパフォーマンス改善と、クロック当たりの命令数(IPC)の最適化が図られている。

8コアパッケージはPコアとLP Eコアを4基ずつ搭載し、16コア/16コア 12XeパッケージではこれにEコアを8基追加している。いずれのコアもハイパースレッディング(マルチスレッド動作)には対応しない。

同一消費電力時では、Core Ultra 200Vプロセッサ比でシングルスレッドの性能は10%超、Core Ultra 200V/Hプロセッサ比でマルチスレッド性能は50%超向上するという。

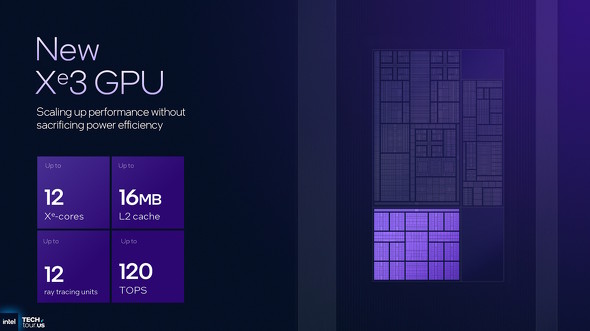

GPUコアは「Xe3アーキテクチャ」

Core Ultraプロセッサ(シリーズ3)のGPUコアは、自社開発で最新の「Xe3アーキテクチャ」を採用している。従来のXe/Xe2アーキテクチャと同様にスケーラビリティーを重視した設計で、8コア/16コアパッケージではXeコア(演算エンジン)とレイトレーシングユニットを最大4基、16コア 12XeパッケージではXeコアとレイトレーシングユニットを最大12基搭載している。

GPUコアのパフォーマンスは、Core Ultra 200V/Hプロセッサに搭載しているものの1.5倍超になったという。

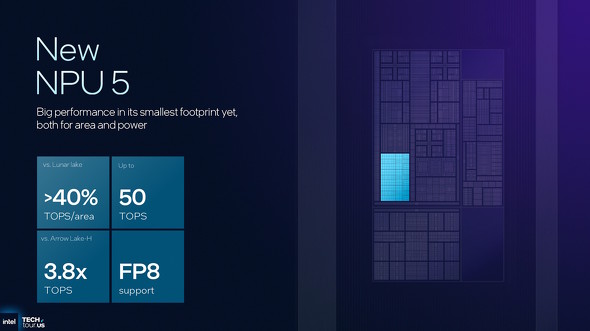

NPUコアのピーク性能は50TOPSに

Core Ultraプロセッサ(シリーズ3)のNPUコア(Intel AI Engine)は、第5世代(NPU 5)となった。ピーク時の演算性能は最大50TOPS(毎秒50兆回)で、FP8(8bit浮動小数点演算)のネイティブサポートを追加している。

NPU 5はCore Ultra 200Vプロセッサ比でエリア当たりの処理パフォーマンスが40%以上向上し、Core Ultra 200Hプロセッサ比で演算性能が3.8倍向上したという。

最上位構成のチップの場合、CPUコア(10TOPS)+GPUコア(120TOPS)+NPUコア(50TOPS)で、理論上の最大性能は180TOPSとなる。

その他の特徴

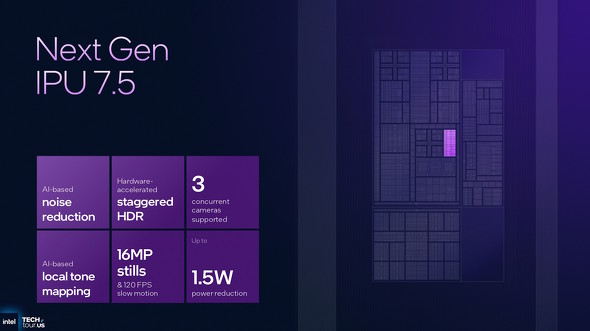

内蔵カメラの処理を行う「IPU」と動画のエンコード/デコードを担う「Xe Media Engine」は、CPUコアと同じComputeタイル内にある。

IPUは第7.5世代(IPU 7.5)となり、Core Ultra 200Vプロセッサに搭載されている「IPU 7」比で消費電力が最大1.5W削減された。

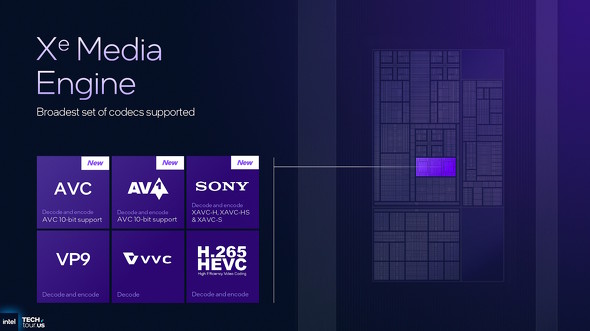

Xe Media Engineでは、「AVC(H.264)」「AV1」コーデックにおいて10bitデータのエンコード/デコードに対応した他、ソニーの独自フォーマット「XAVC-H」「HAVC-HS」「XAVC-S」のエンコード/デコード機能を追加している。

Platform Controllerには、Wi-Fi 7 Release 2(IEEE 802.11be)/Bluetooth Core 6.x対応の通信機能と、Thunderbolt 4(USB4 Version 1.0)コントローラー(最大4ポート)、USBコントローラー(USB 3.2規格最大2ポート+USB 2.0規格最大8ポート)を統合している。Thunderbolt 5(USB4 Version 2.0)を搭載する場合は、コントローラーチップを別途搭載する必要がある。

PCI Expressバスのレーン数は、パッケージによって以下の通り異なる。

- 8コア:PCI Express 5.0 x4+PCI Express 4.0 x8(合計12レーン)

- 16コア:PCI Express 5.0 x12+PCI Express 4.0 x8(合計20レーン)

- 16コア 12Xe:PCI Express 5.0 x4+PCI Express 4.0 x8(合計12レーン)

メモリモジュールはLPDDR5X規格の他、16コア 12Xeパッケージを除きDDR5規格も利用可能だ。最大速度(MT値)は、パッケージによって以下の通り異なる。

- 8コア:LPDDR5X-6800/DDR5-6400

- 16コア:LPDDR5X-8533/DDR5-7200

- 16コア 12Xe:LPDDR5X-9600

関連記事

Intelが次世代CPU「Panther Lake」を“チラ見せ” 製品は2026年初頭に発売予定

Intelが次世代CPU「Panther Lake」を“チラ見せ” 製品は2026年初頭に発売予定

Intelが「Core Ultraプロセッサ(シリーズ2)」の次に投入する予定のCPU「Panter Lake」のデモンストレーションを行った。量産は2025年後半から始まる予定で、搭載製品は2025年初頭に発売される見通しだ。 試して分かった「Core Ultra 200V」の実力! Intelの新型CPUはゲームチェンジャーだと思ったワケ 現行ノートPCとの決定的な違いは?

試して分かった「Core Ultra 200V」の実力! Intelの新型CPUはゲームチェンジャーだと思ったワケ 現行ノートPCとの決定的な違いは?

Intelのモバイル向け最新SoC「Core Ultra 200Vプロセッサ」を搭載するノートPCが、いよいよ発売される。今までのIntel製CPUにはない特徴を多く備えた本製品の実像はいかほどのものか、「ASUS Zenbook S 14(UX5406)」のCore Ultra 258Vモデルを通してチェックしていく。 Intelが新プロセス「Intel 3」の詳細を発表 消費電力当たりの性能を最大18%向上

Intelが新プロセス「Intel 3」の詳細を発表 消費電力当たりの性能を最大18%向上

Intelが、VLSIシンポジウム2024に合わせて「Intel 3」の詳細を発表した。「Intel 4」の細かい部分を改良したプロセスだが、それが最大18%のパフォーマンス改善につながっているという。 次世代CPU「Lunar Lake」でIntelが目指す“AI PC”とは? 驚くべき進化点と見える弱点、その克服法

次世代CPU「Lunar Lake」でIntelが目指す“AI PC”とは? 驚くべき進化点と見える弱点、その克服法

COMPUTEX TAIPEI 2024に先立って、Intelが今後発売される予定のCPUに関する技術説明会を開催した。この記事では、2024年第4四半期に登場する予定のモバイル向けCPU「Lunar Lake」(開発コード名)の技術的概要を紹介する。 2025年までに「1.8nm相当」に――Intelが半導体生産のロードマップを説明

2025年までに「1.8nm相当」に――Intelが半導体生産のロードマップを説明

Intelが半導体生産のロードマップを説明するイベントを開催した。2022年には7nmプロセスの製品が、2024年には新技術を取り入れた製品が登場する見通しだ。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- Windows 11(24H2/25H2)の新「スタートメニュー」で問題発生 追加/削除したアイコンの反映にタイムラグ (2026年04月17日)

- アキバは早くもGWモードに! 20万円購入でゲーミングディスプレイをもらえる大盤振る舞いも (2026年04月18日)

- 「DJI Osmo Pocket 4」速攻レビュー Pocket 3から買い換える価値はある? 進化したポイントを実機で比較した (2026年04月16日)

- 複雑な設定不要で高精度な造形ができる3Dプリンタ「Bambu Lab A1 mini」が25%オフの2万9999円に (2026年04月17日)

- Appleはいかにして「今日のAIやWeb」を予見したのか? “暗黒時代”とも呼ばれた1985〜1996年の光と影 (2026年04月17日)

- キングジム、「ポメラ DM250」にクリアパープル筐体採用の特別モデル 500台限定 (2026年04月17日)

- IntelがNPU内蔵エントリーCPU「Core シリーズ3」を発表 (2026年04月17日)

- 「Jackery ポータブル電源 2000 New」が43%オフの11万9898円に (2026年04月17日)

- Googleの「パーソナル インテリジェンス」が日本でも提供開始/Windows 11の初回セットアップ時にOSアップデートがスキップ可能に (2026年04月19日)

- 最新PCサブスクからオンデバイスAI、カラフルなエッジPCまで「情シスの負担を減らす」最前線を見てきた (2026年04月19日)