96層QLCの「Intel 665P」をデモ さらに144層QLCへ――「Intel Memory & Storage Day」レポート(2/4 ページ)

» 2019年10月01日 13時00分 公開

[鈴木雅暢,ITmedia]

144層QLC NANDも準備中 1セルあたり5bit記録も

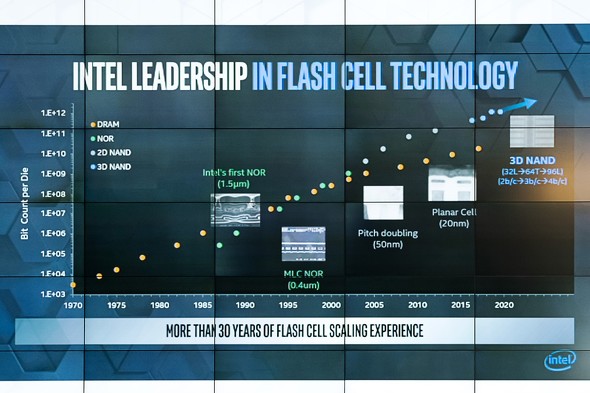

イベントの基調講演では、Intelの3D NANDフラッシュの技術的な優位性やロードマップも示された。

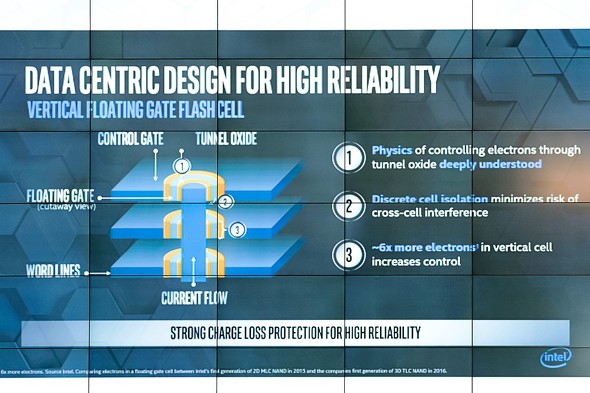

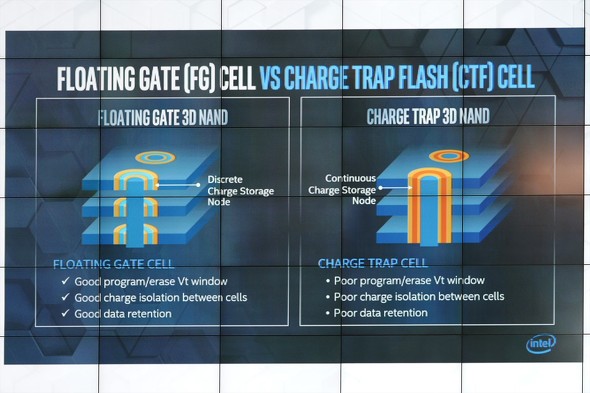

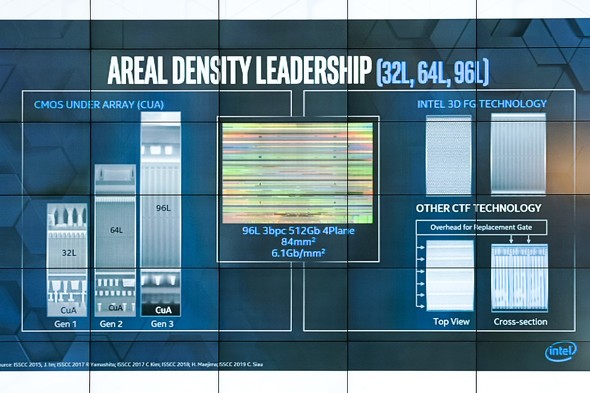

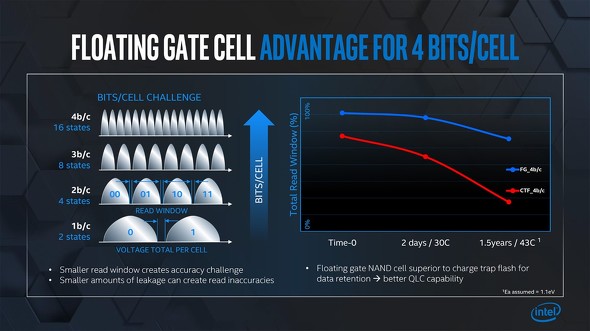

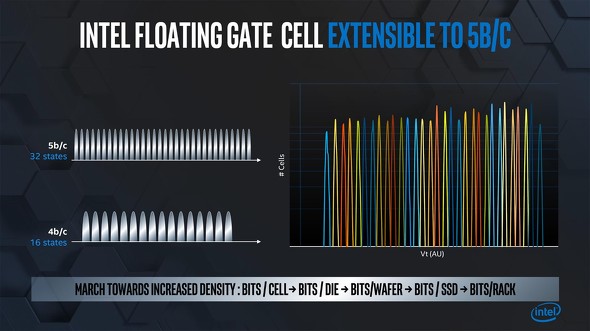

Intelの3D NANDフラッシュメモリは、データの記録に「フローティングゲート(浮遊ゲート)方式」を採用していることを強調。この方式は、競合他社が採用している「チャージトラップ(電荷捕獲)方式」に比べて、データの保持能力が高く、耐久性で有利なことが特徴だ。層間での電気的干渉が無いことから多層化も容易で、データセンター向け製品として2020年内にも144層モデル(開発コードネーム「Arbordale+」)を投入するロードマップが公開された。

さらに、「1セルあたり5bit記録」についても、製品化を前提に評価を進めていることも明らかにされた。1セルあたりに4bitを記録するQLC NANDは、16段階の電圧操作を必要としている。それに対して1セルあたり5bitを記録する5bit/CELLでは、1セルあたりの記録容量をQLCの1.25倍に増やせる一方、電圧操作は32段階と難易度が上がることになる。

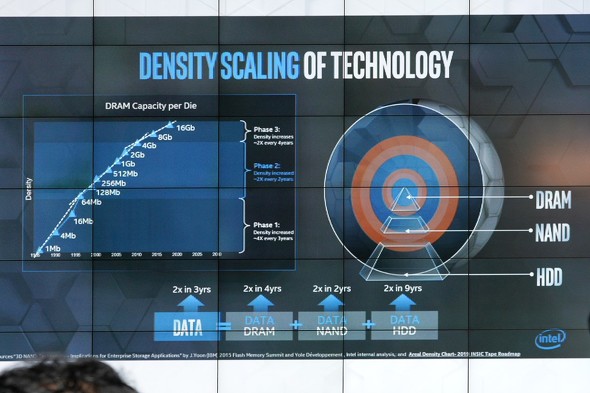

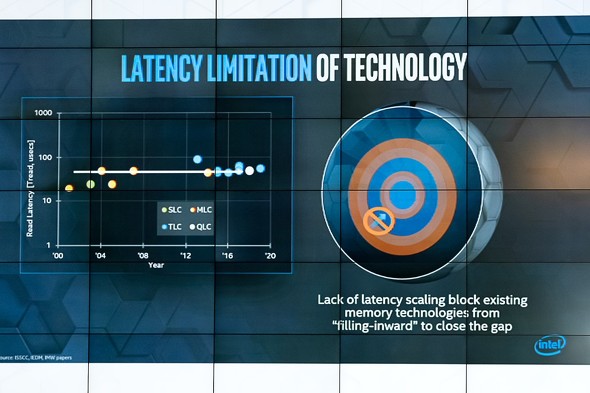

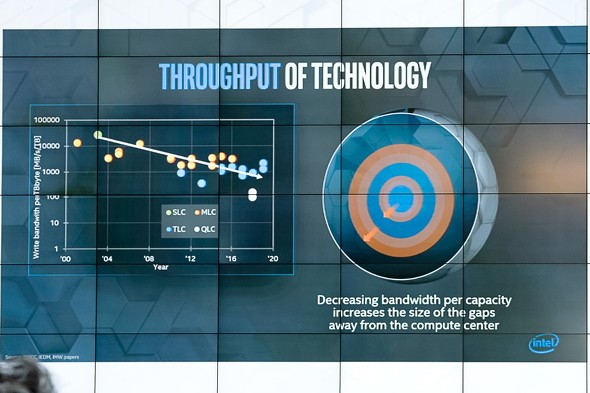

クライアントレベルでのメモリ階層モデル。データ増量ペースに既存デバイスの技術革新ペースが追いつかないことから、DRAMとNAND、NANDとHDDの間に性能や容量のギャップが生じる(十分な性能、容量を提供できなくなる)

クライアントレベルでのメモリ階層モデル。データ増量ペースに既存デバイスの技術革新ペースが追いつかないことから、DRAMとNAND、NANDとHDDの間に性能や容量のギャップが生じる(十分な性能、容量を提供できなくなる)関連記事

Intel、Optaneテクノロジーを標準装備したM.2 SSD「インテル Optane メモリー H10」

Intel、Optaneテクノロジーを標準装備したM.2 SSD「インテル Optane メモリー H10」

Intelは、OptaneテクノロジーとQLC 3D NANDを統合したM.2 SSD「インテル Optane メモリー H10」を発表した。 100ドル切りの512GB M.2 NVMe SSD登場 しかもIntel製

100ドル切りの512GB M.2 NVMe SSD登場 しかもIntel製

Intelは、QLC 3D NANDを採用したM.2 NVMe SSD「660p」シリーズを発表。512GBモデルで市場想定価格99ドルという低価格を実現した。 16万円弱のSSD「Optane SSD 905P」がアキバで予想以上の反響

16万円弱のSSD「Optane SSD 905P」がアキバで予想以上の反響

Intelのエンスージアスト向けSSD「Optane SSD 905P」が複数店に入荷し、税込み16万円弱という価格ながら好調に売れている。NVMe M.2 SSDも新製品が豊富だ。 最新のIntel NUCで自作して分かった2つの驚き

最新のIntel NUCで自作して分かった2つの驚き

Intelの超小型PC「NUC」を手に入れたとあるユーザーが、ほぼ5年ぶりにPCを自作。すっかりさび付いていた“自作魂”に火をつけたものとは何だったのでしょうか。

Copyright © ITmedia, Inc. All Rights Reserved.

SpecialPR

SpecialPR

アクセストップ10

2026年05月24日 更新

- 日本が舞台のオープンワールドレースゲーム「Forza Horizon 6」は、土地の空気感まで再現された圧倒的リアルさ 車好きでなくとも絶対ハマる理由 (2026年05月23日)

- かわいらしい水色が魅力の「Omikamo 折り畳み式Bluetoothキーボード」がタイムセールで25%オフの5688円に (2026年05月22日)

- どんな場面で役立つ? 「サンワダイレクト ペン型マウス 400-MAWBT202R」がタイムセールで23%オフの5380円に (2026年05月22日)

- 26万円のASUS製Ryzenマザーが即完売! 33万円引きの特価グラフィックスカードなど秋葉原を騒がせた目玉パーツ (2026年05月23日)

- スマホを開かずに天気や予定をひと目で把握できる「SwitchBot スマートデイリーステーション」がタイムセールで14%オフの1万3680円に (2026年05月22日)

- メモリ容量が最大192GBに! AMDが新型モンスターAPU「Ryzen AI Max PRO 400」を発表 (2026年05月22日)

- バッテリー着脱式! Ryzen AI Max+ 395で驚異の性能をたたき出すポータブルPC「OneXFly APEX」を試す (2026年05月22日)

- 小さすぎるモバイルマウス「サンワダイレクト 400-MAWB216GM」が18%オフで販売中 (2026年05月22日)

- AMDが強々なミニPC「Ryzen AI Halo」を披露 NVIDIAのミニスパコンに“汎用性”で対抗 (2026年05月22日)

- VAIOが個人向け製品を統一価格で提供する「指定価格制度」を開始 (2026年05月22日)

最新トピックスPR