最大128コア! AMDが第4世代EPYCに「多コア全振りモデル」と「L3キャッシュ爆増しモデル」を追加

» 2023年06月15日 07時00分 公開

[井上翔,ITmedia]

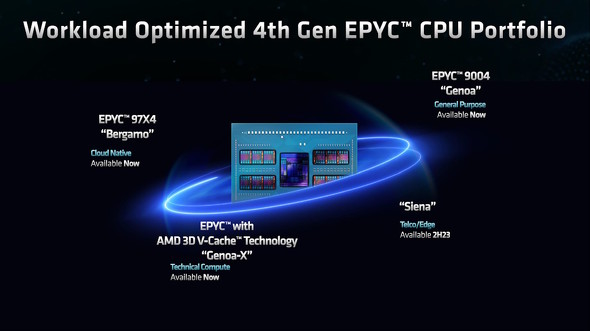

AMDは6月13日(米国太平洋夏時間)、データセンター向けCPU「第4世代EPYCプロセッサ」のスケーラビリティー重視モデル(開発コード名:Bergamo)と、3D V-Cacheテクノロジーを適用してL3キャッシュを増量したモデル(開発コード名:Genoa-X)の出荷開始を発表した。

EPYC 97X4プロセッサ(開発コード名:Bergamo)

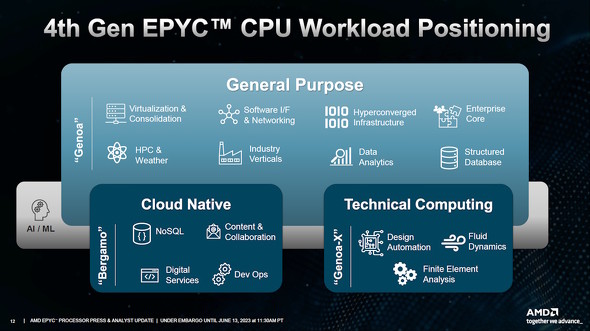

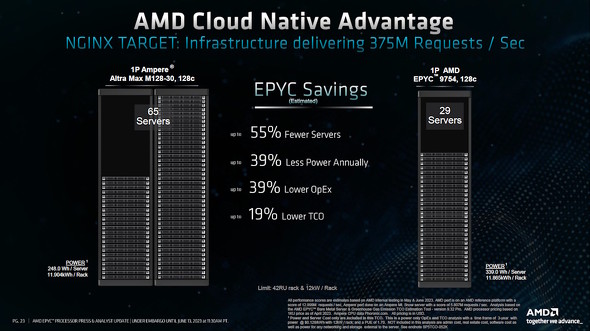

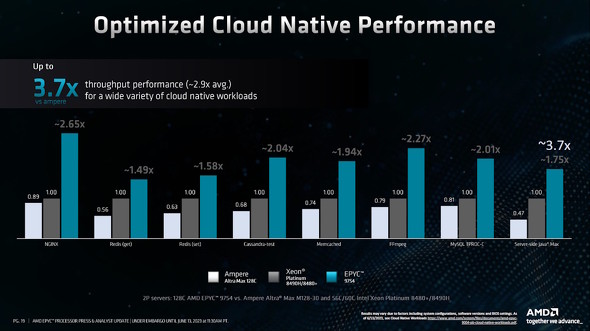

クラウドネイティブなサービスを提供するデータセンター(サーバ)への導入を前提に、スケーラビリティーを重視したBergamoは「EPYC 97X4プロセッサ」という名称で製品化された。

CPUコアはスケーラビリティーを重視した「Zen 4cアーキテクチャ」で、最大で128コア256スレッド構成となる。オリジナルの「Zen 4アーキテクチャ」と比べると1コア当たりの性能は若干低いが、サーバエンドで稼働する仮想マシン(VM)など、物理コア(や論理スレッド)がたくさん必要な用途では稼働効率が高まるというメリットがある。

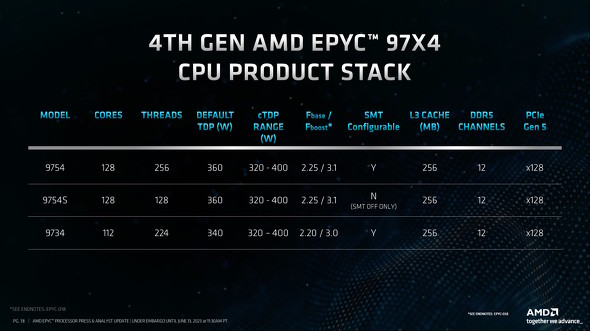

ラインアップは以下の通り。

- EPYC 9734

- CPUコア:112コア224スレッド

- 動作クロック:2.2GHz〜3GHz

- L3キャッシュ:256MB

- TDP:320〜400W(定格は340W)

- EPYC 9754

- CPUコア:128コア256スレッド

- 動作クロック:2.25GHz〜3.1GHz

- L3キャッシュ:256MB

- TDP:320〜400W(定格は360W)

- EPYC 9754S(マルチスレッド非対応)

- CPUコア:128コア128スレッド

- 動作クロック:2.25GHz〜3.1GHz

- L3キャッシュ:256MB

- TDP:320〜400W(定格は360W)

3D V-Cache搭載第4世代EPYCプロセッサ

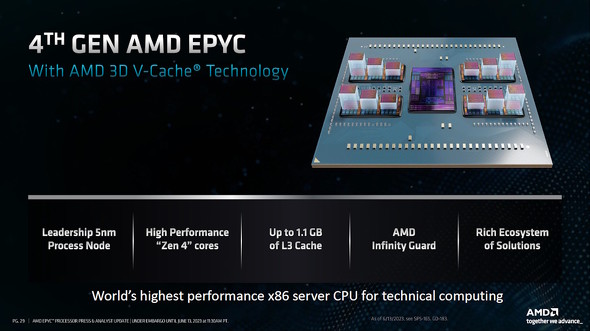

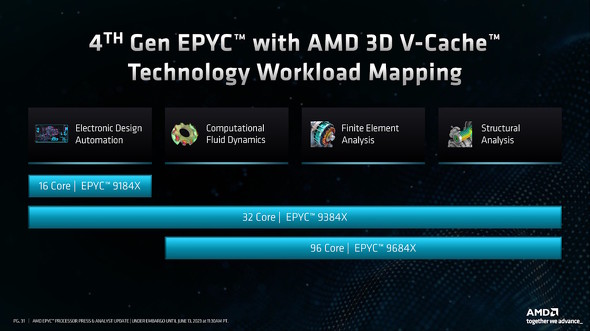

Genoa-Xは「AMD 3D V-Cache搭載第4世代EPYCプロセッサ」として投入される。開発コード名から分かる通り、オリジナルの第4世代EPYCプロセッサ(開発コード名:Genoa)に3D V-Cache Technologyを適用したCPUで、L3キャッシュを最大で1.1GBまで拡張している。

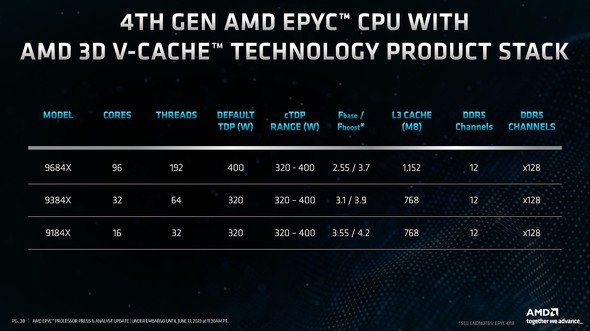

ラインアップは以下の通り。

- EPYC 9184X

- CPUコア:16コア32スレッド

- 動作クロック:3.55GHz〜4.2GHz

- L3キャッシュ:768MB

- TDP:320〜400W(定格は320W)

- EPYC 9384X

- CPUコア:32コア64スレッド

- 動作クロック:3.1GHz〜3.9GHz

- L3キャッシュ:768MB

- TDP:320〜400W(定格は320W)

- EPYC 9684X

- CPUコア:96コア192スレッド

- 動作クロック:2.55GHz〜3.7GHz

- L3キャッシュ:1152MB

- TDP:320〜400W(定格は400W)

関連記事

最大96コアでライバルを撃墜!? AMDがHPC/データセンター向けCPU「第4世代EPYC」を発売 最大1.9倍のパフォーマンス向上

最大96コアでライバルを撃墜!? AMDがHPC/データセンター向けCPU「第4世代EPYC」を発売 最大1.9倍のパフォーマンス向上

AMDが、Zen 4アーキテクチャベースのHPC/データセンター向けCPU「EPYC 9004シリーズ(第4世代EPYC)」を発売した。前世代と比べると最大で1.9倍のパフォーマンス向上を図った他、ライバルのIntelの現行製品である第3世代Xeonスケーラブルプロセッサと比べると、最大2.8倍(処理内容によっては3倍)のパフォーマンスを発揮できるという。 Zen 4アーキテクチャの「Ryzen PROプロセッサ」登場 モバイル向けは一部を除きAIプロセッサを搭載

Zen 4アーキテクチャの「Ryzen PROプロセッサ」登場 モバイル向けは一部を除きAIプロセッサを搭載

AMDが企業向けの管理/セキュリティ機能を強化したCPUを発表した。モバイル向けの「Ryzen PRO 7040シリーズ」は、エントリーモデルを除き機械学習ベースのAIを処理するための専用プロセッサを搭載しており、オンデバイスAI処理が高速にこなせることが特徴だ。 AI処理パフォーマンスを大きく改善 4nmプロセスのモバイルAPU「Ryzen 7040シリーズ」登場 搭載製品は3月以降に登場

AI処理パフォーマンスを大きく改善 4nmプロセスのモバイルAPU「Ryzen 7040シリーズ」登場 搭載製品は3月以降に登場

AMDの最新CPUアーキテクチャ「Zen 4」が、いよいよモバイル向けに登場する。メインストリームとなるRyzen 7040シリーズでは、CPUコアが4nmプロセスとなり省電力性能が高まった他、最新の「RDNA 3アーキテクチャ」のGPUや独立したAIアクセラレーターも統合していることも特徴だ。 AMDがモバイル向けプロセッサの「モデル名」のルールを改定 2023年以降の新製品から適用

AMDがモバイル向けプロセッサの「モデル名」のルールを改定 2023年以降の新製品から適用

AMDが、2023年以降に新規出荷されるモバイル向けプロセッサ(APU)からモデル名の付与ルールを変更する。同一年内に異なる複数のアーキテクチャの製品を投入することから、位置付けを含めて区別をしやすくするための措置で、少なくとも3年間は適用されるようである。 “6nmプロセス化”だけではない! AMDがモバイル向け「Ryzen 6000シリーズ」の進化を力説

“6nmプロセス化”だけではない! AMDがモバイル向け「Ryzen 6000シリーズ」の進化を力説

AMDが、CES 2022で披露したモバイル向けRyzen 6000シリーズプロセッサの詳細を解説するイベントを2度に渡って開催した。競合のIntelが製品の競争力の面で復活しつつある中、弱点を徹底的につぶした上で強みをより強化することで再び優位性をアピールできるAPU(GPU統合型CPU)に仕上がった。【訂正】

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

SpecialPR

SpecialPR

アクセストップ10

2026年04月27日 更新

- キーボード「FILCO」ブランドのダイヤテックが閉業 4月22日付で (2026年04月24日)

- サイボウズの社名由来 “坊主”に込められた意味が深すぎる (2016年07月29日)

- 次期「DaVinci Resolve 21」で写真編集が可能に/Google Cloudが第8世代TPUを発表 (2026年04月26日)

- 発表時の批判は裏返る? スペック据え置きでも“買い”と言える、極上の普段着スマホ「Pixel 10a」を触ってみた (2026年04月27日)

- 大型連休前のアキバは新CPUラッシュ! AMD「Ryzen 9 9950X3D2」とIntel「Core Ultra 5 250K Plus/KF Plus」の気になる在庫状況 (2026年04月25日)

- 持ち運びを極めた超軽量キーボード「ロジクール KEYS TO GO 2」が17%オフの9980円に (2026年04月23日)

- Windows 11の使い勝手はどう変わる? 「Copilot」名称外しやInsider Program再編に見るMicrosoftの本気度 (2026年04月24日)

- 部屋の雰囲気を一瞬で変えられる「SwitchBot RGBIC フロアライト」が15%オフの7633円に (2026年04月24日)

- ACアダプター不要の外付けHDD「Seagate One Touch Desktop External Hard Drive」を試す 超大容量で配線スッキリ (2026年04月24日)

- 2026年版Surfaceはどうなる? 正面衝突を避けるMicrosoft、10万円切り「MacBook Neo」対抗への秘策はあるか (2026年04月21日)

最新トピックスPR