Core Ultra(シリーズ2)にデスクトップ/ハイエンドモバイル向けモデルが登場! これまでのIntel製CPUとの決定的な違い(3/5 ページ)

「ハイパースレッディング非対応」になったPコア/Eコアも性能アップ

ここからは、Arrow LakeのComputeタイル(CPUコア)の特徴を見ていこう。

Core Ultra 200Sプロセッサの場合、Computeタイルはパフォーマンスコア(Pコア)が最大8基、高効率コア(Eコア)が最大16基という構成となる。

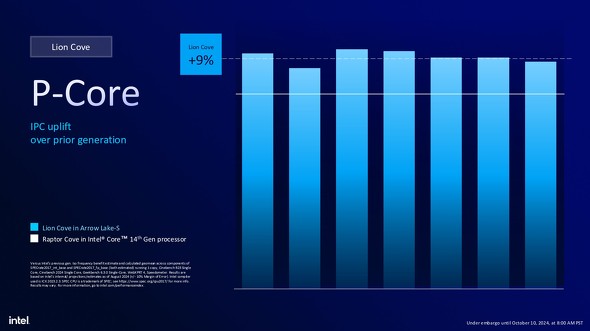

Pコアは、Core Ultra 200Vプロセッサで初搭載された「Lion Cove」(開発コード名)だ。つまり、ハイパースレッディング(同時マルチスレッド)機構は非搭載となる。

過去の拙著でも触れた通り、Lion Coveの平均IPC(クロックあたりの処理命令数)は非常に高い。ゆえに、ハイパースレッディングに対応したとしても、その投資(トランジスタ数や消費電力)に見合った性能を引き出すことは厳しい。

ハイパースレッディングは元々、CPUの余剰演算器を有効活用する目的で搭載されてきた。現在実行しているスレッドとは無関係なスレッドの処理に対応させることで、アイドル(非活用)状態になっている演算器や他の実行ユニットを稼働できることが、動作効率面で何よりも意義深かった。しかし、IPCが良好になったこもあり、昨今のPコアではハイパースレッディングに対応する意義が薄れている。

前も言ったが、最近のIntelは「これなら、ハイパースレッディングに対応させるコストをEコアの増量に回した方が全体性能が改善するんじゃね?」という設計信条を持っているようだ。

結局のところ、ハイパースレッディングでは「CPUコアが完全に“分身”する」わけではない。IntelがLion Coveに対して「ハイパースレッディングは載せない」と判断したのは、パフォーマンス向上という面では理にはかなっている。ただし、競合CPUに対してスレッド数が減った(≒パフォーマンスを発揮しづらい)ように見えるのは確かなので、既存ユーザーに対して丁寧な説明が必要になってくるだろう。

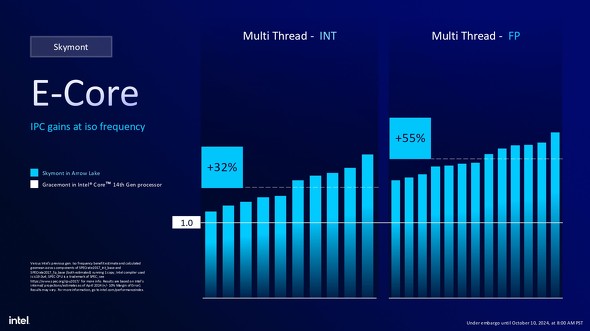

Eコアも、Core Ultra 200Vプロセッサと同じ「Skymont」(開発コード名)を搭載している。元々、Eコアにはハイパースレッディング機構は搭載されていないので、そのあたりの仕様変更はない。

しかし、Core Ultraプロセッサ(シリーズ1)のEコア「Cresmont」(開発コード名)と比べると、「浮動小数点演算/AVX系SIMD演算のパフォーマンス改善」「アウトオブオーダー実行の範囲拡大」など、CPUコアとしての基礎性能を高める措置が施されている。

この効果はてきめんなようだ。Intelによると、第13世代CoreプロセッサとCoreプロセッサ(14世代)のEコア「Gracemont」(開発コード名)と比較した場合、整数演算のパフォーマンスはシングルスレッド/マルチスレッドの双方で最大32%向上し、浮動小数点演算のパフォーマンスはシングルスレッドで最大72%、マルチスレッドで最大55%向上したという。筆者としては「『Eコア』という呼び方で損をしている」という印象を持った。

このLion CoveとSkymontについての深い解説は、いずれ回を改めて行いたいと考えている。

タスク振り分けが一層洗練された「Intel Thread Director」

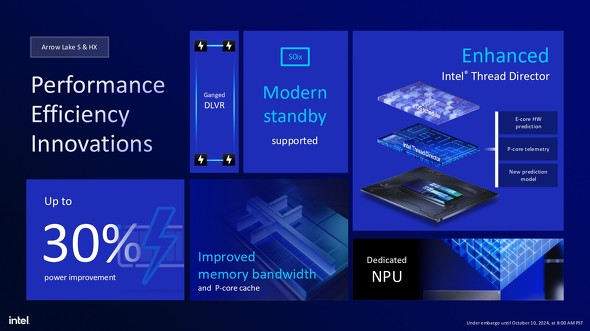

Arrow Lakeでは、CPUのキャッシュメモリの階層構造に大きな変革はない。ただ、着実かつ順当な強化はなされている。

全てのCPUコアで共有するL3キャッシュの容量は最大36MBとなる。これは第13世代CoreプロセッサとCoreプロセッサ(14世代)から変わりない。

L2キャッシュについては、Pコアでは1コアあたり3MBに増強された。これは第13世代CoreプロセッサとCoreプロセッサ(14世代)におけるPコアの1.5倍の容量だ。Eコアは4基あたり4MBのL2キャッシュを共有する設計で、第13世代CoreプロセッサとCoreプロセッサ(14世代)と同じだ。

PコアのL2キャッシュを増量した理由はシンプルで、比較的長いループを回るスレッドの実行を担当する機会が多いからだ。L2キャッシュの強化(増量)は、メモリへのアクセスを低減させ、シングルスレッドの性能向上に直結する。

スレッド(ワークロード)をPコアとEコアに振り分ける「Intel Thread Director」は、第13世代CoreプロセッサとCoreプロセッサ(14世代)はもちろん、Core Ultraプロセッサ(シリーズ1)やCore Ultra 200Vプロセッサとも少し異なるアルゴリズムで動作するという。

まずEコアだが、従来の第13世代CoreプロセッサとCoreプロセッサ(14世代)の場合は「平均IPCがどのくらい出ているか?」ということだけを基準とするシンプルなアルゴリズムでスレッドの割り振りを行っていた。

それに対して、Arrow Lakeでは従来のPコアに近い精度のテレメトリーベースの割り当てが適用される。つまり、例えば「どのアドレス範囲のスレッドを、どのくらいの稼働率で、どのくらいの時間動かしたか」「どんな種別の命令が実行されたのか」「CPUキャッシュのヒット率はいかほどか」といった情報を蓄積し、Eコアに継続して従事させるのか、あるいはスレッドを別コアに割り当て直すのか、といった判断を行う。ここで言う「別コア」には、Pコアだけでなく、別クラスタにあるEコアも含まれる。

Pコアにおけるスレッド割り振りは、従来通りテレメトリーベースのアルゴリズムで行われる。ただし、高いシングルスレッド性能が要求される場合は、なるべくPコアに集中してスレッドを割り当てるように振る舞うという。

これらのスレッド割り当ては、ニューラルネットワークベースの予測メカニズムを採用しているとのことで、「このスレッドはどのコアに割り当てるべきか?」の予測精度が劇的に向上したとIntelは説明している。

Arrow Lakeには、ハイパースレッディング機構がない。とはいえ、マルチコアCPUであることには変わりなく、マルチスレッド処理には対応している。当然、OSレベルが行うコンテキストスイッチングも普通に対応している。

Core Ultra 200S/200HXプロセッサは、ゲーミングPCでの採用が多くなると思われる。その際に、ゲームのメインスレッドを動作させているPコアを、不用意かつ高頻度にプリエンプションさせて別スレッドを割り当ててしまっては、ユーザーのためにならない。

Intelは、Arrow LakeのThread Directorを「適材適所」ならぬ、よりレベルの高い「適スレッド/適コア」となるように予測モデルをさらに賢いものに仕立てた――そう考えると、今回の機能拡張がイメージしやすいだろう。

関連記事

IntelがNPUを統合したデスクトップ向け「Core Ultra 200Sプロセッサ」を発表 アンロック版は米国で10月24日発売

IntelがNPUを統合したデスクトップ向け「Core Ultra 200Sプロセッサ」を発表 アンロック版は米国で10月24日発売

Intelの「Core Ultraプロセッサ」に、デスクトップ向けモデルがついに登場する。まずアンロック対応版が5製品発売される予定で、2025年第1四半期には同アーキテクチャを採用したモバイル向け製品もお目見えする予定だ。 「Core Ultraプロセッサ(シリーズ2)」は驚きの内蔵GPU性能に メモリ帯域が当初発表から“倍増”

「Core Ultraプロセッサ(シリーズ2)」は驚きの内蔵GPU性能に メモリ帯域が当初発表から“倍増”

IntelがLuna Lakeこと「Core Ultra 200Vプロセッサ」を発表した。Core Ultraプロセッサ(シリーズ2)のモバイル向けモデルという位置付けだが、どのような特徴があるのだろうか。ドイツ・ベルリンで開催された発表会で得られた情報をもとにまとめた。 Intelのモバイル向け次世代CPU「Lunar Lake」は2024年第3四半期に登場 ライバルを超えるAI処理パフォーマンスを実現

Intelのモバイル向け次世代CPU「Lunar Lake」は2024年第3四半期に登場 ライバルを超えるAI処理パフォーマンスを実現

Intelが、モバイル向け次世代CPU「Lunar Lake」の概要を発表した。2024年第3四半期に登場する予定で、ライバルCPU/SoCよりも高速なAIパフォーマンスを発揮できることが特徴だ。 「AI PC」がベールを脱ぐ! 次世代のモバイル向け「Core Ultraプロセッサ」正式発表 搭載ノートPCは順次発売

「AI PC」がベールを脱ぐ! 次世代のモバイル向け「Core Ultraプロセッサ」正式発表 搭載ノートPCは順次発売

Intelが発表を予告していた「Core Ultraプロセッサ」が、ついに正式発表された。全てのモデルにAIプロセッサ(NPU)を搭載しており、NPUを利用できるアプリのパフォーマンスが大きく向上することが特徴だ。 Intelが次世代CPU「Meteor Lake」の概要をチラ見せ 全モデルに「AIエンジン」を搭載

Intelが次世代CPU「Meteor Lake」の概要をチラ見せ 全モデルに「AIエンジン」を搭載

Intelが「Meteor Lake(メテオレイク)」というコード名で開発を進めているCPUの概要情報を公開した。同社初の7nmプロセスCPUは、全モデルにCPUコアとは別体の「AIエンジン」を搭載するという。

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- 10万円切りMacが17年ぶりに復活! 実機を試して分かったAppleが仕掛ける「MacBook Neo」の実力 (2026年03月10日)

- きょう発売の「MacBook Neo」、もうAmazonで割安に (2026年03月11日)

- 「MacBook Neo」を試して分かった10万円切りの衝撃! ただの“安いMac”ではなく絶妙な引き算で生まれた1台 (2026年03月10日)

- セールで買った日本HPの約990gノートPC「Pavilion Aero 13-bg」が想像以上に良かったので紹介したい (2026年03月11日)

- 新型「MacBook Air」はM5搭載で何が変わった? 同じM5の「14インチMacBook Pro」と比べて分かったこと (2026年03月10日)

- 12機能を凝縮したモニタースタンド型の「Anker 675 USB-C ドッキングステーション」が27%オフの2万3990円に (2026年03月11日)

- リュック1つで展示会セミナーの音響セット構築レポ 現場で得た“2.4GHz帯混信地獄”を生き抜く教訓 (2026年03月11日)

- エンスージアスト向けCPU「Core Ultra 200S Plus」登場 Eコア増量+メモリアクセス高速化+バイナリ最適化でパフォーマンス向上 (2026年03月11日)

- 最新Core Ultra X7 358Hの破壊力! 16型OLED搭載で内蔵GPUがディスクリート超え!? Copilot+ PC「Acer Swift 16 AI」レビュー (2026年03月10日)

- 出張や通勤で荷物が増えても安心な「ミレー ビジネスリュック EXP NX 20+」が27%オフの1万3865円に (2026年03月10日)