Intelの最新CPUを支えるテスターはロボと人力! マレーシアのキャンパスで行われていること:大人の社会科見学(1/4 ページ)

8月下旬、Intelは半導体関連を中心とする世界中のメディアをマレーシアに集め、同社のCPUの製造拠点である「ペナンキャンパス」と「クリムキャンパス」を公開するイベント「Intel Tech Tour.MY」を開催した。

この記事では、CPUの量産に欠かせない、両キャンパスにおける“支援技術”に目を向けようと思う。本記事をより深く理解するには、以前に掲載したCPUの“作られ方”の記事を先に読むことをお勧めする。

なお、本記事についても工場内部の撮影は原則禁止だったため、特記のない写真と動画は、全てIntelが提供したものを利用している。

マレーシアで試作CPUのテストも行っテル!

ペナンキャンパスには「Intel Maylasia Design and Development Lab(通称:MDC MEGA LAB)」が設置されている。ここでは、量産前/開発中のCPUの動作検証と、量産を進めるための基礎技術開発などを担っており、その役割から通常は社外に公開されることはあり得ない。しかし、今回のツアーでは、幸運にもこのセクションも公開され、見学することができた。

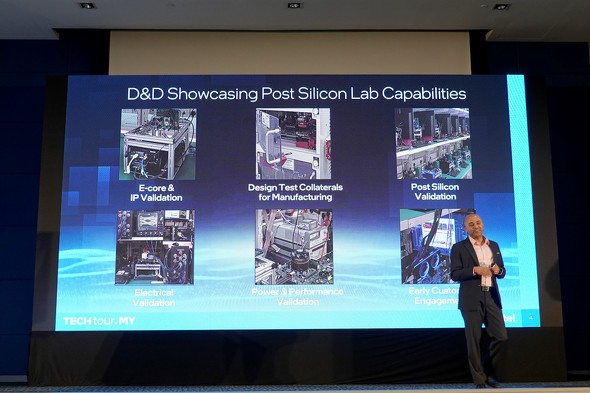

上の写真にもある通り、今回はこのMDC MEGA LABのうち、6つのセクションを見学する機会を得た。写真と動画を使って、その内容をじっくりと紹介していく。実際の見学順路とは少し異なるが、分かりやすくするためにスライドの左上から右下に向かって順に見ていこう。

E-Core and IP Validation

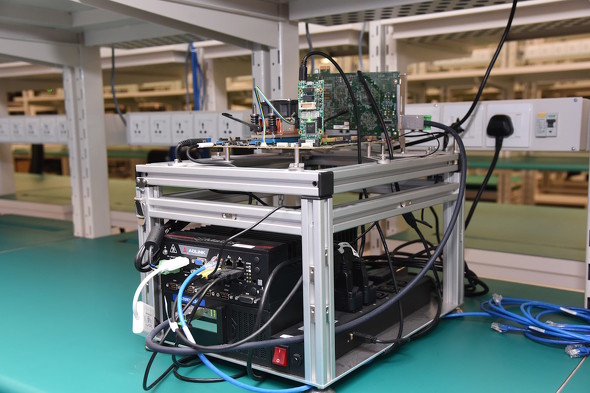

「E-Core and IP Validation」は、第12世代Coreプロセッサ(開発コード名:Alder Lake)から実装されるようになった「高効率コア(Eコア)」の検証を主に行うセクションとなる。

ご存じの通り、第12世代以降のCoreプロセッサでは、シングルコアの処理性能を重視する「パフォーマンスコア(Pコア)」と、バックグラウンド処理や各種入出力(I/O)処理に必要十分な性能を持つ、低消費電力重視の「高効率コア(Eコア)」を混在させるアーキテクチャを採用している。

見学時は、このコーナーでは12月に正式発表される予定の「Core Ultraプロセッサ」(開発コード名:Meteor Lake)のEコアの負荷試験を行うテスト機材が公開されていた。

Design Test Collaterals for Manufacturing

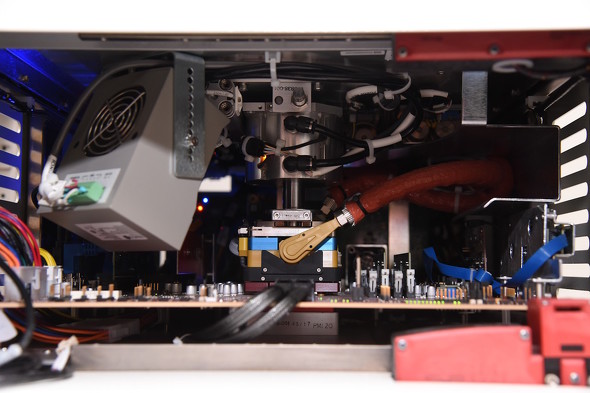

「Design Test Collaterals for Manufacturing」セクションは、CPU製品の量産ラインに組み込まれるテスト機材の開発を担っている。ここで開発された機材や技術は、前編で紹介した量産ラインに組み込まれていくという。

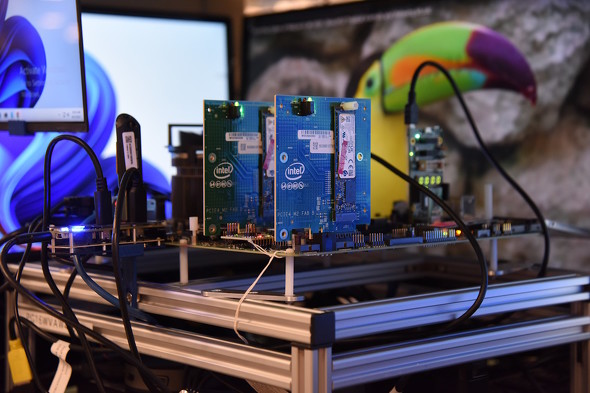

Post Silicon Validation

「Post Silicon Validation」は、CPUの試作品や量産テスト品が完成した際に行われるテスト工程だ。テストの内容は、前編で出てきた「PPV(Platform Performance Validation)」に近く、実動OS上で実際の周辺機器たちと組み合わせてテストが行われる。違いとしては、工程が完全に自動化されていないことで、人(作業員)の介入が多い。

ここで得られた知見は、量産ラインにおけるPPVに反映されるケースも多いと思われる。

各種実験工程は、まだまだ続く。

関連記事

CPUの型番はいつ決まる? どうやって決める? Intel最新CPUの作り方、みんなに見せちゃいます!

CPUの型番はいつ決まる? どうやって決める? Intel最新CPUの作り方、みんなに見せちゃいます!

IntelのCPUの多くは、マレーシアにある工場で作られている。同国で開催された報道関係者向けのイベントにおいて、同社がCPUを作る過程を公開したので、ガッツリと紹介したいと思う。 Intelの次世代CPUは「Core Ultraプロセッサ」として12月14日(米国太平洋時間)に正式発表

Intelの次世代CPUは「Core Ultraプロセッサ」として12月14日(米国太平洋時間)に正式発表

Intelが「Meteor Lake」として開発を進めてきた次世代CPUを「Core Ultraプロセッサ」として販売することを正式に発表した。詳細なスペック、ラインアップなどは12月14日(米国太平洋時間)に明らかとなる。 「Meteor Lake」はCPUコアが3種類!? Intelが次世代CPUの詳細を発表(前編)

「Meteor Lake」はCPUコアが3種類!? Intelが次世代CPUの詳細を発表(前編)

Intelが、次世代CPUとして2023年末に正式発表する予定の「Meteor Lake」のアーキテクチャ面での詳細を発表した。この記事では、CPUコアを備える「Compute Tile」と、高度な機能を複数搭載する「SoC Tile」にある“謎の新要素”について詳説する。 半導体生産で「委託」「受託」を両にらみ Intelが「IDM 2.0」構想を発表

半導体生産で「委託」「受託」を両にらみ Intelが「IDM 2.0」構想を発表

Intelが、新しい半導体生産方針「IDM 2.0」を発表した。自社生産を基本とする方針は堅持しつつ、ファウンドリーを活用した製品生産を拡大し、自らがファウンドリーとして生産を受託する事業も開始する。 Intel、GPUステータス計測ツール「PresentMon」β版を公開

Intel、GPUステータス計測ツール「PresentMon」β版を公開

米Intelは、GPUステータス計測ツール「PresentMon」β版の公開を開始した。

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- 「ANAオリジナル タフなビジネスリュック」を試す 収納力もバツグンで鳥肌が立つほどにカッコいい (2026年04月07日)

- レノボが「ThinkPad」2026年モデルを一挙発表! 12年ぶりの構造刷新やUSB Type-Cの自力交換対応でメンテナンス性も向上 (2026年04月07日)

- GoogleのAシリーズ最新作「Pixel 10a」は7万9900円から カメラの出っ張りが消えて新色も追加 (2026年04月07日)

- 「Google Pixel 10a」に日本限定カラー登場! ヘラルボニーとのコラボで多様性を表現する特別な「Isai Blue」(異彩青) (2026年04月07日)

- ANAがビジネスユースに特化した耐久性重視のビジネスバッグ3製品を発売 (2025年11月14日)

- 待望の「Core Ultra 7 270K Plus」は静かな船出――アキバでは激安ピラーレスケースなど“高コスパ”パーツに熱視線 (2026年04月06日)

- Googleが最新オープンAIモデル「Gemma 4」を公開 (2026年04月06日)

- FCCLがこだわりのキーボード「FMV Keyboard X」をクラファン形式で販売 約2.3万円から (2026年04月07日)

- NVIDIAが「G-SYNC Pulsar」対応ディスプレイを日本初披露 何がすごい? (2026年04月06日)

- 迷走の5年間を経て――MicrosoftがWindows 11の“不都合な真実”を認め、改善を宣言した背景 (2026年04月01日)