次世代の「Core Ultraプロセッサ」に採用! リアルタイムレイトレに対応したIntel内蔵GPUの“秘密”に迫る:Intel Innovation 2023(2/6 ページ)

Core Ultraプロセッサの内蔵GPUを深掘り!

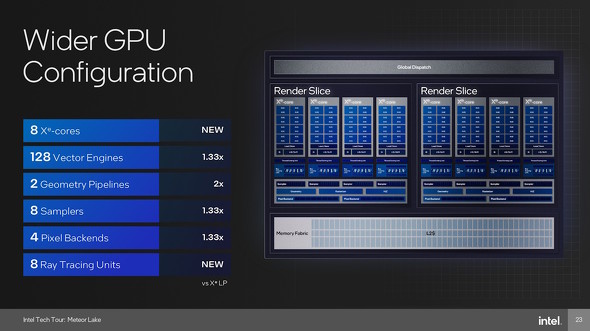

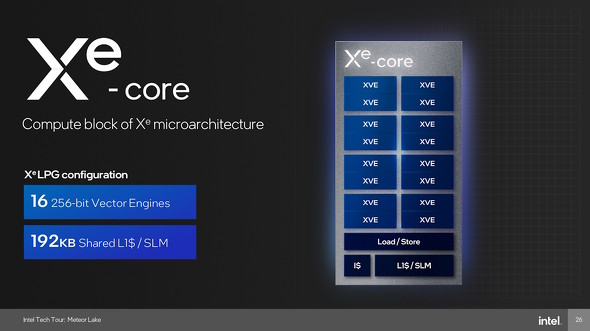

Core Ultraプロセッサは、Xe-LPGアーキテクチャを採用するGPUを搭載する“初号機”ということになる。そのブロックダイアグラム(構造図)を見てみると、「Render Slice」と呼ばれるGPUクラスターが2基あり、それぞれのRender Sliceには「Xe-Core」が4基内包されている。1基のXe-Coreには、合計16基(2基×8)の「XVE(Xe Vector Engine)」と呼ばれるベクトル演算エンジンが搭載されている。

各部位の名称を、NVIDIA製GPUと同等の呼び方に言い換えると以下の通りとなる。

- Render Slice≒GPC(Graphics Processing Cluster)

- Xe-Core≒SM(Streaming Mulitiprocessor)

- XVE≒CUDA(Compute Unified Device Architecture)コア

Render Sliceが2基構成という点は、ノートPC向けのエントリー独立GPU「Intel Arc A370M Graphics」と近い。恐らくは、実際の性能もArc A370Mが目安となるだろう。

ベクトル演算エンジンに改良

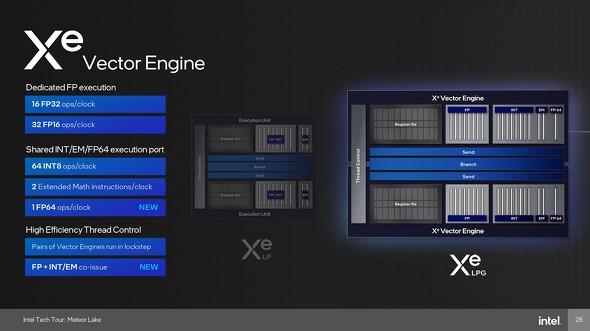

XVEの実態は、256bitの「SIMD浮動小数点ベクトル積和算演算器」だ。なので、XVE1基でFP32(32bit浮動小数点数)演算を行う場合、1命令で最大8つの演算を並行して行える。いわゆる「SIMD8」だ。

その見かけ上の仕様は、Xe-HPGアーキテクチャにおけるXVEと変わりない。しかし、Intel Graphics Product Teamのダミエン・トリオレット氏によると、He-LPGのXVEは2つの点でXe-HPGのそれを上回る仕様となっているという。

強化点の1つが、FP64(64bit倍精度浮動小数点)演算に対応したことだ。ただし、XVE全体で1クロック当たり1つの演算しかできないという制限がある。

もう1つが、「FP16(半精度浮動小数点数)またはFP32のSIMD演算」と「整数のSIMD演算または超越関数のスカラ演算」を同時実行できるようになったことだ。これにより、シェーダープログラムの実行効率が若干上がる。

後述する「DP4a命令」は、整数のSIMD演算に相当するので、FP16/FP32の浮動小数点演算と同時並列実行が可能となっている。

従来のXe-HPGアーキテクチャにはなかった「Out of Order Sampling」や、IntelのCPU内蔵GPUとしては初めて搭載される「リアルタイムレイトレーシング機能」についても見ていこう。

関連記事

Intel“逆襲”の鍵はやはり「AIプロセッサ」か 次世代CPU「Core Ultra(Meteor Lake)」を解説(後編)

Intel“逆襲”の鍵はやはり「AIプロセッサ」か 次世代CPU「Core Ultra(Meteor Lake)」を解説(後編)

Intelが「Meteor Lake」というコード名で開発してきたCPUを「Core Ultraプロセッサ」としてリリースすることを発表した。この記事では、SoC Tileに搭載されているNPUやディスプレイ/メディアエンジン、Graphics Tile(内蔵GPU)やI/O Tile(入出力インタフェース)について解説する。【訂正】 「Meteor Lake」はCPUコアが3種類!? Intelが次世代CPUの詳細を発表(前編)

「Meteor Lake」はCPUコアが3種類!? Intelが次世代CPUの詳細を発表(前編)

Intelが、次世代CPUとして2023年末に正式発表する予定の「Meteor Lake」のアーキテクチャ面での詳細を発表した。この記事では、CPUコアを備える「Compute Tile」と、高度な機能を複数搭載する「SoC Tile」にある“謎の新要素”について詳説する。 モバイル向けGPU「Intel Arc Aシリーズ」が発進 スペック別に3シリーズを順次投入

モバイル向けGPU「Intel Arc Aシリーズ」が発進 スペック別に3シリーズを順次投入

Intelが、モバイル向けGPU「Intel Arc Aシリーズ」を正式に発表した。米国ではエントリー製品を搭載するノートPCの受注が始まっており、4月から搭載製品が順次お披露目される見通しだ。 第11世代Coreプロセッサ(Tiger Lake)の性能は「PCメーカー次第」 どういうこと?

第11世代Coreプロセッサ(Tiger Lake)の性能は「PCメーカー次第」 どういうこと?

近いうちに搭載ノートPCが出る予定である「第11世代Coreプロセッサ」(開発コード名:Tiger Lake)。実は、同じCPUを搭載していても、メーカー(あるいはモデル)によって性能に差が生じる可能性があるという。どういうことなのだろうか。【画像差し替え】 Intelの最新CPUを支えるテスターはロボと人力! マレーシアのキャンパスで行われていること

Intelの最新CPUを支えるテスターはロボと人力! マレーシアのキャンパスで行われていること

IntelはマレーシアにCPUの開発/製造拠点を保有している。8月下旬、世界中の報道関係者を集めて見学イベントが行われたが、その際にCPUの開発や製造を支援するセクションも見学することができた。この記事では、その模様をお伝えする。

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- キーボード「FILCO」ブランドのダイヤテックが閉業 4月22日付で (2026年04月24日)

- 大型連休前のアキバは新CPUラッシュ! AMD「Ryzen 9 9950X3D2」とIntel「Core Ultra 5 250K Plus/KF Plus」の気になる在庫状況 (2026年04月25日)

- 持ち運びを極めた超軽量キーボード「ロジクール KEYS TO GO 2」が17%オフの9980円に (2026年04月23日)

- ACアダプター不要の外付けHDD「Seagate One Touch Desktop External Hard Drive」を試す 超大容量で配線スッキリ (2026年04月24日)

- Windows 11の使い勝手はどう変わる? 「Copilot」名称外しやInsider Program再編に見るMicrosoftの本気度 (2026年04月24日)

- 強力なドッキングステーション「Anker PowerExpand Elite 13-in-1 Thunderbolt 3 Dock」が28%オフの2万6490円に (2026年04月23日)

- Microsoftの「12インチSurface Pro」「13インチSurface Laptop」が一部販路で値上げ 直販では4万6200円増しに (2026年04月23日)

- 部屋の雰囲気を一瞬で変えられる「SwitchBot RGBIC フロアライト」が15%オフの7633円に (2026年04月24日)

- Microsoftの新日本語IME「Copilot Keyboard」が正式版に “お前を消す方法”で有名なキャラ「カイル」も追加 (2026年04月23日)

- 「Apple AirPods 4」が20%オフの2万3798円に (2026年04月24日)