大解説! “Broadwell-Y”な「Core M」はここがすごい(前編):14ナノメートル導入のメリットとは(2/2 ページ)

“フィン”で差をつけるインテルの技術力

Intelでプロセス技術の開発を担当するIntel ロジックテクノロジー部門 シニアフェローのマーク・ボア氏は、14ナノメートルプロセスルールは最終検証段階を終えて量産段階に入ったことを明らかにした。

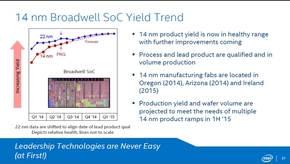

また、「その歩留まり(良品の採れる割合)は22ナノメートルプロセスルールの立ち上げより劣っているものの、14ナノメートルプロセスルールが本格的に立ち上がる2015年半ばには、現行の22ナノメートルプロセスルールと同等の歩留まりを実現できる目処がたった」とし、開発が順調に進んでいることをアピールする。

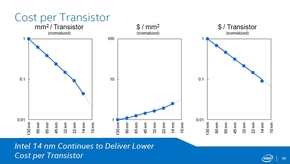

また、「14ナノメートルプロセスルールの製造コストは、これまでよりも高価になるが、当初の計画よりも高密度化できたため、トランジスタあたりの製造コストはこれまでのどのプロセスよりも良好だ」と語る。これにより、Intelは半導体プロセス技術の進化による微細化のペースを保ち、同じトランジスタ数であれば、約半分のダイサイズにできるようにし、「半導体の集積密度は18〜24カ月で倍増する」とするムーアの法則を堅持することができることになる。

14ナノメートルプロセスルールの面積あたり製造コストは従来よりも高めだが、高密度化が進んだことで、トランジスタあたりの製造コストはこれまでより安くなる(写真=左)。14ナノメートルプロセスルールの歩留まりは22ナノメートルプロセスルール立ち上げ時よりは劣っているものの、14ナノメートルプロセスルールが本格的に立ち上がる2015年半ばには、22ナノメートルプロセスルールと同等の歩留まりを実現できるという(写真=右)

14ナノメートルプロセスルールの面積あたり製造コストは従来よりも高めだが、高密度化が進んだことで、トランジスタあたりの製造コストはこれまでより安くなる(写真=左)。14ナノメートルプロセスルールの歩留まりは22ナノメートルプロセスルール立ち上げ時よりは劣っているものの、14ナノメートルプロセスルールが本格的に立ち上がる2015年半ばには、22ナノメートルプロセスルールと同等の歩留まりを実現できるという(写真=右)

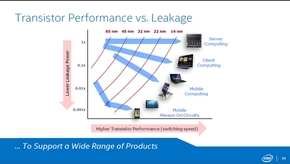

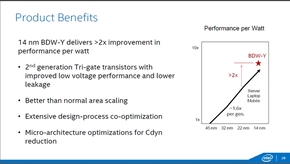

14ナノメートルプロセスは、リーク電流を低減しただけでなく、より高クロックで動作するCPUも実現できる(写真=左)。これまでIntelのCPUは世代交代ごとに約1.6倍ほど消費電力あたりのパフォーマンス向上を果たしてきた。これに対し、“Broadwell-Y”ことCore Mプロセッサでは、14ナノメートルプロセスルールと半導体設計の最適化などで、2倍以上の消費電力あたりのパフォーマンス向上を果たすという(写真=右)

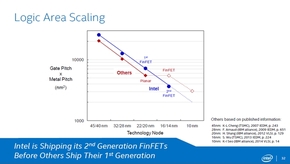

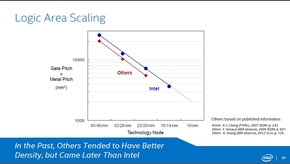

14ナノメートルプロセスは、リーク電流を低減しただけでなく、より高クロックで動作するCPUも実現できる(写真=左)。これまでIntelのCPUは世代交代ごとに約1.6倍ほど消費電力あたりのパフォーマンス向上を果たしてきた。これに対し、“Broadwell-Y”ことCore Mプロセッサでは、14ナノメートルプロセスルールと半導体設計の最適化などで、2倍以上の消費電力あたりのパフォーマンス向上を果たすという(写真=右)ボア氏は「TSMCやIBMといった競合他社は、われわれよりもプロセス進化が遅れている分、微細化と高密度化でアドバンテージを保ってきたが、現在開発中のFinFET(Fin Field Effec Transistor:Intelのトライゲートトランジスタ同様、フィン形状の立体トランジスタ技術の半導体業界における一般的な名称)プロセスは、われわれよりも3年以上遅れている上、高密度化においてもわれわれが優位に立つ」と、公開されている資料をもとに競合他社とのプロセス技術を比較を比較する。

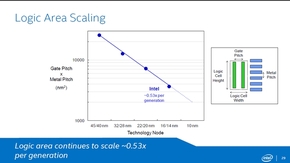

Intelの半導体製造プロセスでは、世代を進化させるごとにその回路規模を約53%に微細化し続けてきた(写真=左)。これに対し、TSMCなどの競合はプロセスの微細化ペースでIntelより遅れる分、より回路規模の小さなプロセス技術を実現してきた(写真=右)

Intelの半導体製造プロセスでは、世代を進化させるごとにその回路規模を約53%に微細化し続けてきた(写真=左)。これに対し、TSMCなどの競合はプロセスの微細化ペースでIntelより遅れる分、より回路規模の小さなプロセス技術を実現してきた(写真=右)関連記事

Intel、Broadwell世代の「Core M」概要を公開

Intel、Broadwell世代の「Core M」概要を公開

最初の搭載モデルは2014年のクリスマス商戦に登場する予定だ。 タブレットに注力するインテル、14nmプロセスの「Core M」も年内に出荷開始か

タブレットに注力するインテル、14nmプロセスの「Core M」も年内に出荷開始か

「COMPUTEX TAIPEI 2014」では、インテルによる基調講演が行われ、モバイル向けプロセッサ「Core M」などが発表された。Core Mは2014年後半に出荷される予定だという。講演にはFoxconnのYoung Liu氏も登壇し、「タブレット端末にはカスタマイズが必要になる」と強調した。 次世代のコンピューティングデバイスはどうなる?――Intel基調講演まとめ

次世代のコンピューティングデバイスはどうなる?――Intel基調講演まとめ

新たに14ナノプロセスルールを採用する低消費電力プロセッサ「Core M」が発表されたIntelの基調講演を振り返る。同社が考える次世代コンピューティングデバイス像とは。 Intelが新ブランド「Core M」を発表――Surface Pro 3より薄型軽量のリファレンスデザインも公開

Intelが新ブランド「Core M」を発表――Surface Pro 3より薄型軽量のリファレンスデザインも公開

Intelは6月3日、開催中の「COMPUTEX TAIPEI 2014」にて、開発コード名「Broadwell」で知られる次世代Coreプロセッサーのうち、低消費電力モバイル向け製品のブランド名を「Core M」に決定したと発表。 大解説! 次期CPUに対応する新世代“冷却”事情

大解説! 次期CPUに対応する新世代“冷却”事情

“Devil's Canyon”“Broadwell”では、従来の冷却機構が対応できないという。次期CPUに向けたクーラーユニット、PCケース、電源ユニットの動きを解説する。 大復習! Haswell RefreshからDevil's Canyon、Intel 9シリーズチップセットを整理する

大復習! Haswell RefreshからDevil's Canyon、Intel 9シリーズチップセットを整理する

“新しい”第4世代Coreプロセッサー・ファミリーとチップセットは、これまでと何が違うのか? 期待の“アンロック”なCPUとともにおさらいしておこう。 米Intelがファンレス仕様の新型NUCを発表、“Broadwell”ベースNUCの投入計画も

米Intelがファンレス仕様の新型NUCを発表、“Broadwell”ベースNUCの投入計画も

米Intelのパートナー向け会議でBay Trailベースの新型NUCが披露されるとともに、14ナノメートルプロセスを採用するBroadwellベースのNUCについても投入計画を明らかにした。 2014年は「デスクトップPCの再発明」――Intelの最新ロードマップをまとめてみた

2014年は「デスクトップPCの再発明」――Intelの最新ロードマップをまとめてみた

GDCにあわせてIntelがデスクトップ向けCPUの最新ロードマップを公開。2014年のCPU計画を「デスクトップPCの再発明」と定義する。BroadwellやIntel X99の情報もアップデート。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- 発表時の批判は裏返る? スペック据え置きでも“買い”と言える、極上の普段着スマホ「Pixel 10a」を触ってみた (2026年04月27日)

- サイボウズの社名由来 “坊主”に込められた意味が深すぎる (2016年07月29日)

- キーボード「FILCO」ブランドのダイヤテックが閉業 4月22日付で (2026年04月24日)

- マザーボードは「細部まで白」が今の主流? 高コスパ水冷など見逃せない最新自作PCパーツ事情 (2026年04月27日)

- 大型連休前のアキバは新CPUラッシュ! AMD「Ryzen 9 9950X3D2」とIntel「Core Ultra 5 250K Plus/KF Plus」の気になる在庫状況 (2026年04月25日)

- 次期「DaVinci Resolve 21」で写真編集が可能に/Google Cloudが第8世代TPUを発表 (2026年04月26日)

- エレコム、士郎正宗デザインマウス「M.A.P.P.」復刻モデルの予約販売を4月6日に開始 (2026年03月25日)

- エレコム、「士郎正宗 復刻マウス」発売日を延期 5月下旬の予定に (2026年04月27日)

- 持ち運びを極めた超軽量キーボード「ロジクール KEYS TO GO 2」が17%オフの9980円に (2026年04月23日)

- 部屋の雰囲気を一瞬で変えられる「SwitchBot RGBIC フロアライト」が15%オフの7633円に (2026年04月24日)