ついに! ようやく? 「Intel Maxシリーズ」2023年1月から出荷 HBM付き「Xeon Max」と高密度実装GPU「Intel GPU Max」(3/3 ページ)

究極の目標は「XPU」

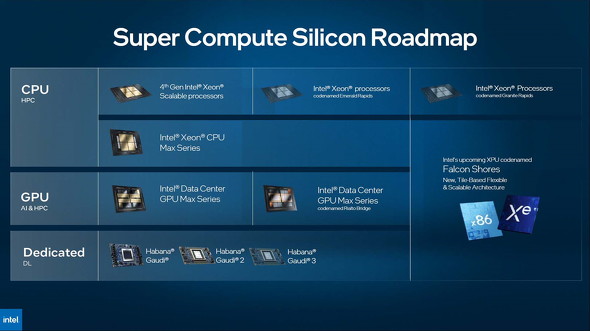

今回の発表に合わせて、Intelは今後のHPC/AI処理用のCPUとGPUのロードマップを“チラ見せ”している。その概要を紹介する。

CPU

CPUについては、今回登場したXeon MaxからHBM2を省略した「第4世代Xeonスケーラブルプロセッサ」が近いうちに登場するようだ。その後、Sappire Rapidsの改良版である「Emerald Rapids」(開発コード名)を投入し、プロセスルールを10nmから7nm(Intel 3)に微細化した「Granite Rapids」(同)をリリースする予定となっている。

ただし、Intelの図表をよく見てみると、Emerald Rapidsの世代にHBMメモリを統合するCPUはないようで、Granite Rapidsと同世代となる新型のXPUがその任を担うことになりそうである。

GPU

GPUについては、今回登場したIntel Data Center GPU Maxを改良した「Rialto Bridge」(開発コード名)が2024年に登場する予定となっている。Rialto Bridgeはデータセンターでの利用を想定した機能強化が行われる予定で、以下の特徴を備えているという。

- 消費電力は最大800Wに(液冷モデルもあり)

- Xeコア/RTコアは最大160基に

- フォームファクターはPonte Vecchioと同様(Subsystemも流用可能)

XPU

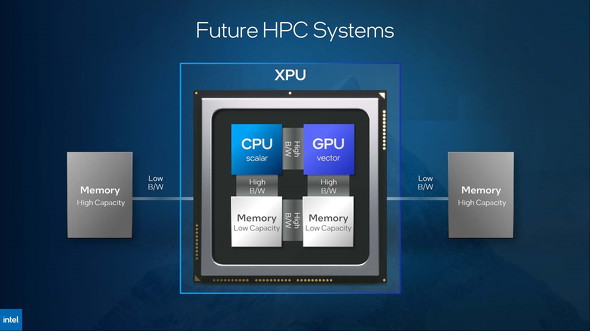

Intelは、CPU、GPU、NPU(AIアクセラレーター)を統合した「XPU」という半導体の開発を計画している。その第1弾として登場するのが「Falcon Shores」(開発コード名)だ。

Falcon ShoresはHPC/AI処理に耐えうるCPU、GPU、NPUを「x86プロセッサのソケットに収まるサイズ」で実現するもので、メモリの容量と帯域をしっかりと確保した上で、消費電力当たりのパフォーマンスにも優れているという。また、Intelが推進している「IDM 2.0」に基づき生産される予定で、同社や他社が知的財産権を保有するオリジナル半導体(プロセッサ)も組み込めるフレキシブルさも備えている。

Intelとしては、将来のHPCやAI処理においてXPUを最有力視しているようだ。

関連記事

2種類のコアで「省電力」と「高パフォーマンス」を両立――Intelが「Alder Lake」の概要を公開 「Sapphire Rapids」にも新情報

2種類のコアで「省電力」と「高パフォーマンス」を両立――Intelが「Alder Lake」の概要を公開 「Sapphire Rapids」にも新情報

Intelが報道関係者に技術動向を説明するイベント「Intel Architecture Day 2021」を開催。このイベントでは、次世代のCoreプロセッサとして2021年秋に登場する予定の「Alder Lake」の概要が公開された。 Intelが「次世代Xeonプロセッサ(Sapphire Rapids)」をチラ見せ 広帯域メモリ内蔵バージョンを用意

Intelが「次世代Xeonプロセッサ(Sapphire Rapids)」をチラ見せ 広帯域メモリ内蔵バージョンを用意

スーパーコンピューターの世界的なイベント「ISC 2021」に合わせて、IntelがHPC(ハイパフォーマンスコンピューティング)に関する取り組みを発表した。その中で、次世代のXeonスケーラブルプロセッサ(開発コード名:Sapphire Rapids)にHBM(広帯域メモリ)を内蔵するバージョンが用意されることが明らかとなった。 IntelがPC向けCPU/GPUのロードマップを更新 「Raptor Lake」は2022年後半に

IntelがPC向けCPU/GPUのロードマップを更新 「Raptor Lake」は2022年後半に

Intelが投資家向けのイベントでCPU/GPUの最新ロードマップを公表した。第12世代Coreプロセッサの後継となる「Raptor Lake(ラプターレイク)」は2022年後半に登場するという。 JEDECが「HBM3」の仕様書を公開 転送速度は毎秒819GBに

JEDECが「HBM3」の仕様書を公開 転送速度は毎秒819GBに

メモリの規格を策定する業界団体であるJEDECは1月27日(米国東部時間)、次世代のメモリである「HBM3(High Bandwidth Memory 3)」の仕様書を公開した。 Intelがファウンドリ事業のイノベーション促進に向けて10億ドルの基金を設立 RISC-V団体にも加盟

Intelがファウンドリ事業のイノベーション促進に向けて10億ドルの基金を設立 RISC-V団体にも加盟

米Intelは、自社で運営するファウンドリ事業のイノベーション促進に向けて10億ドル(約1150億円)の基金を設立すると発表した。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- キーボード「FILCO」ブランドのダイヤテックが閉業 4月22日付で (2026年04月24日)

- 次期「DaVinci Resolve 21」で写真編集が可能に/Google Cloudが第8世代TPUを発表 (2026年04月26日)

- 大型連休前のアキバは新CPUラッシュ! AMD「Ryzen 9 9950X3D2」とIntel「Core Ultra 5 250K Plus/KF Plus」の気になる在庫状況 (2026年04月25日)

- 持ち運びを極めた超軽量キーボード「ロジクール KEYS TO GO 2」が17%オフの9980円に (2026年04月23日)

- ACアダプター不要の外付けHDD「Seagate One Touch Desktop External Hard Drive」を試す 超大容量で配線スッキリ (2026年04月24日)

- Windows 11の使い勝手はどう変わる? 「Copilot」名称外しやInsider Program再編に見るMicrosoftの本気度 (2026年04月24日)

- 「Apple AirPods 4」が20%オフの2万3798円に (2026年04月24日)

- 2026年版Surfaceはどうなる? 正面衝突を避けるMicrosoft、10万円切り「MacBook Neo」対抗への秘策はあるか (2026年04月21日)

- 部屋の雰囲気を一瞬で変えられる「SwitchBot RGBIC フロアライト」が15%オフの7633円に (2026年04月24日)

- 強力なドッキングステーション「Anker PowerExpand Elite 13-in-1 Thunderbolt 3 Dock」が28%オフの2万6490円に (2026年04月23日)